【第Ⅰ期题目 * 5】

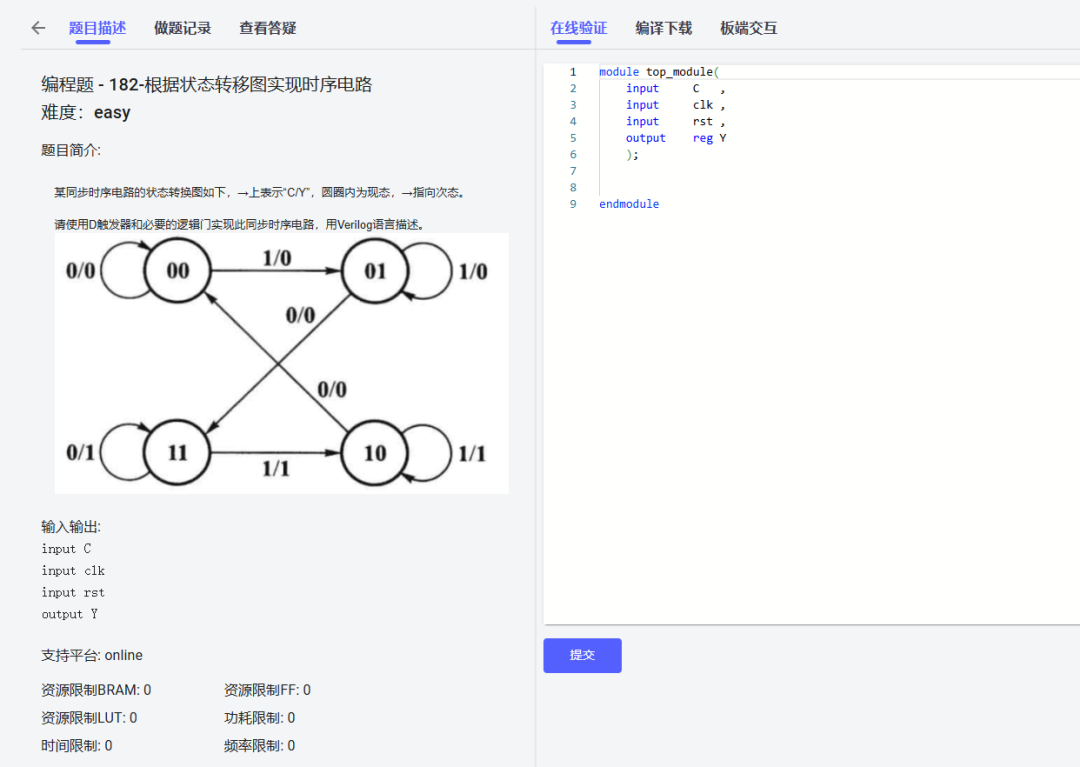

// 某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

【第Ⅰ期题目 * 4】

// 计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

请设计一个0-9的十进制计数器,要求带同步高电平复位功能。

【第Ⅰ期题目 * 3】

// 三人表决器,顾名思义就是三人投票,只要达到两票以上,就取胜。设a,b,c为三个投票的人,输出的为f,投为1,不投为0,两票以上为1,否则为0;

请参考以下真值表,实现三人表决器。

【第Ⅰ期题目 * 2】

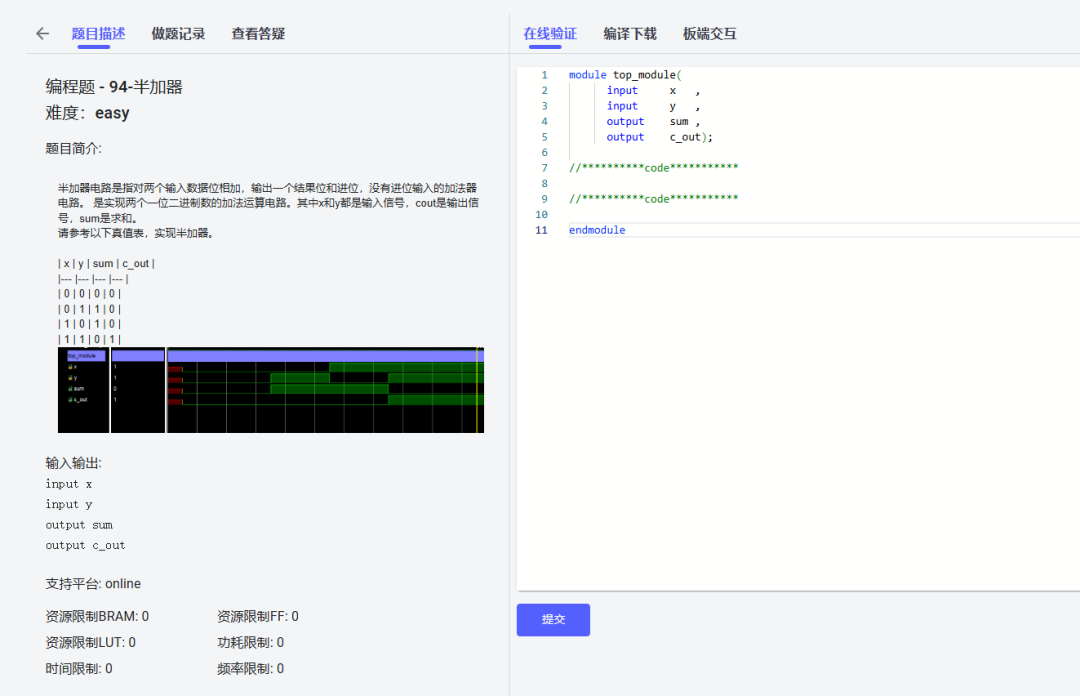

// 半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。是实现两个一位二进制数的加法运算电路。其中x和y都是输入信号,cout是输出信号,sum是求和。

请参考真值表,实现半加器。

【第Ⅰ期题目 * 1】

// 用verilog语言描述6个不同的2输入逻辑门电路,其中包括:与,或,与非,或非,异或和同或门。

题目练习传送门:F学社(www.zzfpga.com,pc端打开哦)

(ps,可灵活运用题目答疑区,提出你的疑问,届时,我们的工程师会统一进行解答~)

5176

5176

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?