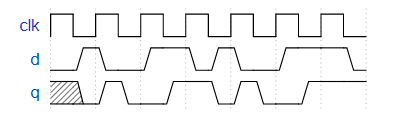

You're familiar with flip-flops that are triggered on the positive edge of the clock, or negative edge of the clock. A dual-edge triggered flip-flop is triggered on both edges of the clock. However, FPGAs don't have dual-edge triggered flip-flops, and always @(posedge clk or negedge clk) is not accepted as a legal sensitivity list.

Build a circuit that functionally behaves like a dual-edge triggered flip-flop:

(Note: It's not necessarily perfectly equivalent: The output of flip-flops have no glitches, but a larger combinational circuit that emulates this behaviour might. But we'll ignore this detail here.)

提交答案:

module top_module (

input clk,

input d,

output q

);

reg q_pos;

reg q_neg;

always @(posedge clk)

q_pos <= d;

always @(negedge clk)

q_neg <= d;

assign q = (q_pos & clk)|(q_neg & ~clk);

endmodule

solution

module top_module(

input clk,

input d,

output q);

reg p, n;

// A positive-edge triggered flip-flop

always @(posedge clk)

p <= d ^ n;

// A negative-edge triggered flip-flop

always @(negedge clk)

n <= d ^ p;

// Why does this work?

// After posedge clk, p changes to d^n. Thus q = (p^n) = (d^n^n) = d.

// After negedge clk, n changes to d^p. Thus q = (p^n) = (p^d^p) = d.

// At each (positive or negative) clock edge, p and n FFs alternately

// load a value that will cancel out the other and cause the new value of d to remain.

assign q = p ^ n;

// Can't synthesize this.

/*always @(posedge clk, negedge clk) begin

q <= d;

end*/

endmodule

846

846

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?