一、配置引脚详细说明

当然可以,我会根据您提供的信息和我所学习到的知识,对表格进行完善和修改。以下是更新后的表格:

| 引脚名称 | 功能描述 | 注意事项 |

|---|---|---|

| VCCBATT | FPGA内部易失性存储器的电池备用电源引脚 | - 用于存储AES解密器密钥。 |

| - 若不需要使用易失性密钥库中的解密密钥,则应将VCCBATT引脚连接至GND或VCCAUX。 | ||

| EMCCLK | 外部主配置时钟引脚 | - 使用EMCCLK引脚全速加载程序。 |

1.1 CFGBVS引脚功能介绍

CFPGBVS引脚用于确定或配置Bank0、Bank14、Bank15的电压

| 引脚 名称 | 所属Bank | 类型 | 方向 | 描述 |

|---|---|---|---|---|

| CFGBVS | 0 | 专用 | 输入 | 配置Banks电压选择 CFGBVS 引脚用于确定Bank 0(专用配置Bank) 的 I/O 电压工作范围和电压容限,并确定 AMD Spartan-7、AMD Artix-7 和 AMD Kintex-7 系列中 Bank 14 和 Bank 15 (多功能Bank)的电压选择。CFGBVS 在所有 7 系列设备中,始终选择专用 Bank 0 的工作电压。CFGBVS 仅在配置期间选择多功能配置 Bank 14 和 Bank 15 的工作电压。 根据 Bank 电压要求,将 CFGBVS 连接到高电平或低电平。如果 Bank 0 的 VCCO 电源为 2.5V 或 3.3V,则 CFGBVS 引脚必须接到高电平(即接到 VCCO_0)。如果 VCCO 0 小于等于 1.8V,则将 CFGBVS 连接到低电平(即接地)。如果在配置过程中使用,Bank 14 和 Bank 15 的电压应与应用于 Bank 0 的 VCCO 电平相匹配。 警告! 为避免损坏,CFGBVS 必须正确连接到 VCCO 或接地。参见《配置 Banks 电压选择》第 28 页了解更多信息。 注: CFGBVS 引脚不适用于 AMD Virtex-7 HT 设备。Virtex 7 HT 设备仅支持 Bank 0 使用 1.8V 操作。 |

1.2 Note

当VCCO0电压为2.5V或3.3V时,CFGBVS应连接至VCCO0。 若VCCO0电压为1.5V或1.8V,则CFGBVS应连接至GND。 建议将Bank0、Bank14、Bank15配置为相同的VCCO电压,以避免启动结束时的I/O转换问题。

2.1 M[2:0]功能引脚介绍

M[2:0] 引脚通过不同的组合来选择多种配置模式,包括 JTAG、主模式、从模式等。

| 引脚名称 | Bank | 类型 | 方向 | 说明 |

|---|---|---|---|---|

| M[2:0] | 0 | 专用 | 输入 | 配置模式:M[2:0]用于确定配置模式。有关配置模式的设置,请参见第19页的表格2-3。将每个模式引脚直接或通过≤1 kΩ的电阻,连接到VCCO_0或接地。 |

2.2 Note 1

| 配置模式 | M[2:0] | 总线宽度 | CCLK 方向 |

|---|---|---|---|

| 主串行 (Master Serial) | 000 | x1 | 输出 |

| 主 SPI (Master SPI) | 001 | x1, x2, x4 | 输出 |

| 主 BPI (Master BPI) | 010 | x8, x16 | 输出 |

| 主 SelectMAP (Master SelectMAP) | 100 | x8, x16 | 输出 |

| JTAG | 101 | 不适用 | 不适用 |

| 从 SelectMAP (Slave SelectMAP) | 110 | x8, x16, x32(1) | 输入 |

| 从串行 (Slave Serial)(2) | 111 | x1 | 输入 |

- Slave SelectMAP x16 和 x32 总线宽度不支持AES加密的配置流。

- 由于模式引脚上的内部上拉电阻,这是默认设置。

2.3 Note 2

是的,总线宽度(Bus Width)指的是在一次数据传输过程中总线上能够同时传输的数据位数。它表示数据通道的宽度,通常以“位”(bit)为单位。例如:

- x1 表示一次可以传输1位数据。

- x8 表示一次可以传输8位数据。

- x16 表示一次可以传输16位数据。

- x32 表示一次可以传输32位数据。

在FPGA的配置模式中,较宽的总线(例如x8或x16)可以加快配置的速度,因为它们能够在同一时间内传输更多的比特数据,而较窄的总线(如x1)则传输较少的数据位,速度相对较慢。

3.1 PUDC_B

PUDC_B(Pull-Up/Down Control B)引脚用于控制特定IO口的上拉或下拉电阻状态。

| 引脚名称 | Bank | 描述 |

|---|---|---|

| PUDC_B | 14 | 在上电和配置期间启用SelectlO引脚上的内部上拉电阻。 当PUDC_B为低电平时,每个SelectIO引脚上的内部上拉电阻被启用; 当PUDC_B为高电平时,每个SelectIO引脚上的内部上拉电阻被禁用; PUDC_B必须直接或通过≤1KΩ的电阻连接到VCCO_14或GND; 警告!在配置之前和配置器件,不要是这个脚悬空 |

3.2 Note

SelectIO是指Xilinx FPGA中的一组可编程的I/O引脚。这些引脚具有高度的灵活性和可配置性,可以被配置为各种不同的功能,包括但不限于:

- 通用输入/输出:作为标准的数字I/O。

- 专用功能:如高速差分信号对、LVDS(低压差分信号)、HSTL(高速度传输线)、LVCMOS(低电压CMOS)等。

在Xilinx的FPGA配置和设计中,SelectIO引脚的配置是通过硬件描述语言(如VHDL或Verilog)进行的,设计者可以根据需要选择适当的配置选项。

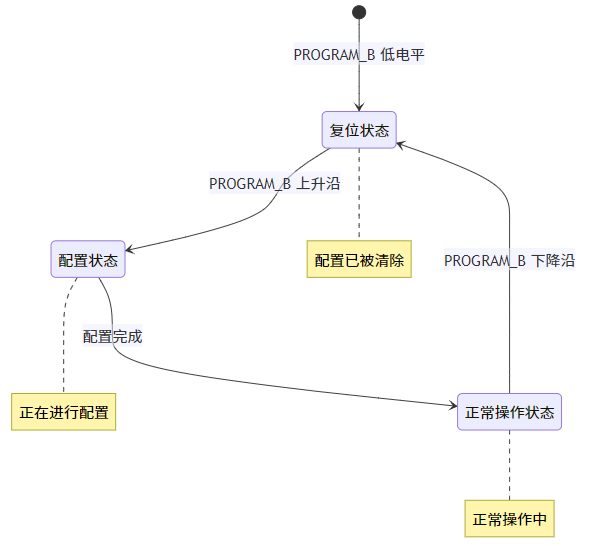

4.1 PROGRAM_B

PROGRAM_B是一个专用复位引脚,控制着FPGA是否接受新的配置数据。

| 引脚名称 | Bank | 专用功能 | 方向 | 说明 |

|---|---|---|---|---|

| PROGRAM_B | 0 | 专用 | 输入 | 该引脚用于主动低电平复位配置逻辑。当PROGRAM_B被拉低时,FPGA的配置会被清除,并开始新的配置过程。下降沿触发配置复位,配置(即编程)过程会在接下来的上升沿开始。 将PROGRAM_B通过一个≤ 4.7 kΩ的上拉电阻连接到VCCO_0,以确保稳定的高电平输入,建议使用接地的按钮来实现手动配置复位。 备注:在上电时保持PROGRAM_B为低电平并不会将FPGA配置保持在复位状态。应使用INIT_B来延迟上电时的配置过程。 |

4.2 Note

5.1 INT_B引脚功能介绍

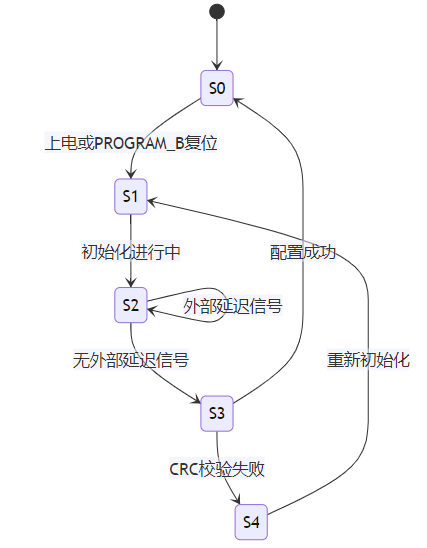

INIT_B引脚在FPGA配置过程中起着重要的作用,可以用来监控配置状态或用于调试和故障排除。

| 引脚 名称 | 所属Bank | 类型 | 描述 |

|---|---|---|---|

| INIT_B | 0 | 专用 | 可配置输入、输出、或开漏且; 外部可访问; 当FPGA处于配置复位状态、初始化(清除)其配置存储器(对应上电或PROGRAM复位),或在配置过程发生CRC错误时,FPGA会将INIT_B拉低为低电平。在完成FPGA初始化后,INIT_B会释放为高组态,此时需要外部电阻将INIT_B拉高。 在上电期间,INIT_B可以通过外部方式保持其低电平,以在初始化过程结束时暂停上电配置。当初始化过程结束后,在INIT_B引脚检测到高电平时,FPGA会根据M[2:0]引脚设置继续执行剩余的配置系列。 将INIT_B连接到一个≤4.7KΩ的上拉电阻,并连接到VCCO_0,以确保低到高电平的转换; |

5.2 Note

我们首先定义上电/复位状态为S0、初始化状态为S1、配置延迟为S2、配置完成为S3和CRC错误为S4。在S0状态下,系统等待初始化,当检测到上电或PROGRAM_B引脚复位信号时,系统进入初始化状态S1。在S1状态下,FPGA正在初始化配置存储器。若上电期间,INIT_B通过外部方式保持低电平,系统将进入配置延迟状态S2。配置过程结束后,如果配置过程中没有检测到CRC错误,系统从S2转移到配置完成状态S3;如果检测到CRC错误,则进入CRC错误状态S4。配置完成后,系统可以重新进入上电/复位状态S0,准备下一次配置。而在CRC错误状态下,系统通常会重新初始化,尝试重新配置,从而转移到状态S1。

6.1 DONE引脚介绍

DONE引脚是一个专用的配置完成指示引脚,当FPGA配置完成后,它会输出高电平信号。

| 功能 | Bank | 类型 | 方向 | 描述 |

|---|---|---|---|---|

| DONE | 0 | 专用 | 双向 | DONE引脚上的高电平信号表示配置过程已经完成。该DONE输出为开漏输出。 注意: DONE引脚内部有一个大约10千欧姆的上拉电阻。 对于DONE寄存器,没有设置或保持时间的要求。 这些特性,加上DonePipe寄存器的软件默认设置,使得不再需要DriveDONE驱动选项。 虽然不需要,但可以使用外部330欧姆的电阻电路,就像在以前的产品代中那样。 |

6.2 Note

在早期的FPGA产品中,为了确保DONE引脚信号的稳定性和可靠性,设计者通常会在外部电路中加入330欧姆的电阻。这种做法有助于防止信号在没有明确电平状态时发生浮动。然而,随着技术的发展,现代FPGA设计已经在内部集成了适当的上拉电阻,减少了对外部电阻的依赖。尽管如此,如果设计者希望保持与早期产品相同的电路设计,或者出于兼容性的考虑,仍然可以选择在外部电路中加入330欧姆的电阻。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?