目录

一、概述

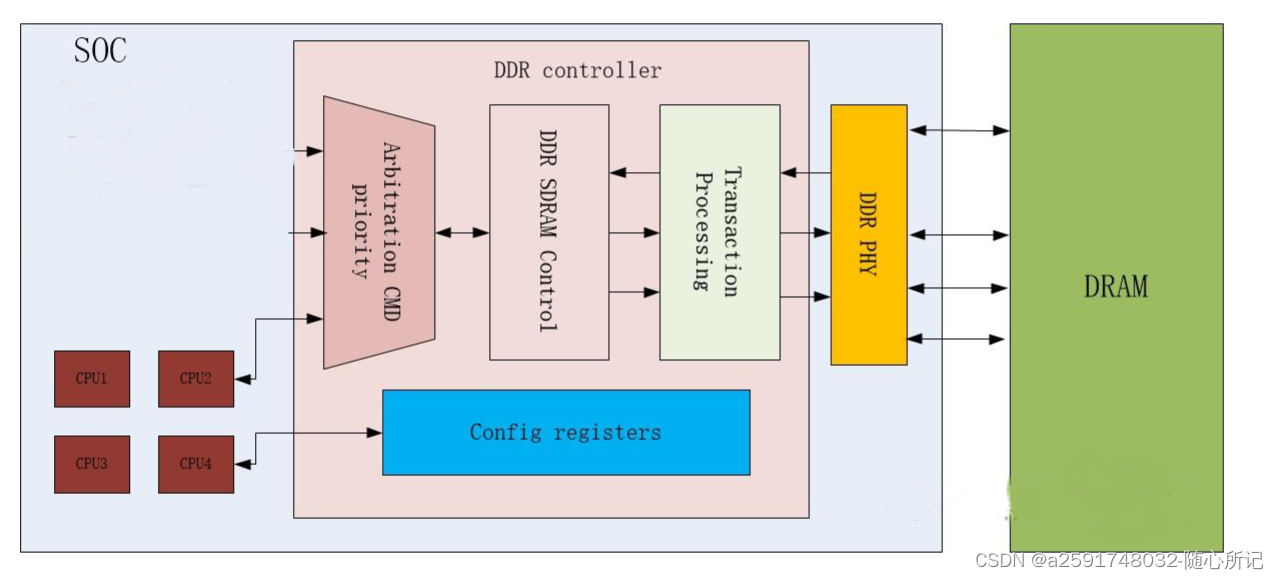

MCP(Multi-Chip Package)是一种多芯片封装技术,它将多个芯片封装在同一个封装体内,形成一个单一的组件。本文所介绍的mcp是flash和ddr的合体,当前主流的厂商将flash与DDR封装到一颗soc内来实现存储和内存运行。

二、MCP整体介绍

2.1 MCP系统框图

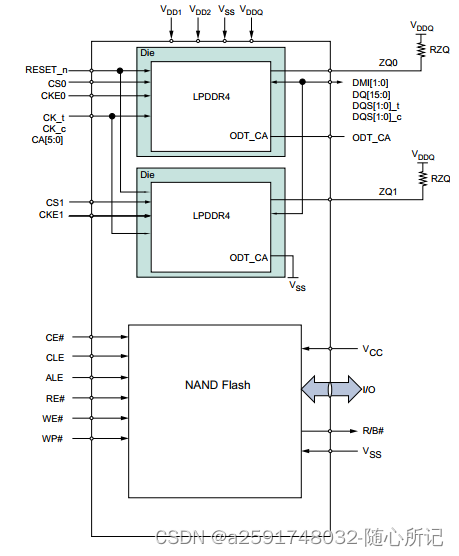

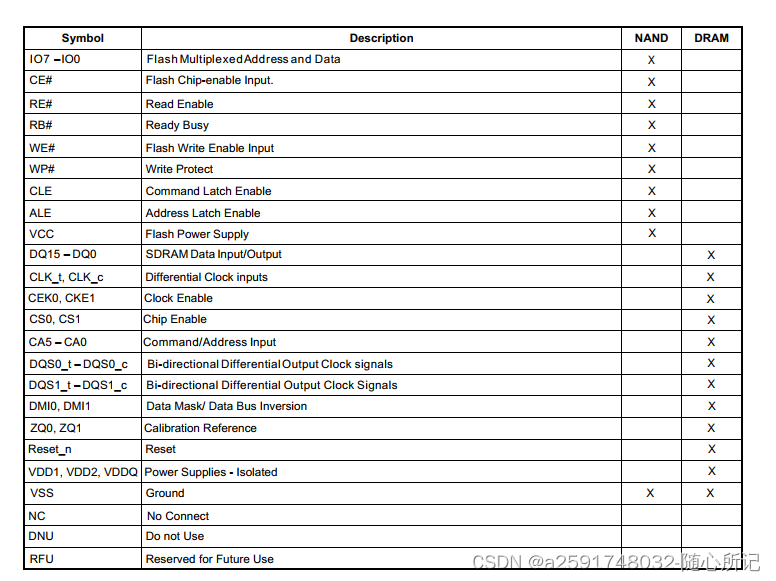

2.2 MCP物理信号

如2.1章节中的系统框图,nand flash接口是由IO0~IO7 8位并行口,以及CE、CLE、ALE、RE#、WE#、WP#,每个引脚的功能描述见下述图表。下表图中除nand flash接口外的其他信号是DDR的,详见下述图表。

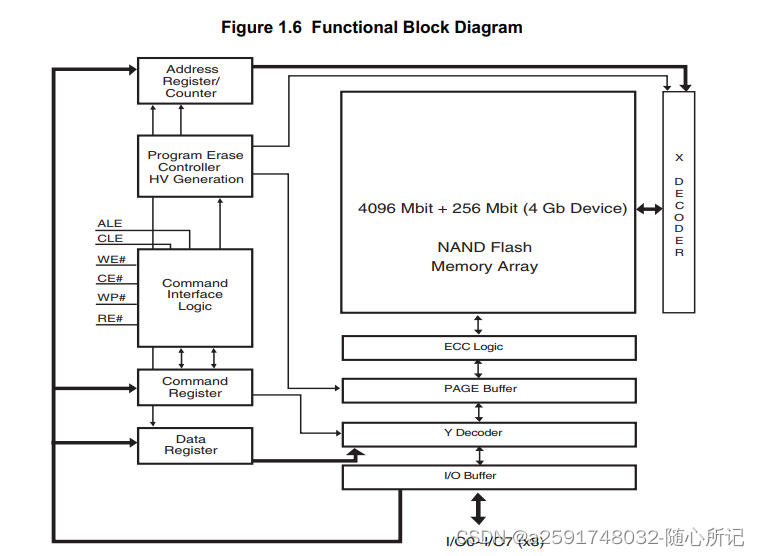

三、nand flash介绍

3.1 nand flash芯片系统框图

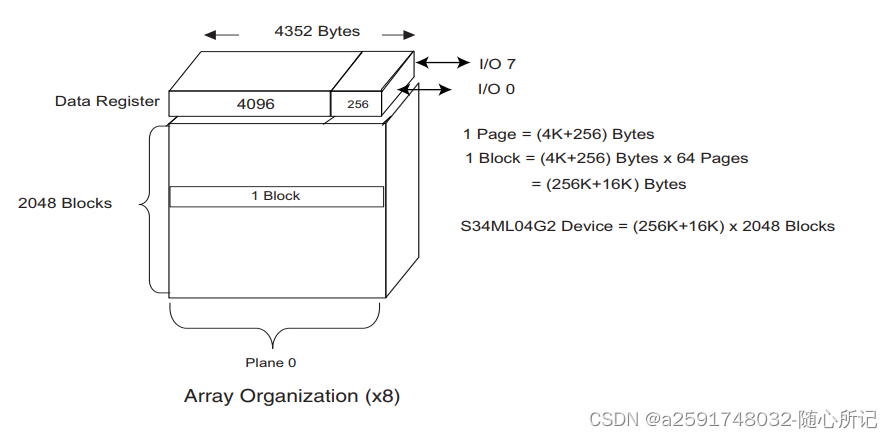

3.2 nand flash 存储数据结构

每个Nand包含一个或多个Chip。Chip是可以独立执行命令并上报状态的最小单元;

每个Chip包含一个或多个plane。不同的plane间可以并发操作,不过有一些限制;

每个plane包含多block,block是最小擦除单元(擦除后为全1,擦除失败则判定为坏块);

每个block包含多个page+obb, page是最小的读写单元,obb区存储校验数据、标记坏块、映射信息等。

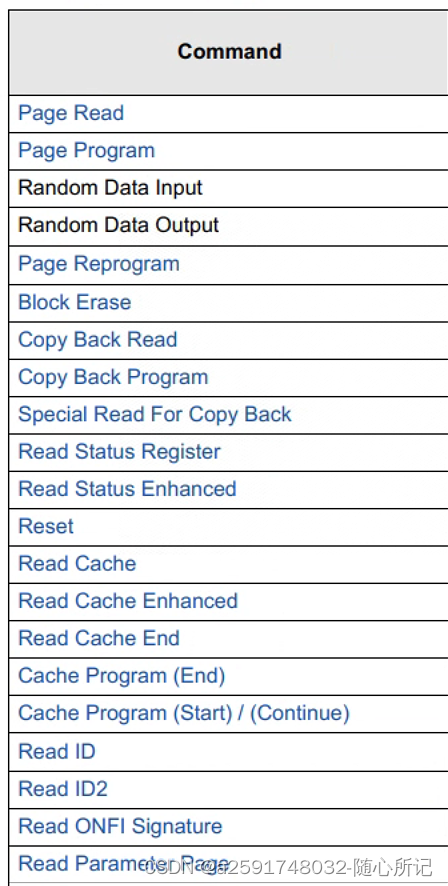

3.3 nand flash 常用操作命令集

本文介绍了MCP技术,重点解析了NAND Flash和DDR的内部结构、操作命令集以及与SOC的连接方式。NAND Flash部分详细阐述了其存储数据结构、读写时序和地址访问,而DDR部分则涵盖了其在MCP中的位置、接口、内部逻辑组成以及读写时序。

本文介绍了MCP技术,重点解析了NAND Flash和DDR的内部结构、操作命令集以及与SOC的连接方式。NAND Flash部分详细阐述了其存储数据结构、读写时序和地址访问,而DDR部分则涵盖了其在MCP中的位置、接口、内部逻辑组成以及读写时序。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

398

398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?