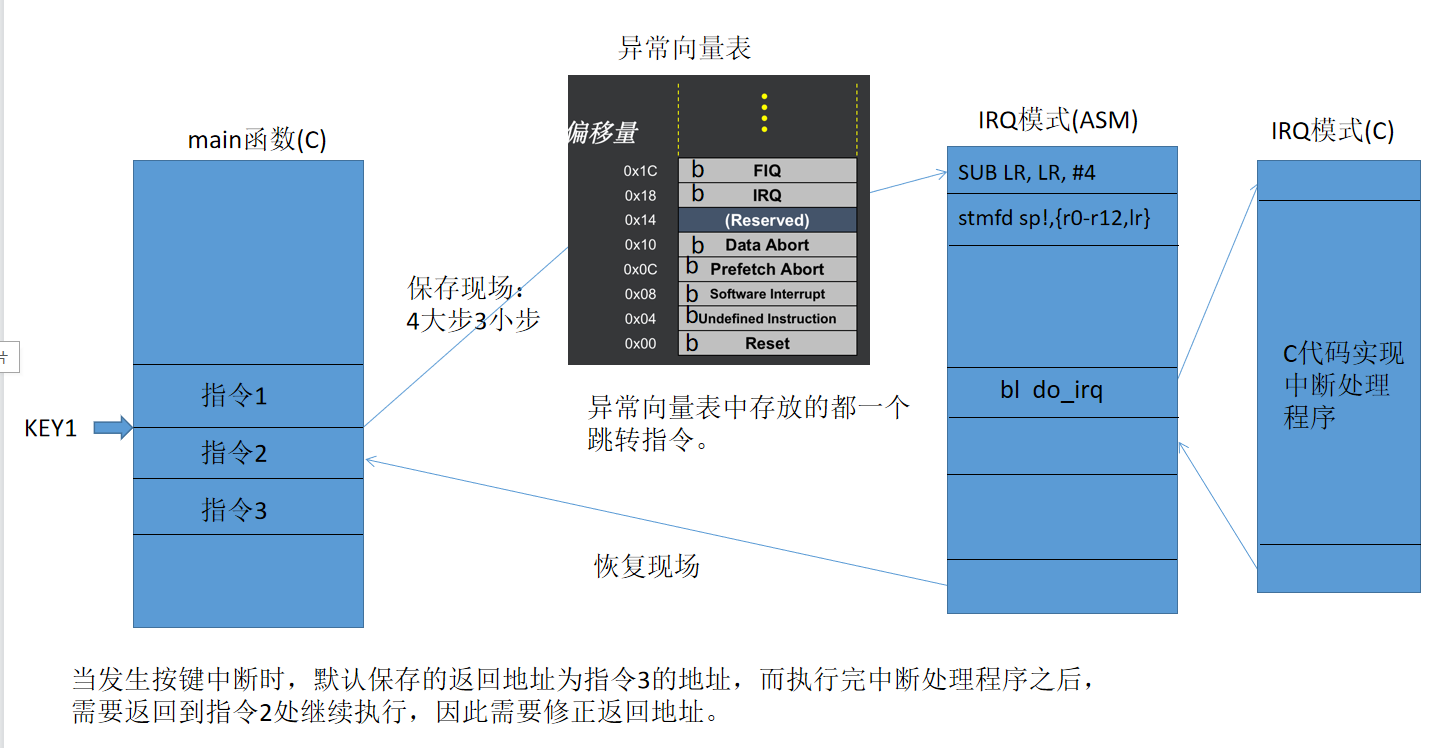

按键中断实验

1、按键电路图分析

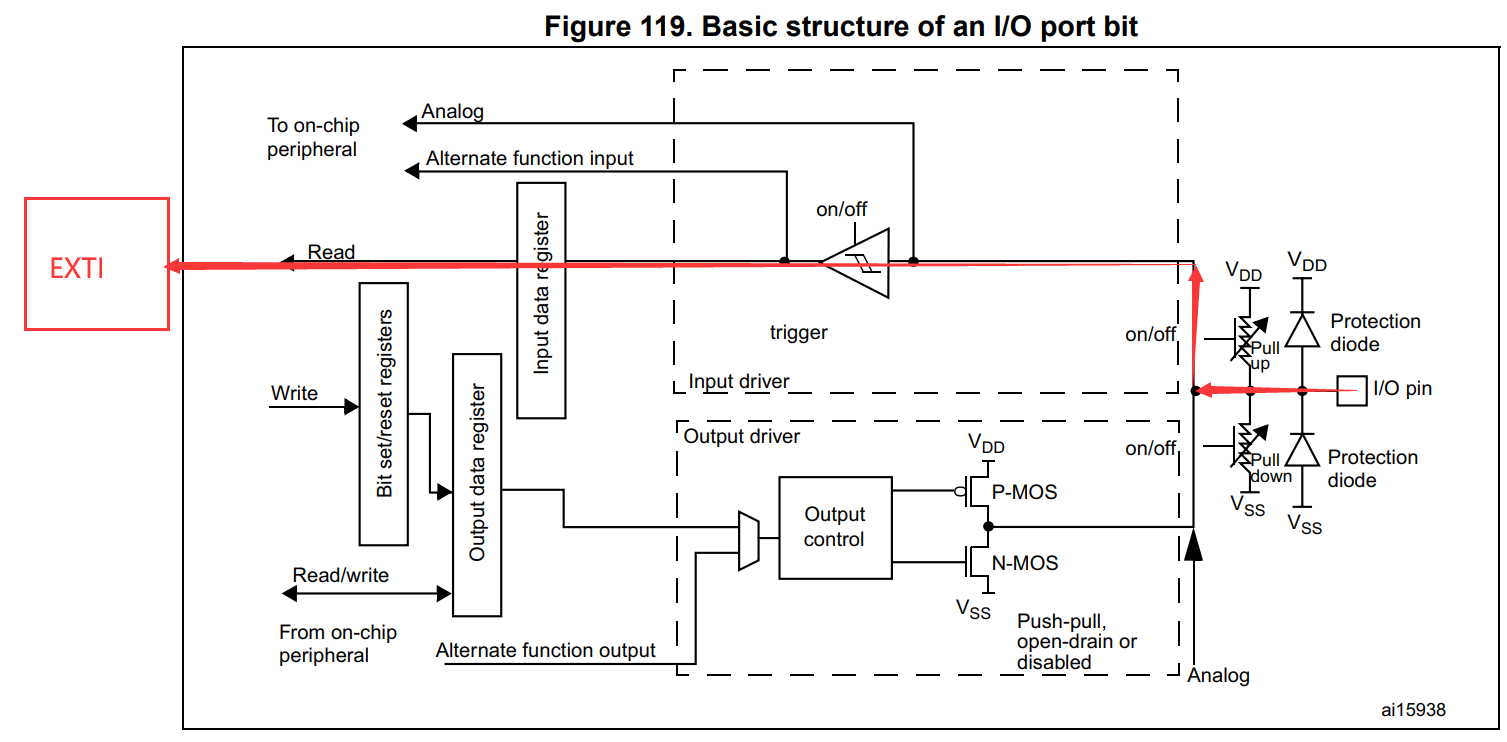

按键抬起时,PF9引脚输入高电平,按键按下时,PF9引脚输入低电平。

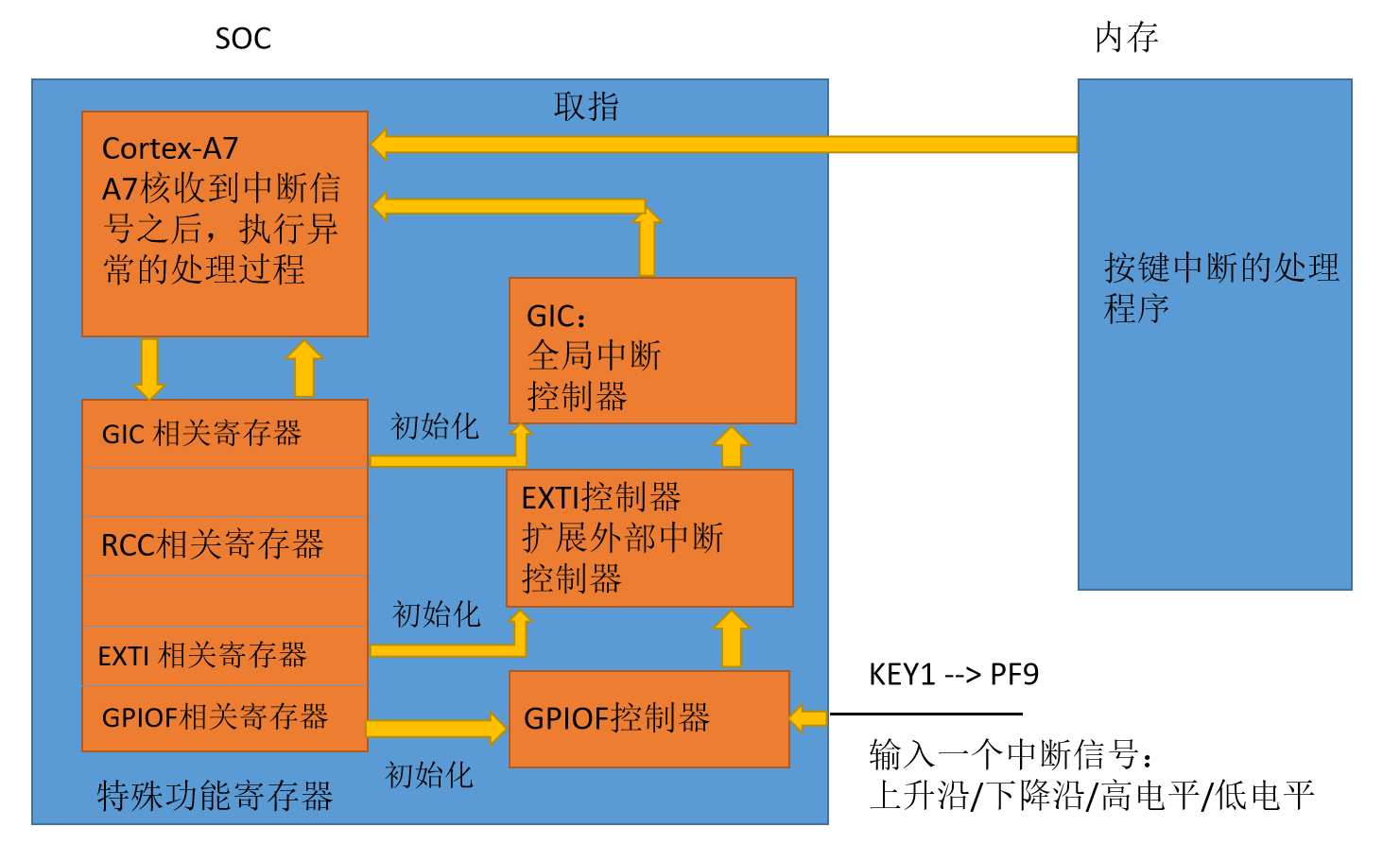

2、分析按键中断的数据手册

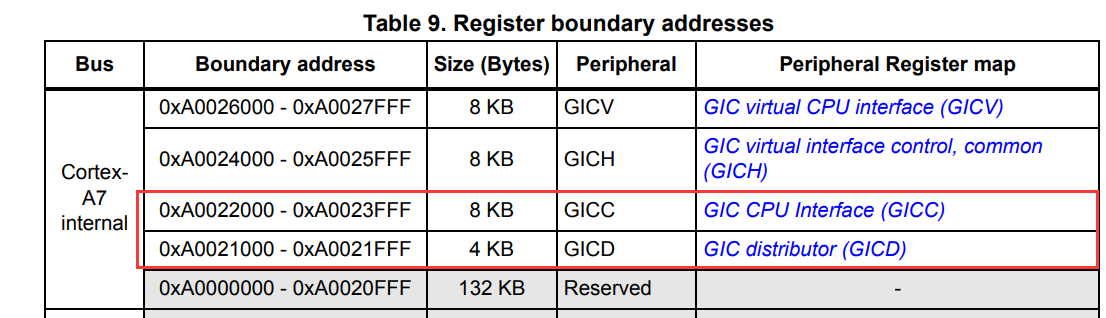

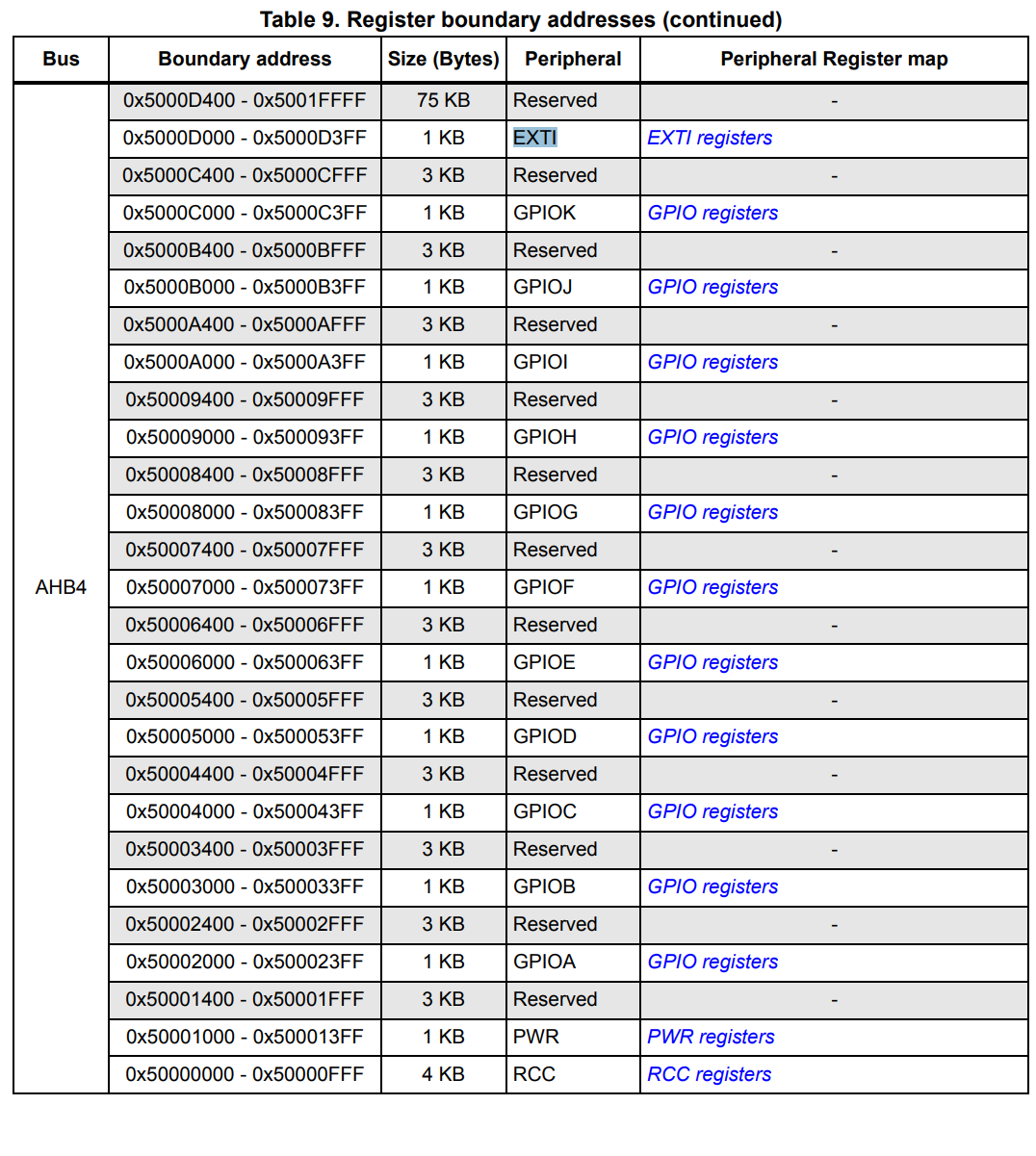

2.1 分析2.5.2章节,确定GPIOF,RCC,EXTI,GIC外设分别接到哪个总线上,以及外设寄存器对应的基地址

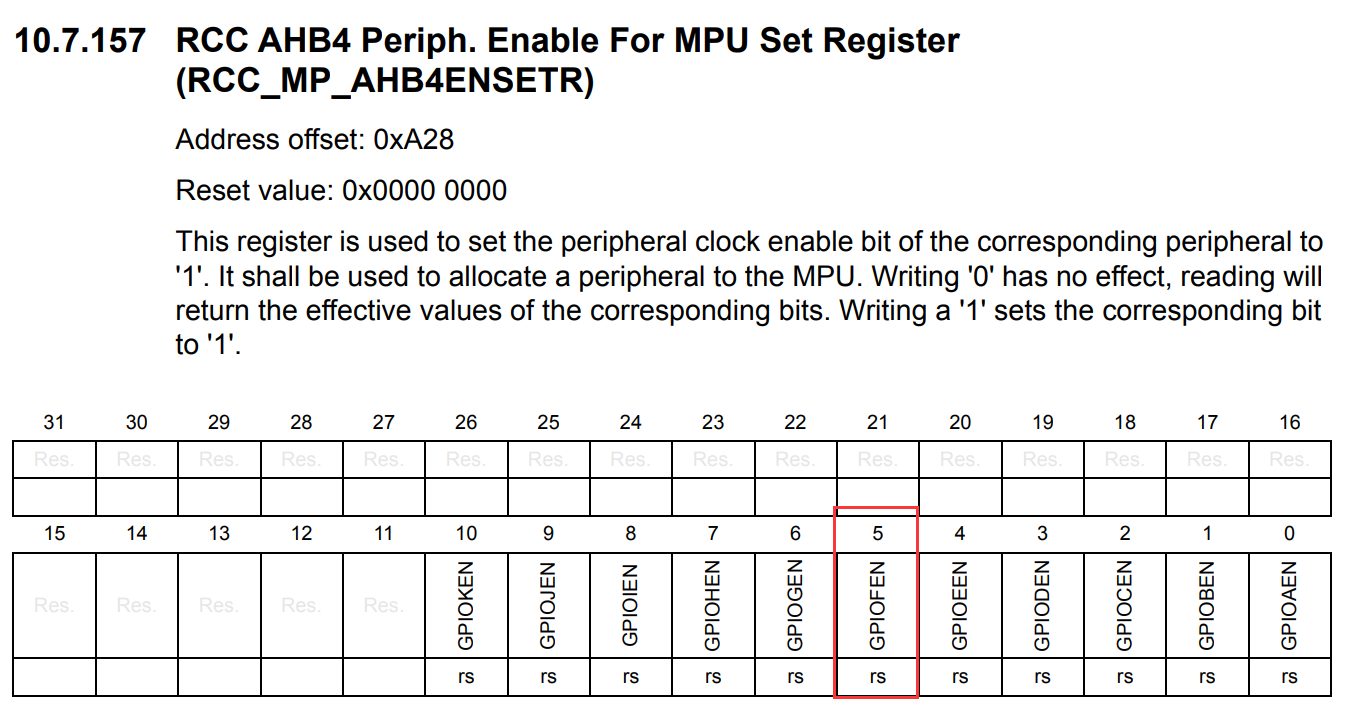

2.2 分析RCC章节,使能GPIOF外设控制器的时钟

2.3 分析GPIO章节,设置GPIO引脚为输入模式

2.3.1 GPIOx_MODER寄存器

2.3.2 GPIOx_PUPDR寄存器

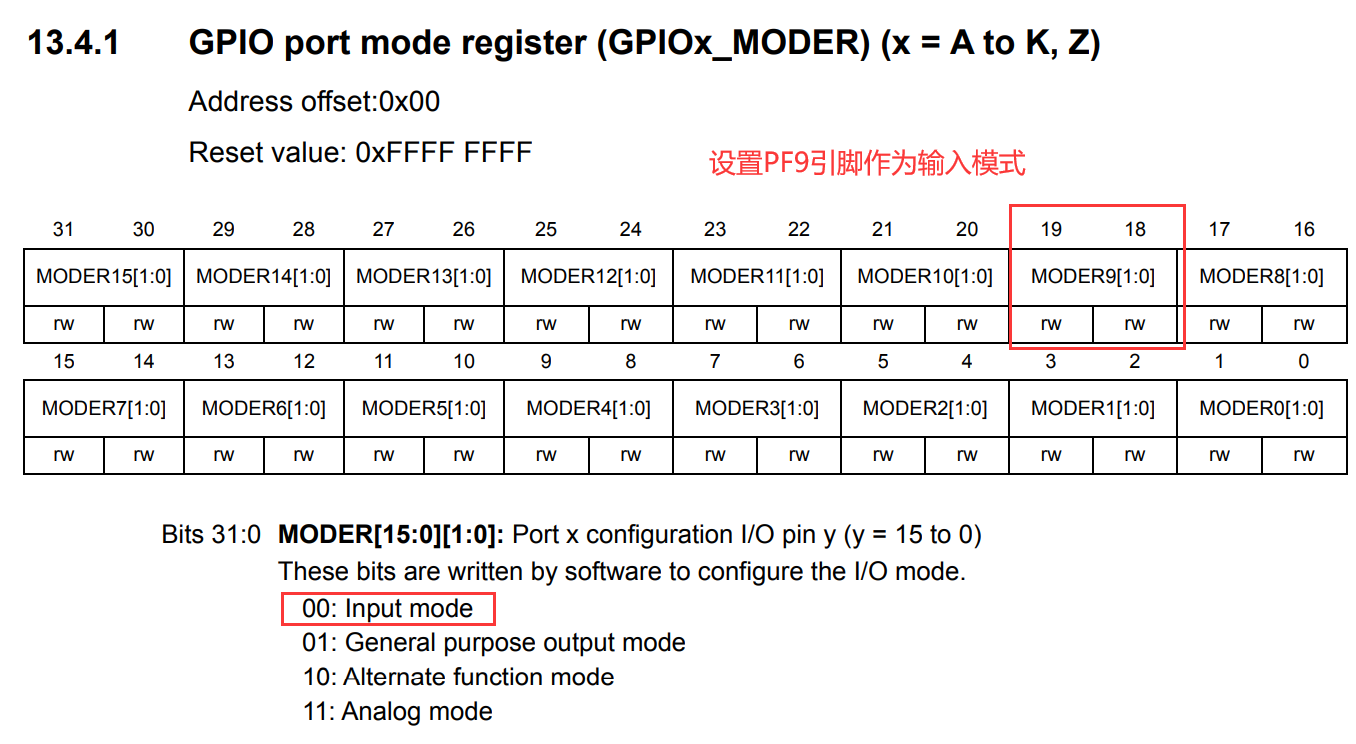

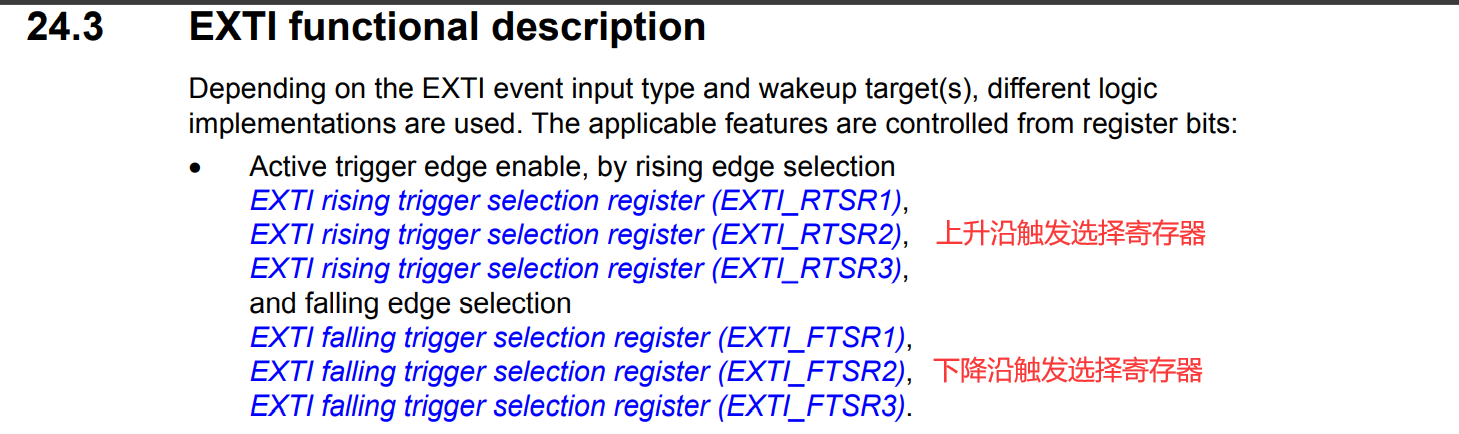

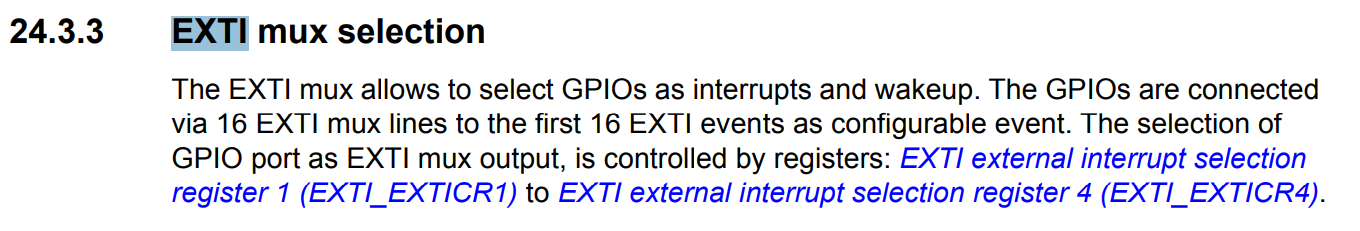

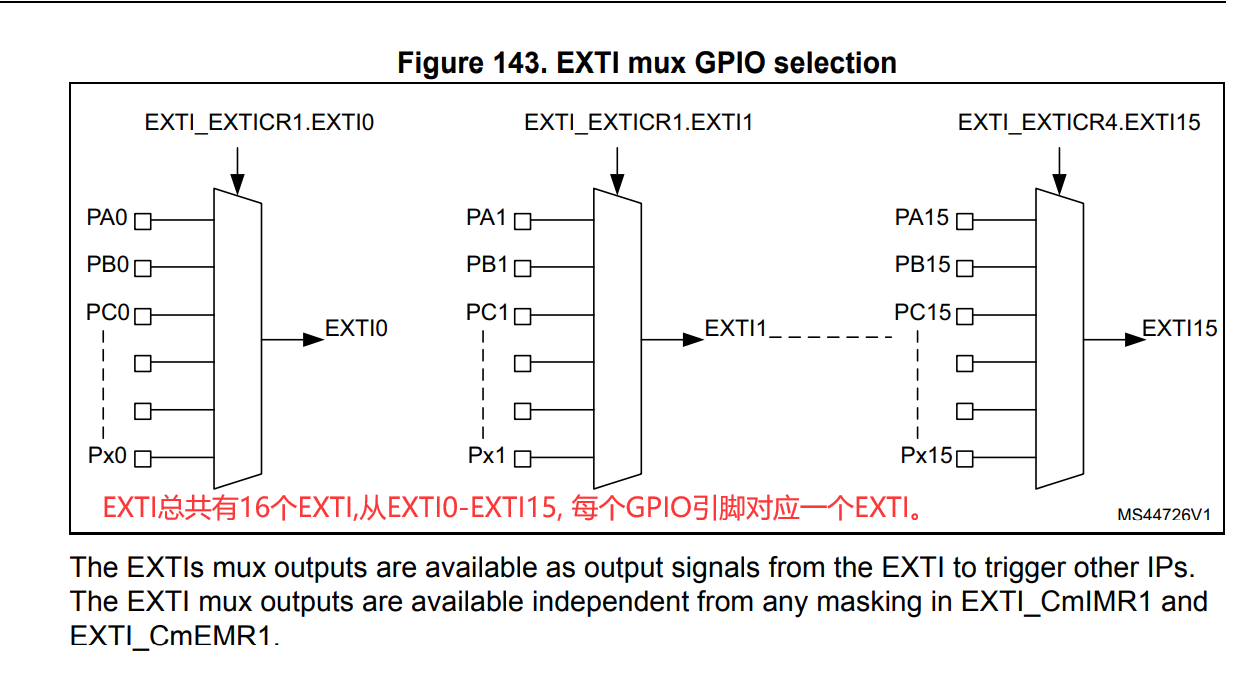

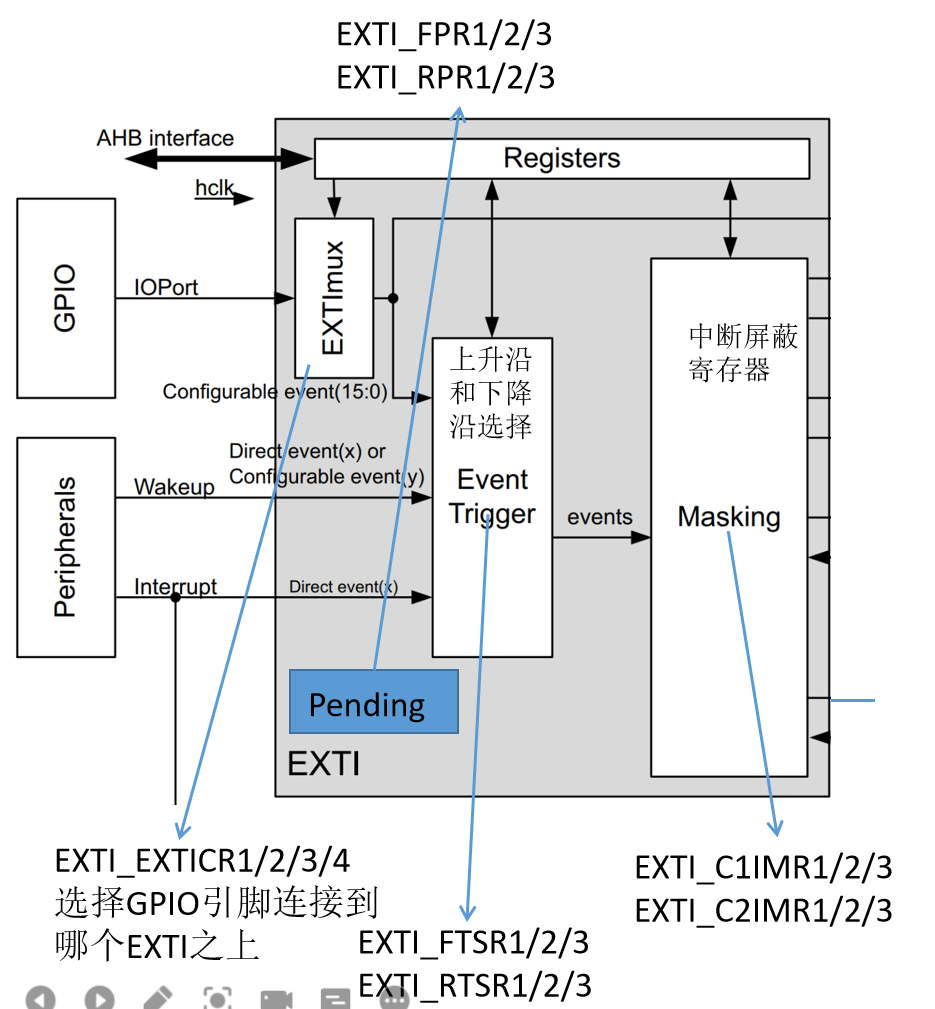

2.4 分析EXTI章节,设置中断信号的检测

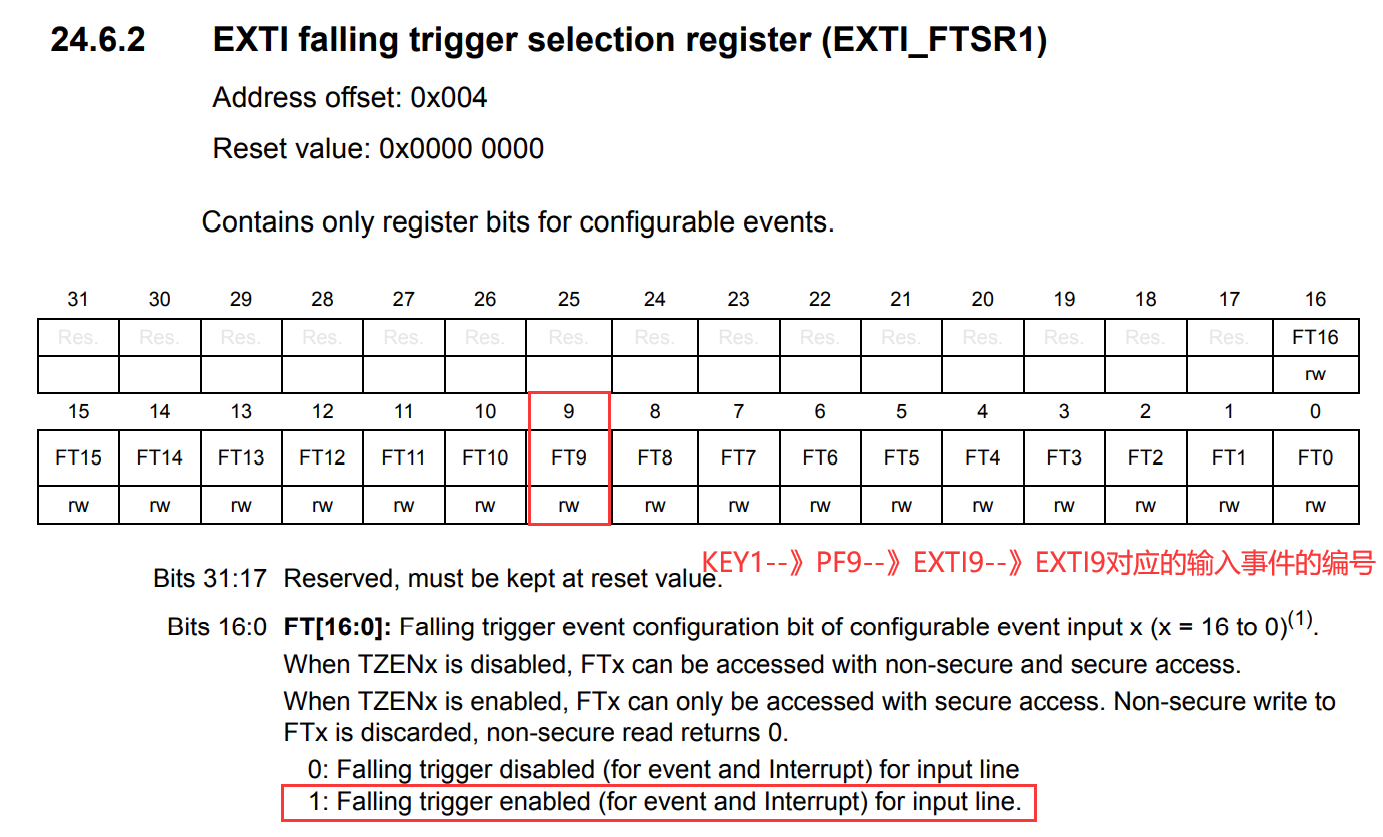

2.4.1 EXTI_FTSR1寄存器

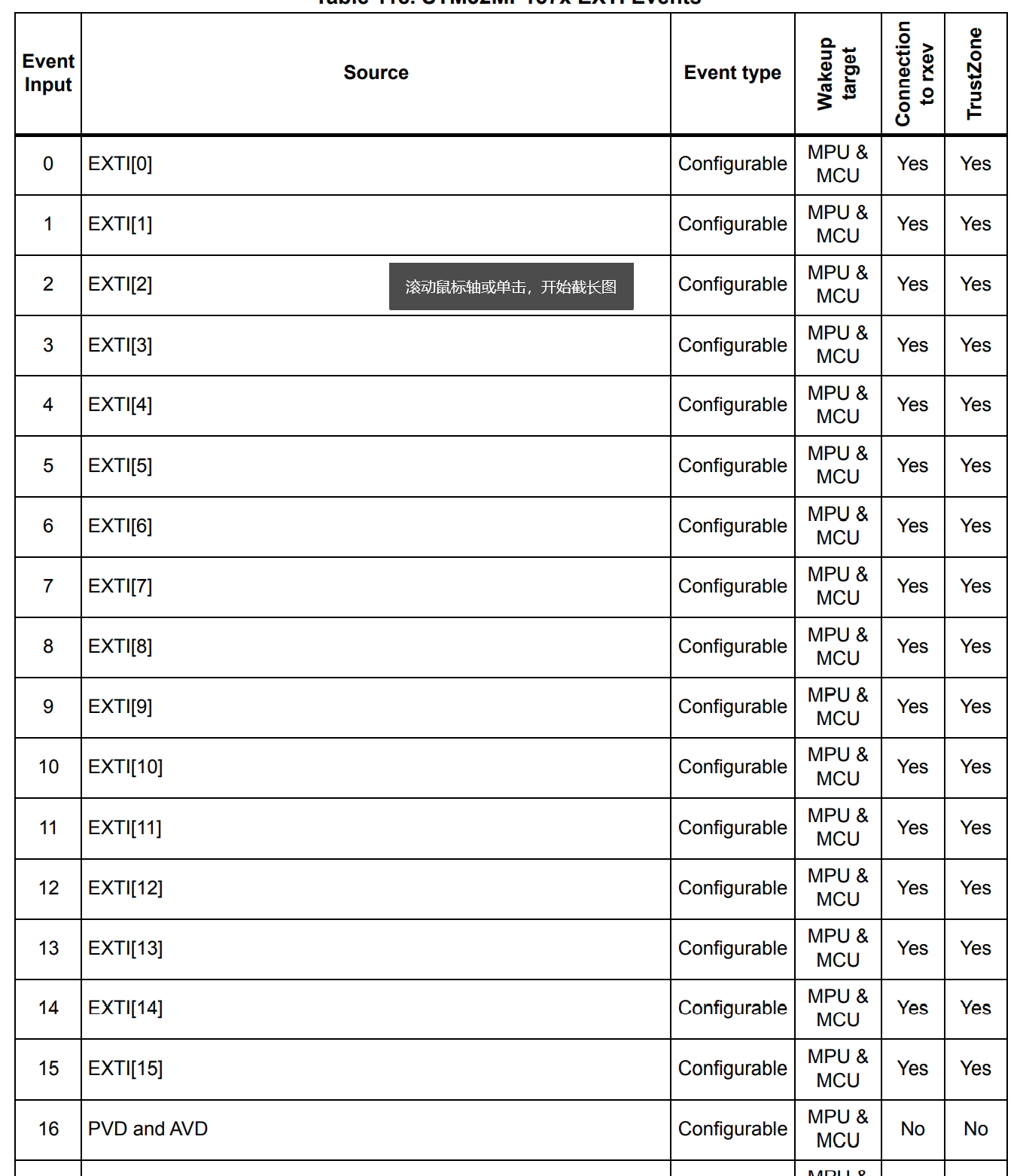

KEY1--》PF9--》EXTI9---》EXTI9对应的输入事件的编号,需要查看数据手册的21.3章节的表118,如下图所示,

可知EXTI9对应的输入事件的编号位输入事件9号。

EXTI_FTSR1[9]写1,使能下降沿触发中断。及当有下降沿时就认为是一个中断信号。

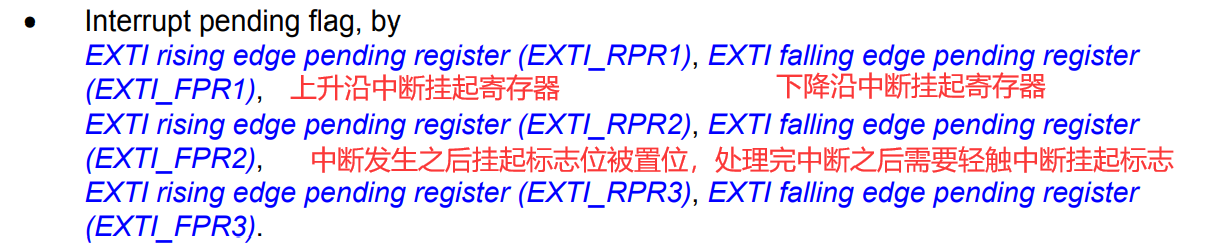

2.4.2 EXTI_FPR1寄存器

KEY1--》PF9--》EXTI9---》EXTI9对应的输入事件的编号,需要查看数据手册的21.3章节的表118,

可知EXTI9对应的输入事件的编号位输入事件9号。

EXTI_FPR1[9]写1,清除下降沿中断挂起标志位。

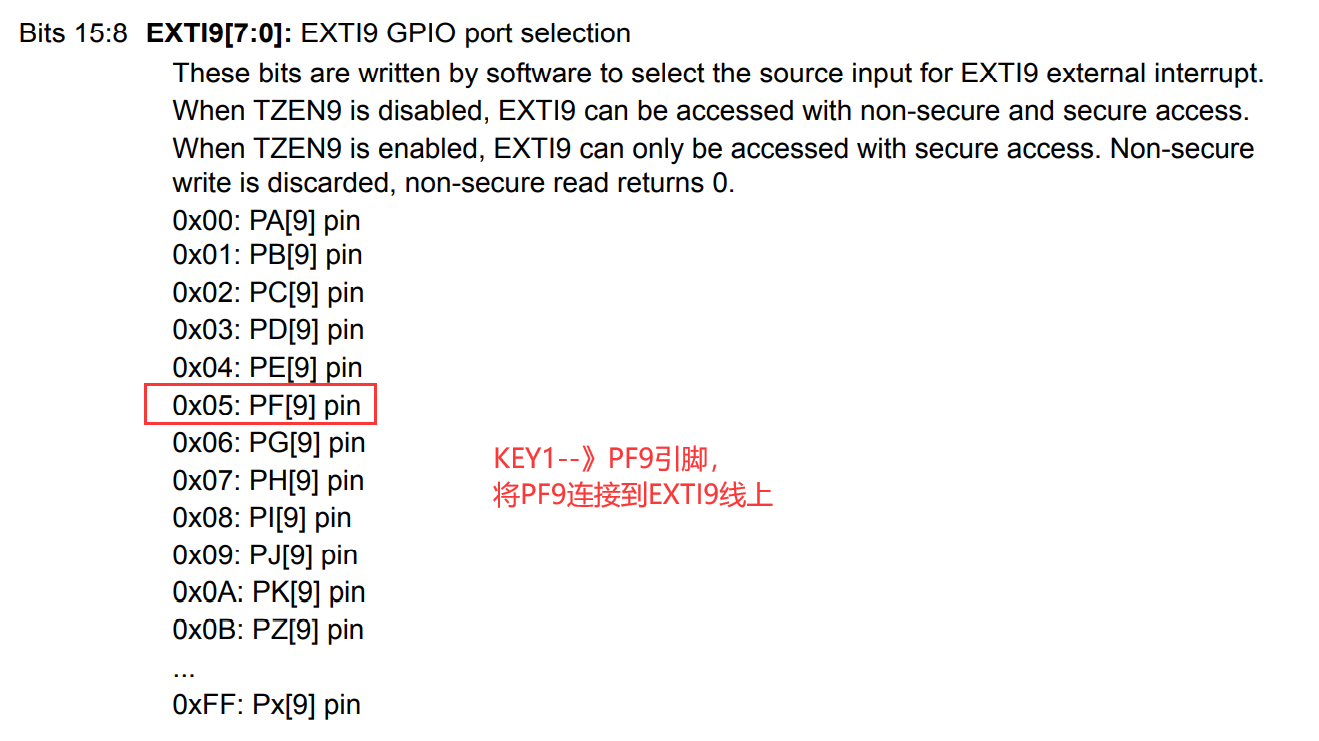

2.4.3 EXTI_EXTICR3寄存器

EXTI中总共有16个EXTI,从EXTI0-EXTI9,EXTI_EXTICR寄存器的每8位管理一个EXTI外设,

几个寄存器最多管理4个EXTI,因此需要4个寄存器工程管理16个EXTI。

KEY1--> PF9 ---> EXTI9 ---》EXTI_EXTICR3[15:8] ---> 写0x5,将PF9连接到EXTI9上

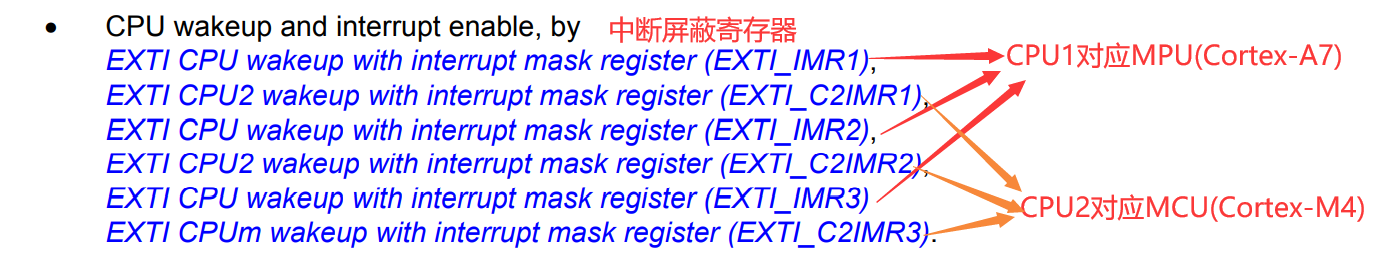

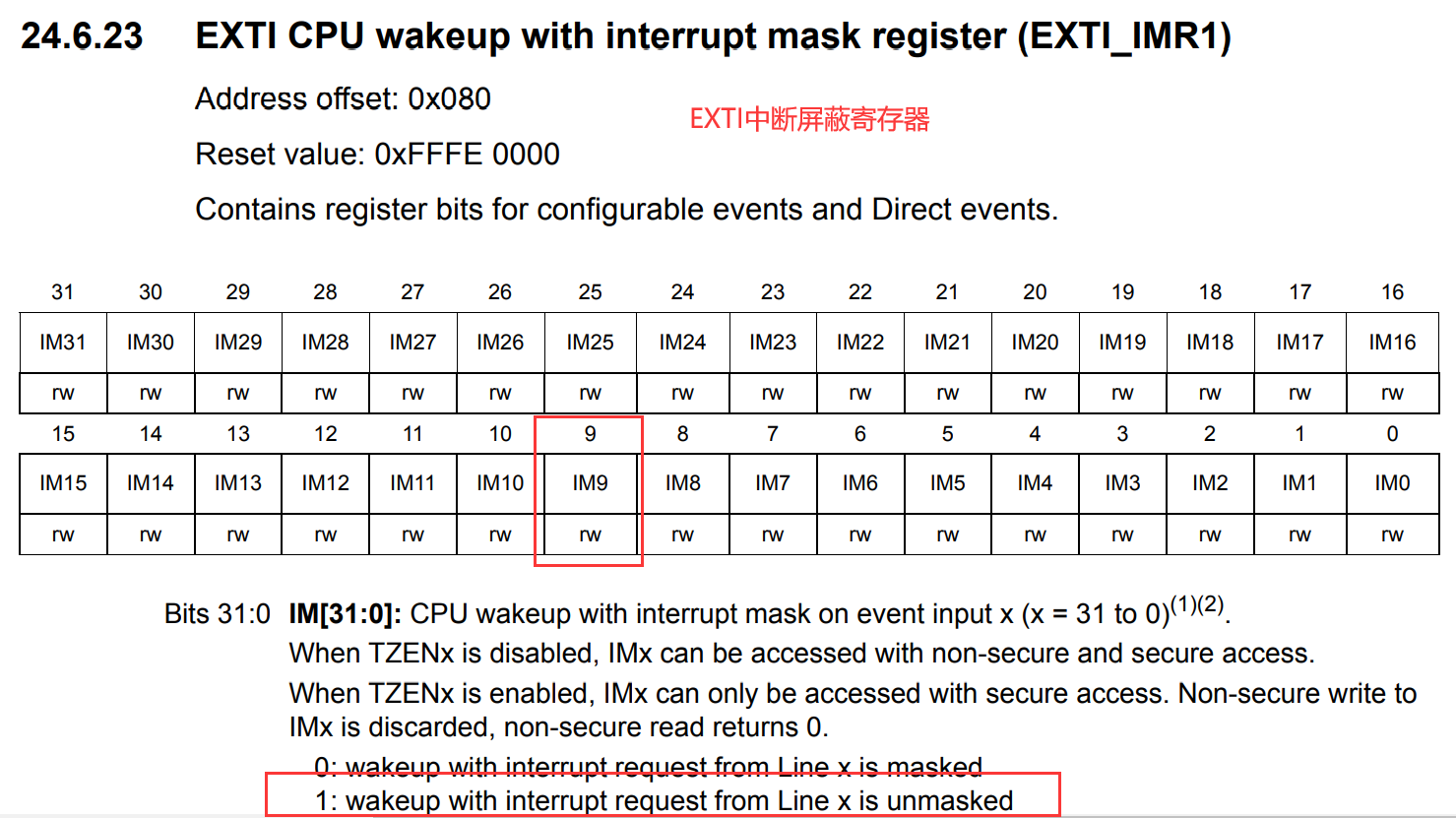

2.4.4 EXTI_C1IMR1寄存器

KEY1--》PF9--》EXTI9---》EXTI9对应的输入事件的编号,需要查看数据手册的21.3章节的表118,

可知EXTI9对应的输入事件的编号为输入事件9号。

EXTI_C1IMR1[9]写1,不屏蔽中断信号。

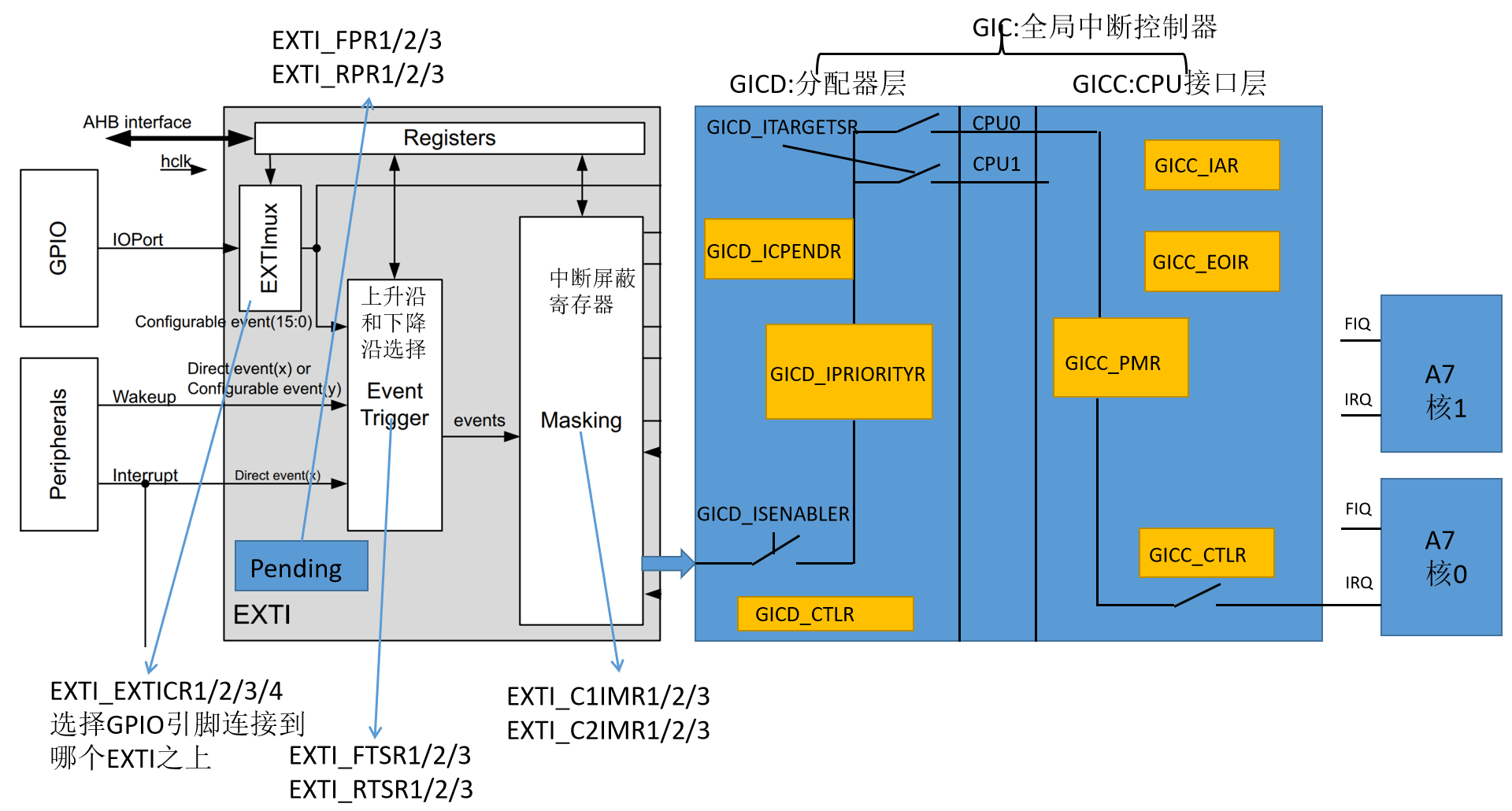

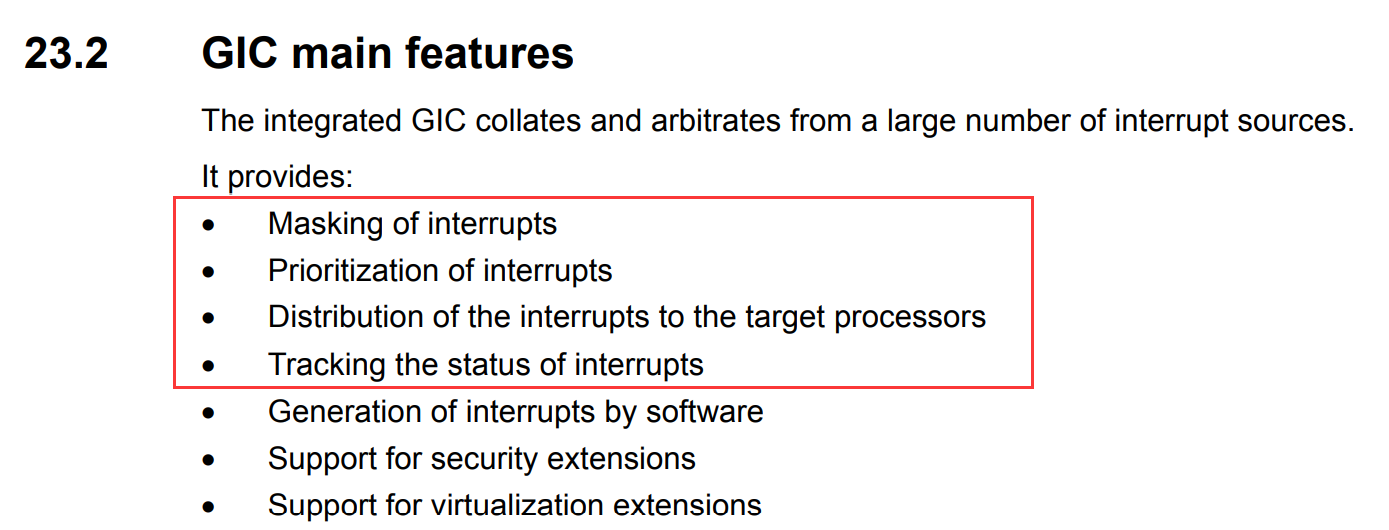

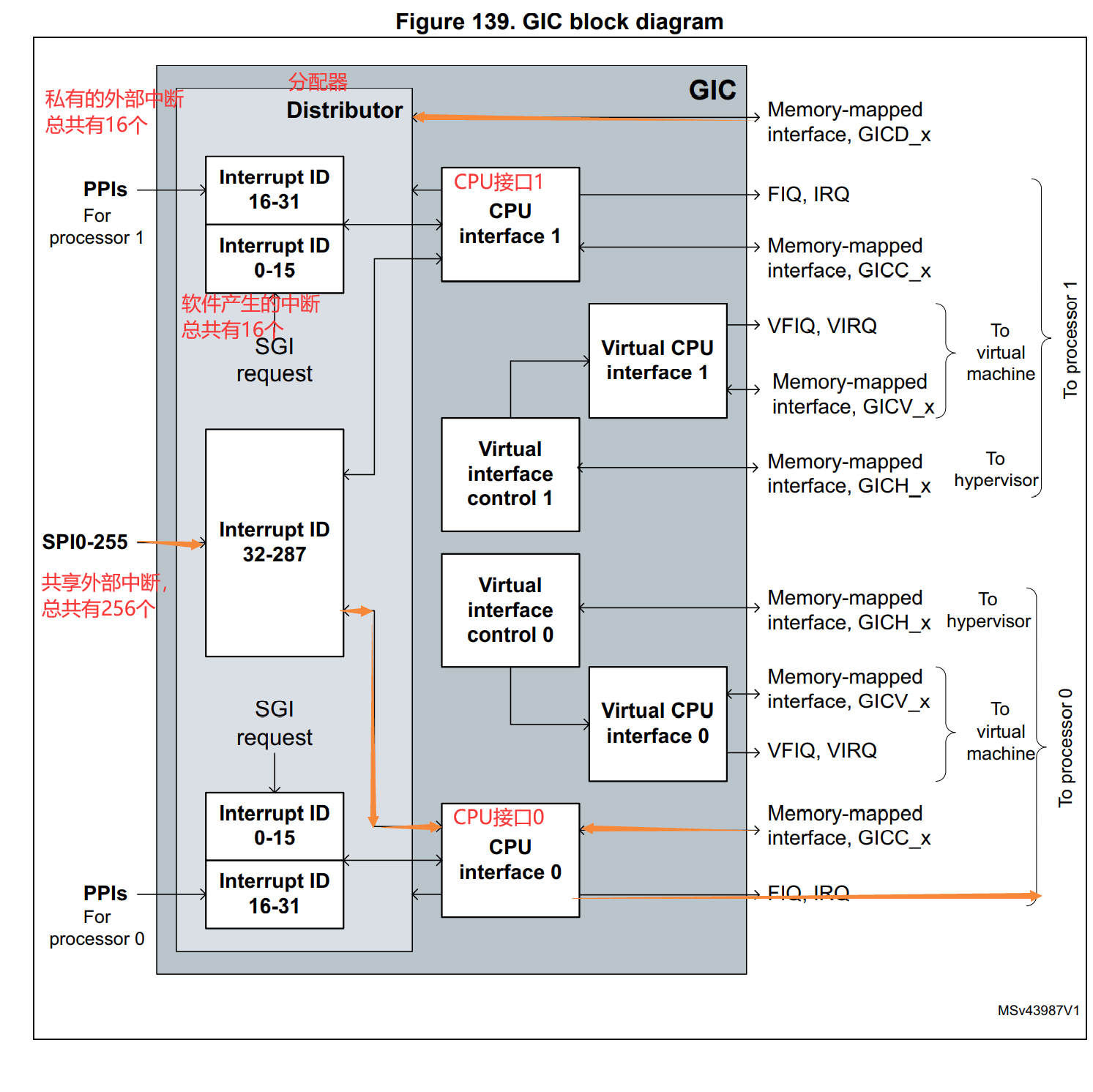

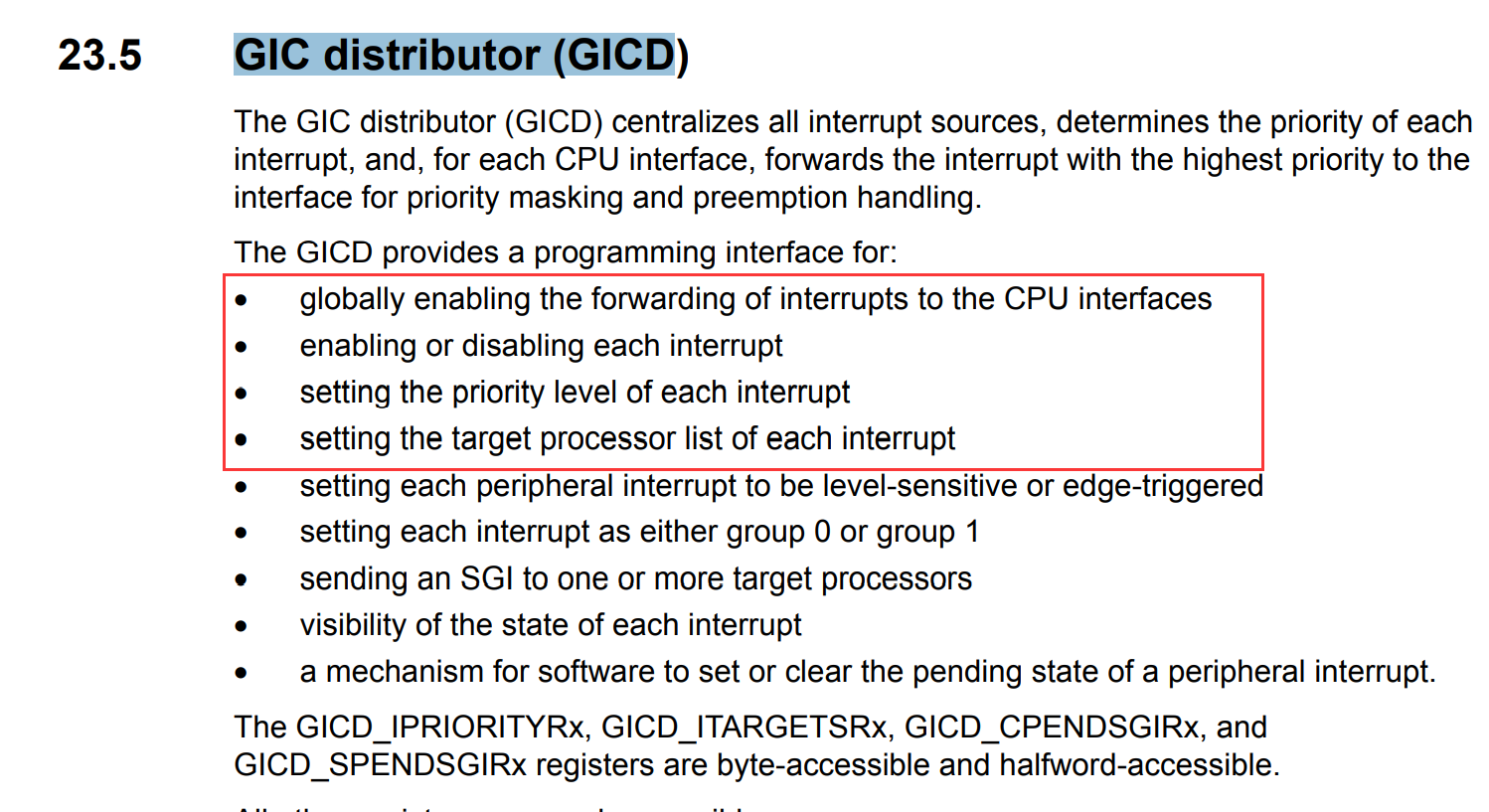

2.5 分析GIC章节,设置全局中断控制器

GICD_CTLR : GICD层全局使能寄存器

GICD_ISENABLER : GICD层中断设置使能寄存器

GICD_ICPENDR :GICD层中断清除挂起寄存器

GICD_IPRIORITYR : GICD层中断优先级设置寄存器

GICD_ITARGETSR : GICD层中断目标分配寄存器

GICC_CTLR : GICC层全局使能寄存器

GICC_PMR : GICC层优先级屏蔽寄存器

GICC_IAR : GICC层中断应答寄存器

GICC_EOIR :GICC层中断处理结束寄存器

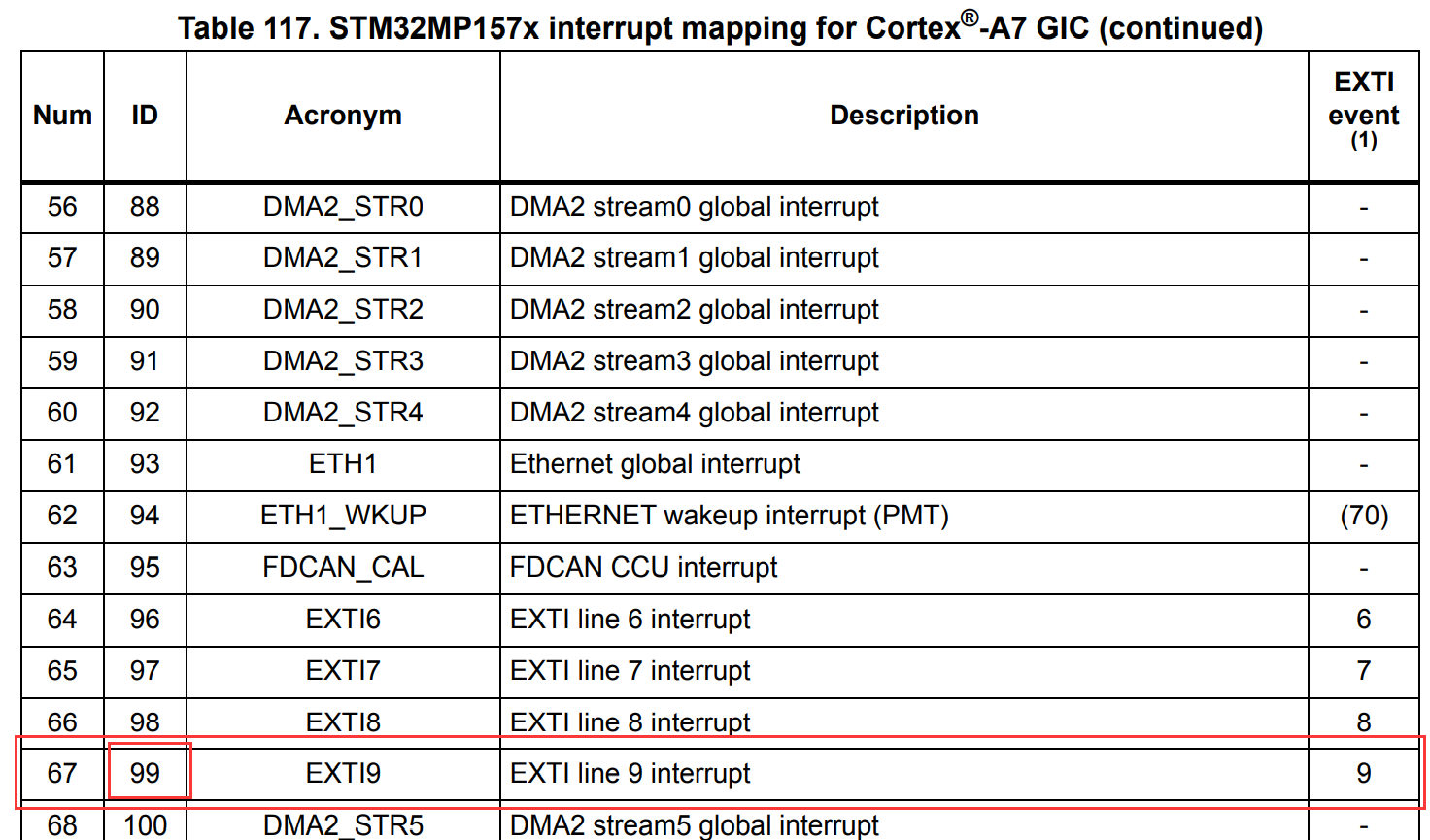

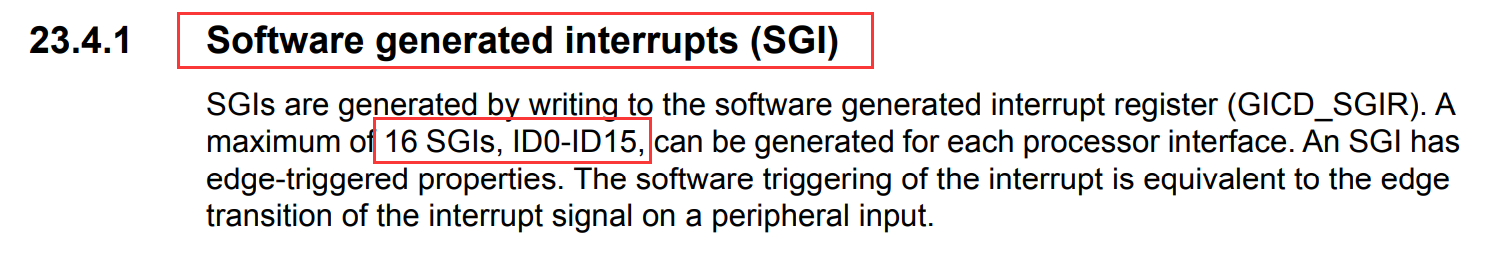

2.5.1 中断号的获取

每个中断外设都有一个唯一的中断号,通过查看芯片手册的21.2章节的表117,如下图所示:

KEY1 ---》 PF9 ---》 EXTI9 ----》中断号:99

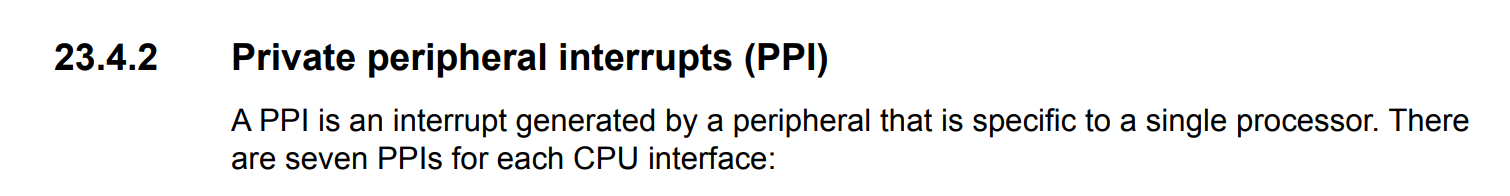

2.5.2 GIC全局中断控制器的介绍

2.5.3 GICD介绍

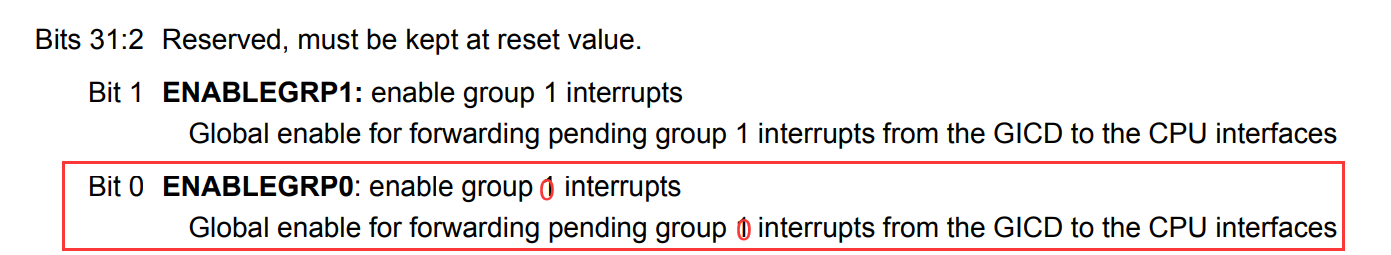

2.5.4 GICD_CTLR : GICD层全局使能寄存器

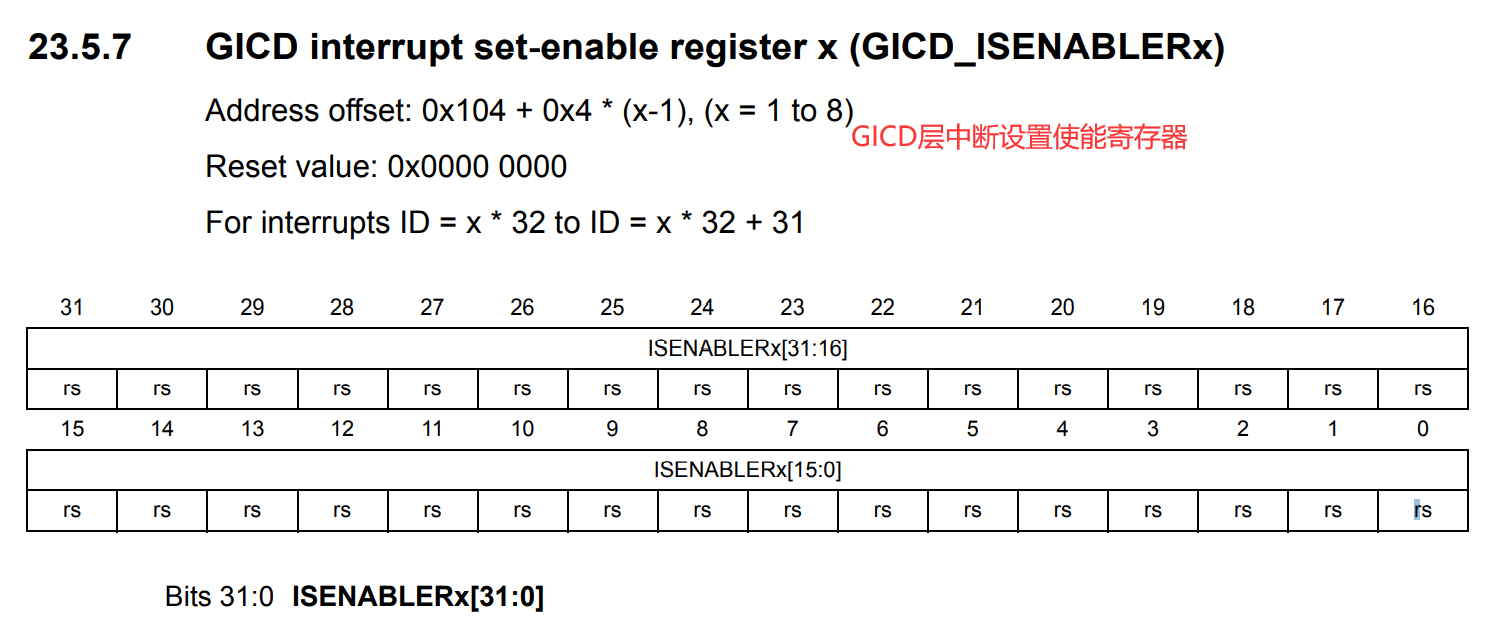

2.5.5 GICD_ISENABLER : GICD层中断设置使能寄存器

前提:KEY1 ---》 PF9 ---》 EXTI9 ----》中断号:99

GICD_ISENABLER : GICD层中断设置使能寄存器

GICD_ISENABLER寄存器的每1位管理一个中断号,一个寄存器最多管理32个中断号。

GIC控制器支持16个SGIs,16个PPIs, 256个SPIs, GIC控制器总共支持288个中断号,

GICD_ISENABLER寄存器要想管理288个中断号,最少需要9(288/32)个寄存器。

99号中断对应GICD_ISENABLER寄存器的哪一个,哪一位?

99 / 32 = 3 ...... 3

商对应着寄存器的编号,余数对应操作寄存器的位。

GICD_ISENABLER3[3] 写1, 使能99号中断

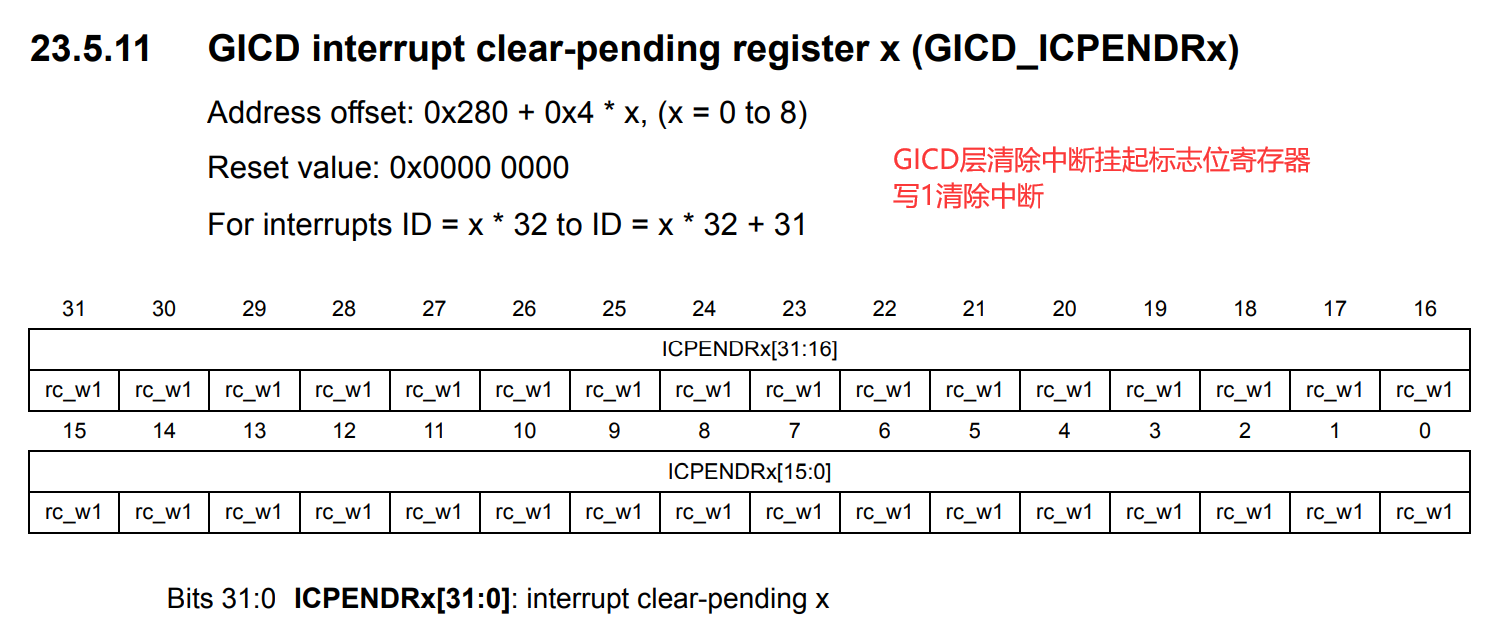

2.5.6 GICD_ICPENDR :GICD层中断清除挂起寄存器

前提:KEY1 ---》 PF9 ---》 EXTI9 ----》中断号:99

GICD_ICPENDR :GICD层中断清除挂起寄存器

GICD_ICPENDR寄存器的每1位管理一个中断号,一个寄存器最多管理32个中断号。

GIC控制器支持16个SGIs,16个PPIs, 256个SPIs, GIC控制器总共支持288个中断号,

GICD_ICPENDR寄存器要想管理288个中断号,最少需要9(288/32)个寄存器。

99号中断对应GICD_ICPENDR寄存器的哪一个,哪一位?

99 / 32 = 3 ...... 3

商对应着寄存器的编号,余数对应操作寄存器的位。

GICD_ICPENDR3[3]

写1, 清除99号中断挂起标志位

写0,没有影响

读0:表示99号中断没有发生

读1:表示99号中断发生

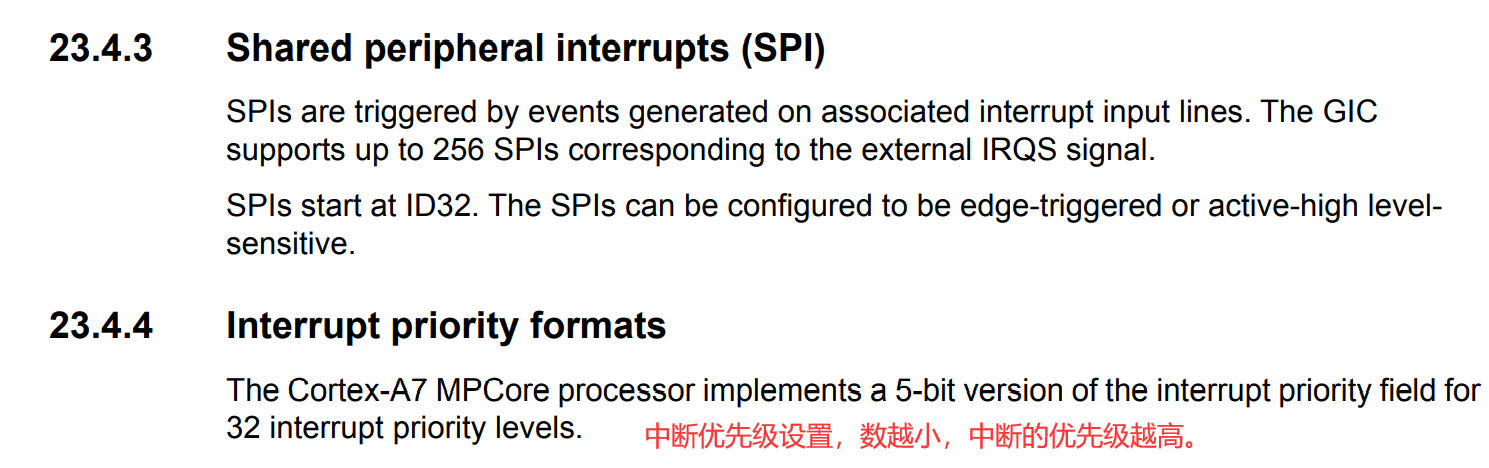

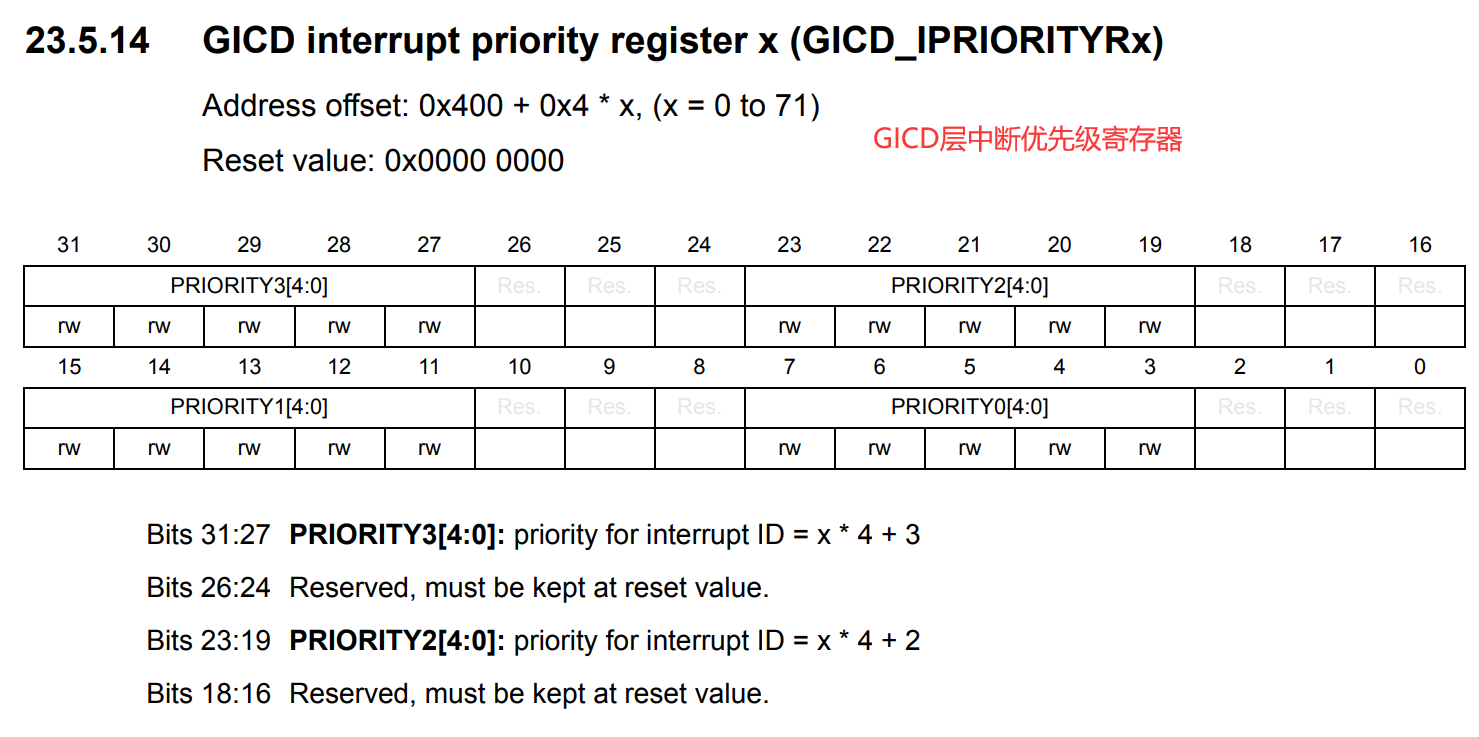

2.5.7 GICD_IPRIORITYR : GICD层中断优先级设置寄存器

前提:KEY1 ---》 PF9 ---》 EXTI9 ----》中断号:99

GICD_IPRIORITYR : GICD层中断优先级设置寄存器

GICD_IPRIORITYR寄存器的每8(5位有效位+3位保留位)位管理一个中断号,一个寄存器最多管理4个中断号。

GIC控制器支持16个SGIs,16个PPIs, 256个SPIs, GIC控制器总共支持288个中断号,

GICD_IPRIORITYR寄存器要想管理288个中断号,最少需要72(288/4)个寄存器。

99号中断对应GICD_IPRIORITYR寄存器的哪一个,哪5位?

99 / 4 = 24 ...... 3

商对应着寄存器的编号,(余数*8+3) 对应操作寄存器的最低位。

GICD_IPRIORITYR24[31:27] 设置中断的优先等级,数越小,优先级越高

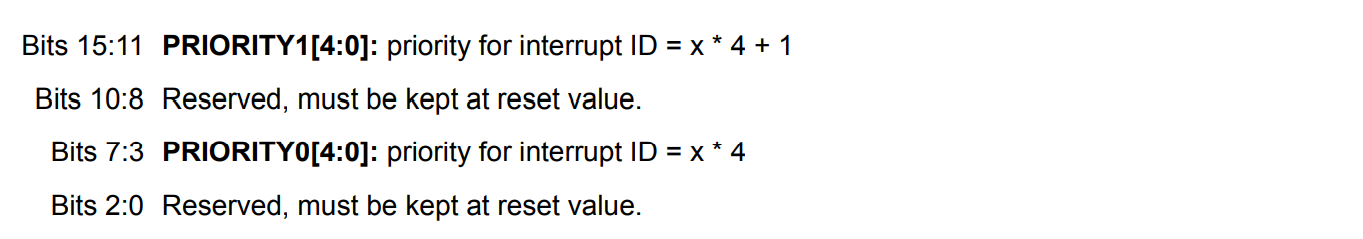

2.5.8 GICD_ITARGETSR : GICD层中断目标分配寄存器

前提:KEY1 ---》 PF9 ---》 EXTI9 ----》中断号:99

GICD_ITARGETSR : GICD层中断目标分配寄存器

GICD_ITARGETSR寄存器的每8(6位保留位+2位有效位)位管理一个中断号,一个寄存器最多管理4个中断号。

GIC控制器支持16个SGIs,16个PPIs, 256个SPIs, GIC控制器总共支持288个中断号,

GICD_ITARGETSR寄存器要想管理288个中断号,最少需要72(288/4)个寄存器。

99号中断对应GICD_ITARGETSR寄存器的哪一个,哪2位?

99 / 4 = 24 ...... 3

商对应着寄存器的编号,(余数*8) 对应操作寄存器的最低位。

GICD_ITARGETSR24[25:24] 分配中断到不同的CPU接口中

写01 : 分配给CPU接口0

写10 : 分配给CPU接口1

写11 : 分配给CPU接口0和CPU接口1

这个寄存器的每1位管理一个CPU核,STM32MP1处理器有两个CPU核,因此需要两位即可

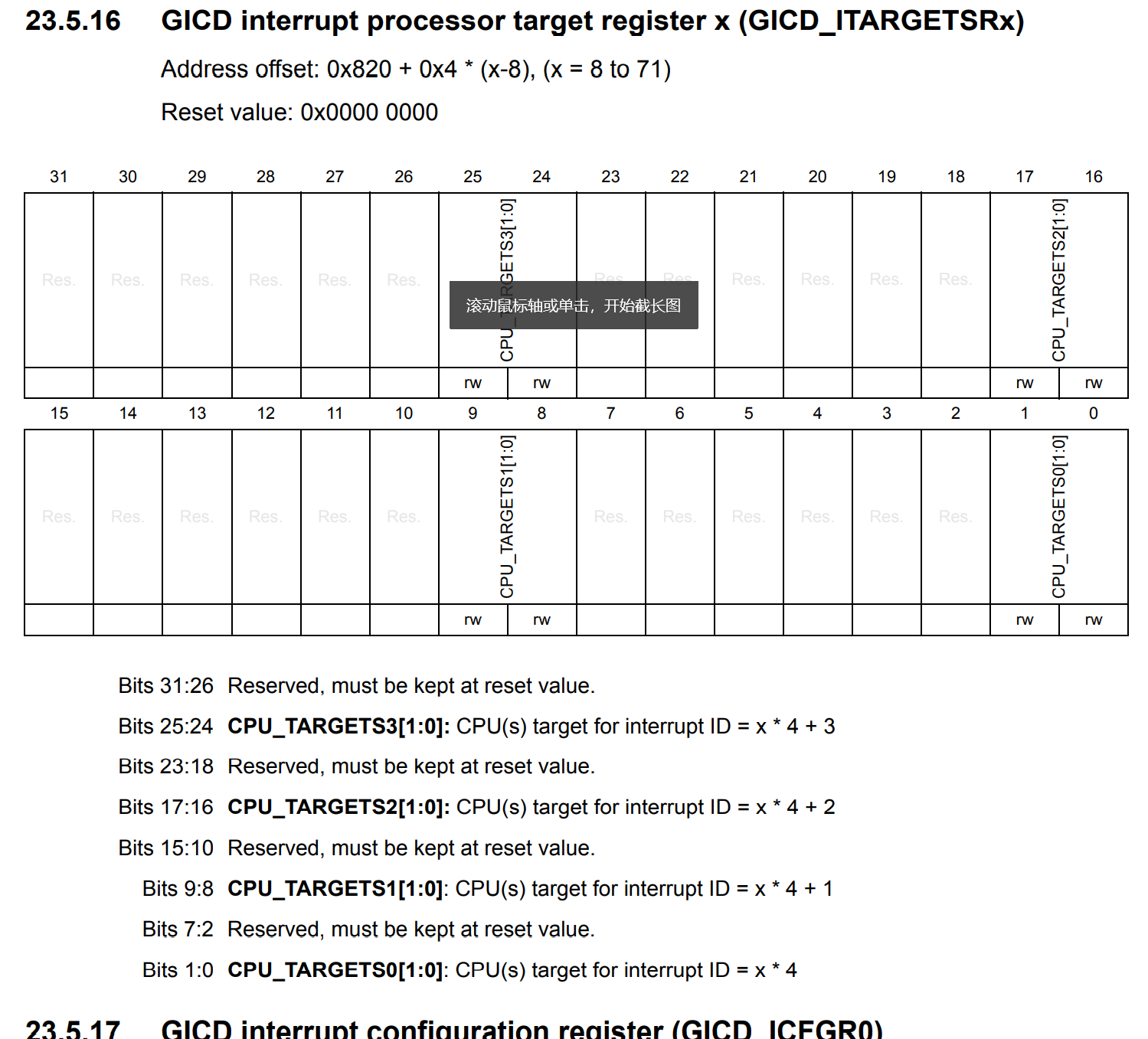

2.5.9 GICC介绍

2.5.10 GICC_CTLR : GICC层全局使能寄存器

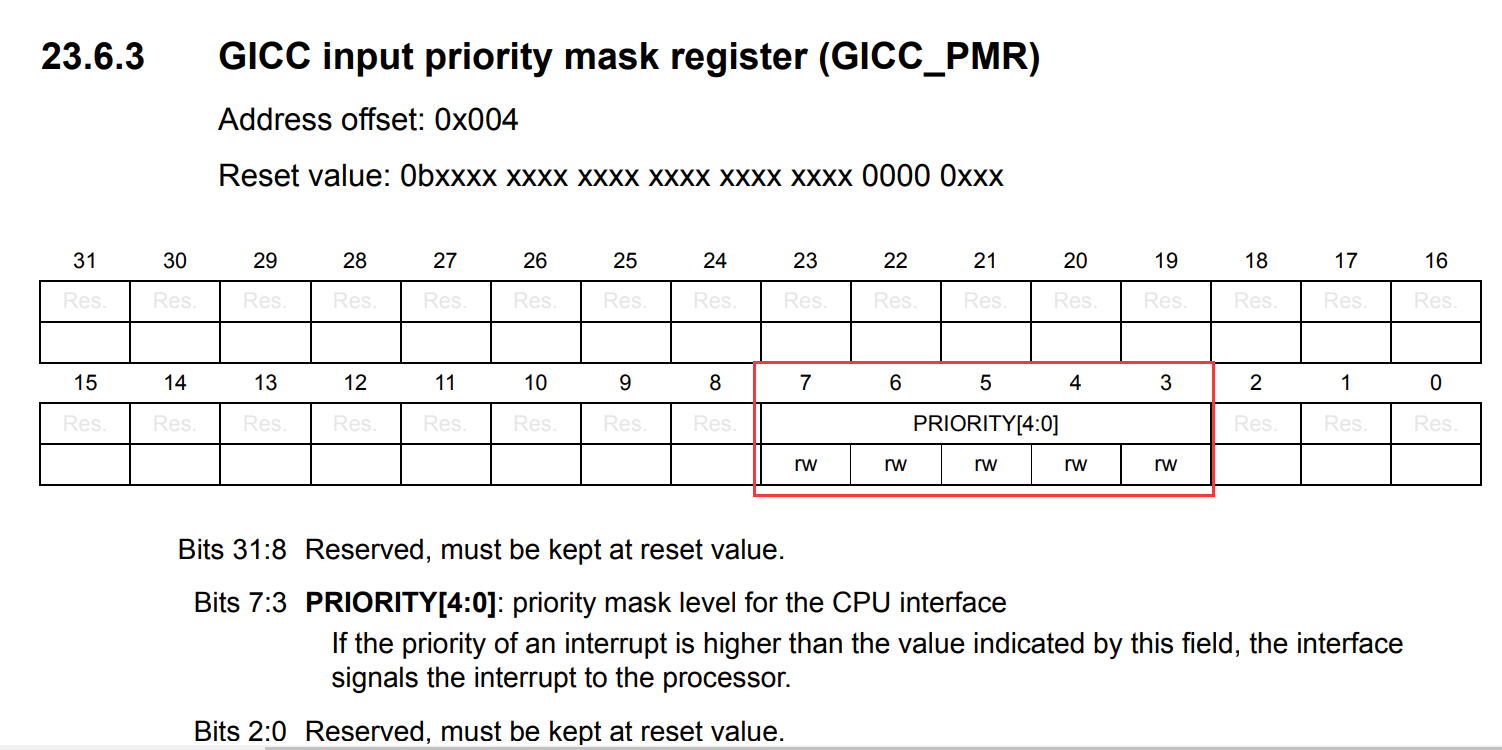

2.5.11 GICC_PMR : GICC层优先级屏蔽寄存器

如果一个中断信号的优先级值高于GICC_PMR寄存器字段中的值,则对应的中断将会被转发到CPU中,

中断信号的优先级通过GICD_IPRIORITYR寄存器进行配置。

假设中断信号的优先级为10, GICC_PMR[7:3]为20, 此中断信号被转发到CPU中。

假设中断信号的优先级为20, GICC_PMR[7:3]为10, 此中断信号不被转发到CPU中。

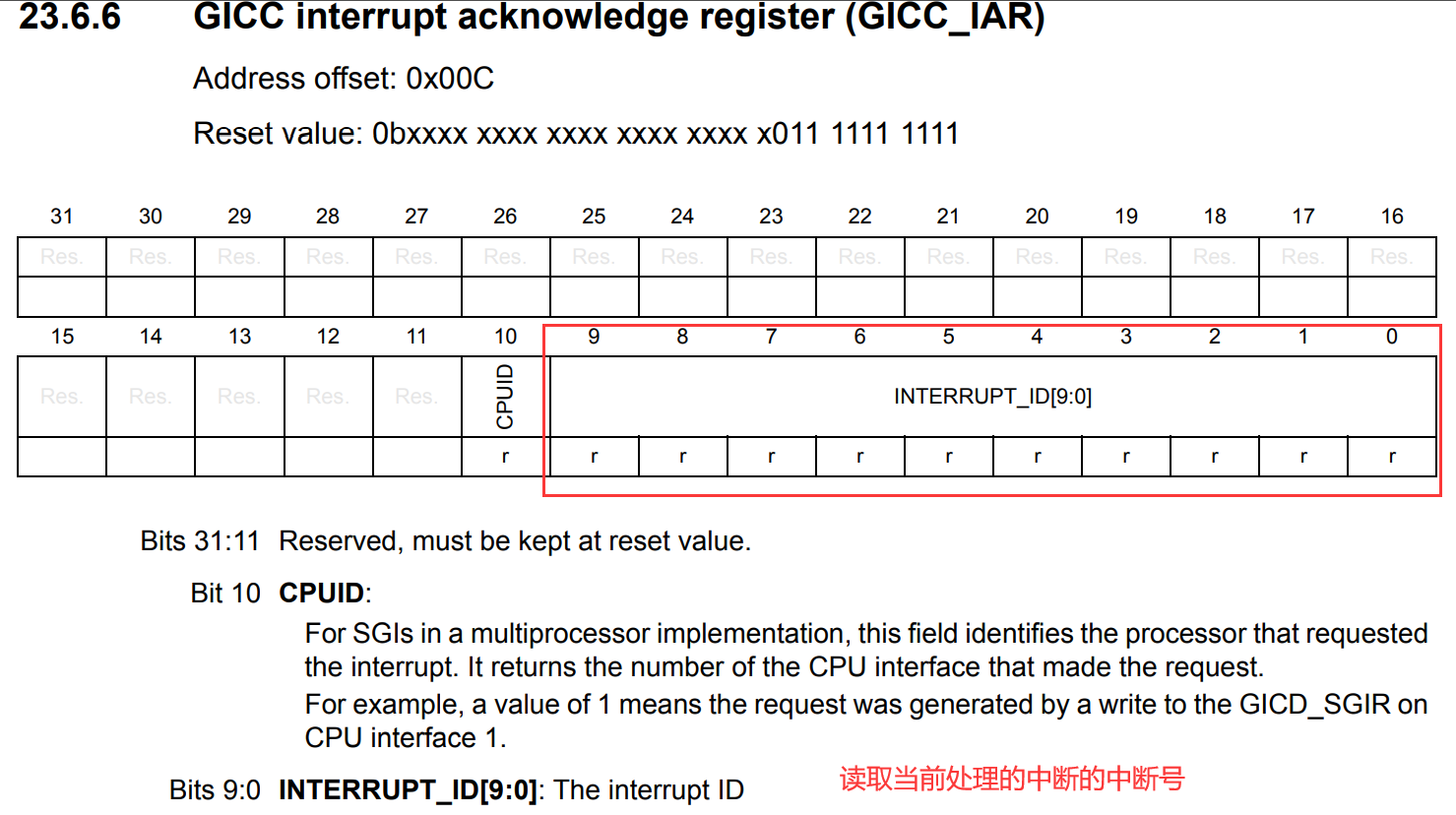

2.5.12 GICC_IAR : GICC层中断应答寄存器

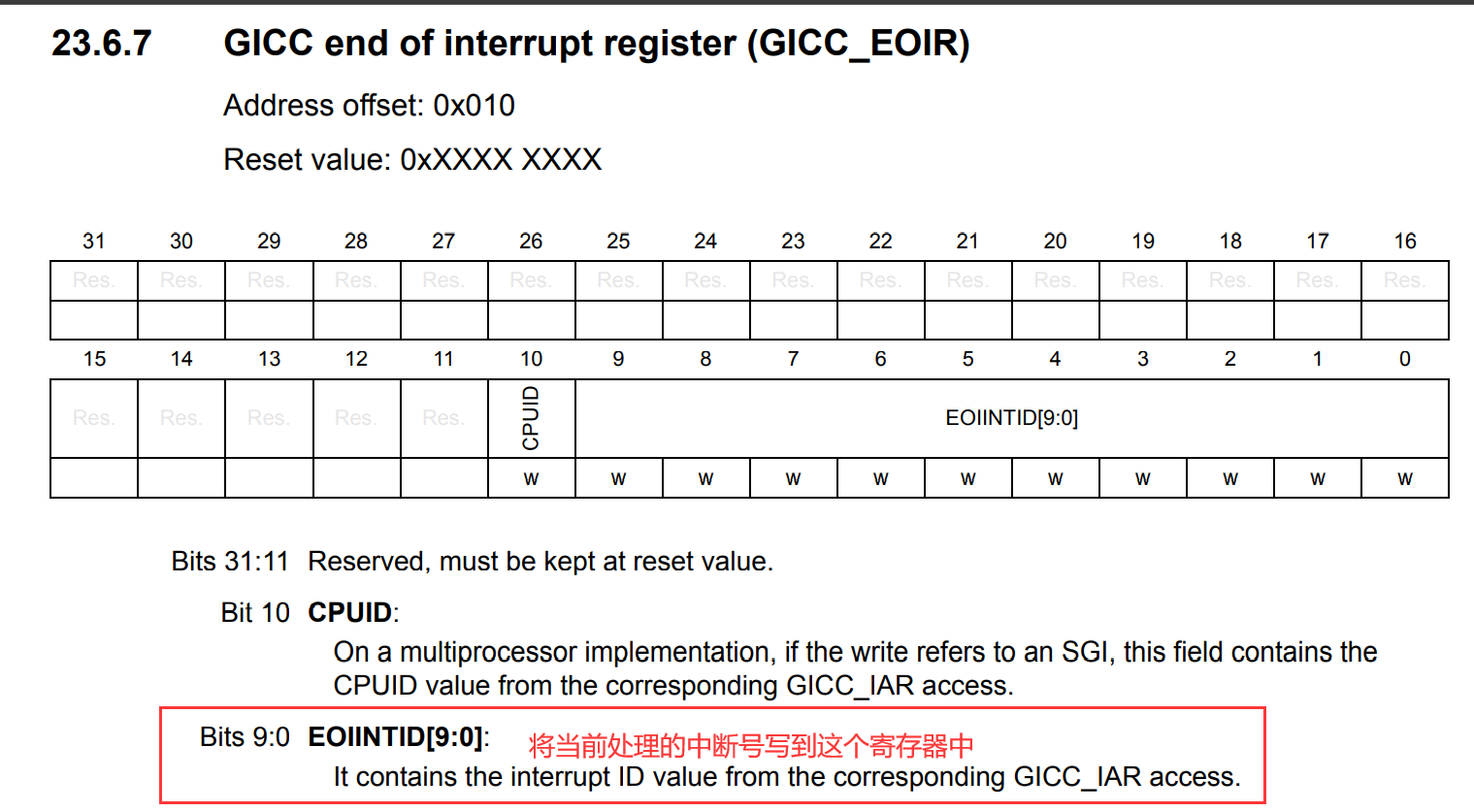

2.5.13 GICC_EOIR :GICC层中断处理结束寄存器

3、编写按键中断的驱动代码

4、代码实现:

4.1interrupt.c

#include "../include/interrupt.h"

void hal_gpio_IT_init(gpio_t *gpios, unsigned int pins)

{

// 1. 使用GPIOF控制器的时钟

RCC->MP_AHB4ENSETR = 0xFF;

// 2. 设置PF9引脚为输入的功能

gpios->MODER &= ~(0x3 << (pins * 2));

}

// KEY1->PF9->EXTI9-->输入事件编号为:9

void hal_exti_IT_init(input_event_t input_event,

gpio_exti_t gpio_exti, trigger_t trigger)

{

// 1. 设置PF9连接到EXTI9上 EXTI_EXTICR3[15:8] = 0x5

switch (input_event / 4)

{

case 0:

EXTI->EXTICR1 &= ~(0xFF << (input_event % 4 * 8));

EXTI->EXTICR1 |= (gpio_exti << (input_event % 4 * 8));

break;

case 1:

EXTI->EXTICR2 &= ~(0xFF << (input_event % 4 * 8));

EXTI->EXTICR2 |= (gpio_exti << (input_event % 4 * 8));

break;

case 2:

EXTI->EXTICR3 &= ~(0xFF << (input_event % 4 * 8));

EXTI->EXTICR3 |= (gpio_exti << (input_event % 4 * 8));

break;

case 3:

EXTI->EXTICR4 &= ~(0xFF << (input_event % 4 * 8));

EXTI->EXTICR4 |= (gpio_exti << (input_event % 4 * 8));

break;

}

// 2. 设置KEY1按键为下降沿检测 EXTI_FTSR1[9] = 0x1

if (trigger != RISING_TRIGGER)

{

EXTI->FTSR1 |= (0x1 << input_event);

}

else

{

EXTI->RTSR1 |= (0x1 << input_event);

}

// 3. 使能EXTI9中断 EXTI_C1IMR1[9] = 0x1

EXTI->C1IMR1 |= (0x1 << input_event);

}

// KEY1->PF9->EXTI9-->中断号为99

void hal_gic_IT_init(unsigned int it_id, unsigned int pri)

{

// 1. 设置GICD层的中断使能 GICD_ISENABLER3[3] = 0x1

GICD->ISENABLER[it_id / 32] |= (0x1 << (it_id % 32));

// 2. 设置GICD层的中断优先级 GICD_IPRIORITYR24[31:27] = 自己定义 范围0-31

GICD->IPRIORITYR[it_id / 4] &= ~(0x1F << (it_id % 4 * 8 + 3));

GICD->IPRIORITYR[it_id / 4] |= (pri << (it_id % 4 * 8 + 3));

// 3. 设置GICD层中断目标分配 GICD_ITARGETSR24[25:24] = 0x1

GICD->ITARGETSR[it_id / 4] &= ~(0x3 << (it_id % 4 * 8));

GICD->ITARGETSR[it_id / 4] |= (0x3 << (it_id % 4 * 8));

// 4. 设置GICD层全局中断使能 GICD_CTLR[0] = 0x1

GICD->CTRL |= (0x1 << 0);

// 5. 设置GICC层中断优先级屏蔽 GICC_PMR[7:3] = 0x1F 自己也可以给其他值

GICC->PMR |= (0x1F << 3);

// 6. 设置GICC层全局中断使能 GICC_CTLR[0] = 0x1

GICC->CTRL |= (0x1 << 0);

}

void hal_clear_exti_IT(input_event_t input_event, trigger_t trigger)

{

if (trigger != RISING_TRIGGER)

{

EXTI->FPR1 |= (0x1 << input_event);

}

else

{

EXTI->RPR1 |= (0x1 << input_event);

}

}

void hal_clear_gic_IT(unsigned int it_id)

{

GICD->ICPENDR[it_id / 32] |= (0x1 << (it_id % 32));

}4.2interrupt.h

#ifndef __INTERRUPT_H__

#define __INTERRUPT_H__

#include "stm32mp1xx_gpio.h"

#include "stm32mp1xx_rcc.h"

#include "stm32mp1xx_exti.h"

#include "stm32mp1xx_gic.h"

#include "gpio.h"

typedef enum

{

INPUT_ENENT_0 = 0,

INPUT_ENENT_1,

INPUT_ENENT_2,

INPUT_ENENT_3,

INPUT_ENENT_4,

INPUT_ENENT_5,

INPUT_ENENT_6,

INPUT_ENENT_7,

INPUT_ENENT_8,

INPUT_ENENT_9,

INPUT_ENENT_10,

INPUT_ENENT_11,

INPUT_ENENT_12,

INPUT_ENENT_13,

INPUT_ENENT_14,

INPUT_ENENT_15,

} input_event_t;

typedef enum

{

RISING_TRIGGER = 0,

FALLING_TRIGGER,

} trigger_t;

typedef enum

{

GPIOA_EXTI = 0,

GPIOB_EXTI,

GPIOC_EXTI,

GPIOD_EXTI,

GPIOE_EXTI,

GPIOF_EXTI,

GPIOG_EXTI,

GPIOH_EXTI,

GPIOI_EXTI,

GPIOJ_EXTI,

} gpio_exti_t;

void hal_gpio_IT_init(gpio_t *gpios, unsigned int pins);

void hal_exti_IT_init(input_event_t input_event,

gpio_exti_t gpio_exti, trigger_t trigger);

void hal_gic_IT_init(unsigned int it_id, unsigned int pri);

void hal_clear_exti_IT(input_event_t input_event, trigger_t trigger);

void hal_clear_gic_IT(unsigned int it_id);

#endif

4.3gpio.h

#ifndef __GPIO_H__

#define __GPIO_H__

#include "stm32mp1xx_gpio.h"

// 1. 封装RCC_MP_AHB4ENSETR寄存器,封装GPIOE,GPIOF寄存器

#define RCC_MP_AHB4ENSETR (*(volatile unsigned int *)0x50000A28)

// 2. 封装LED灯控制的函数

#define GPIO_PIN_0 0U

#define GPIO_PIN_1 1U

#define GPIO_PIN_2 2U

#define GPIO_PIN_3 3U

#define GPIO_PIN_4 4U

#define GPIO_PIN_5 5U

#define GPIO_PIN_6 6U

#define GPIO_PIN_7 7U

#define GPIO_PIN_8 8U

#define GPIO_PIN_9 9U

#define GPIO_PIN_10 10U

#define GPIO_PIN_11 11U

#define GPIO_PIN_12 12U

#define GPIO_PIN_13 13U

#define GPIO_PIN_14 14U

#define GPIO_PIN_15 15U

typedef enum

{

GPIO_INPUT = 0,

GPIO_OUTPUT,

GPIO_AF,

GPIO_ANALOG,

} gpio_mode_t; // gpio引脚模式的枚举类型

typedef enum

{

GPIO_PP = 0,

GPIO_OD,

} gpio_type_t; // gpio引脚的类型

typedef enum

{

GPIO_LOW_SPEED = 0,

GPIO_MEDIUM_SPEED,

GPIO_HIGH_SPEED,

GPIO_VERY_HIGH_SPEED,

} gpio_speed_t; // gpio引脚的速度

typedef enum

{

GPIO_NO_PUPD = 0,

GPIO_UP,

GPIO_DOWN,

} gpio_pupd_t;

typedef enum

{

GPIO_RESET = 0,

GPIO_SET,

} gpio_statues_t;

typedef struct

{

unsigned int pins; // 哪个引脚

gpio_mode_t mode; // 引脚的模式

gpio_type_t type; // 引脚的类型

gpio_speed_t speed; // 引脚的速度

gpio_pupd_t pupd; // 引脚的上拉和下拉

} gpio_init_t; // gpio引脚初始化的结构体

/*

功能:GPIO引脚的初始化

参数:

gpios : 哪个组的gpio引脚

gpio_init : 引脚初始化的结构体

*/

void hal_gpio_init(gpio_t *gpios, gpio_init_t *gpio_init);

/*

功能:写gpio引脚的状态函数

参数:

gpios : 哪个组的gpio引脚

pins : 哪个引脚

statues : 引脚的状态

*/

void hal_gpio_write(gpio_t *gpios, unsigned int pins, gpio_statues_t statues);

/*

功能:读gpio引脚状态的函数

参数:

gpios : 哪个组的gpio引脚

pins : 哪个引脚

返回值:

statues : 引脚的状态

*/

gpio_statues_t hal_gpio_read(gpio_t *gpios, unsigned int pins);

void hal_gpio_toggle(gpio_t *gpios, unsigned int pins);

#endif

4.3stm32mp1xx_gpio.h

#ifndef __STM32MP1xx_GPIO_H__

#define __STM32MP1xx_GPIO_H__

typedef struct {

volatile unsigned int MODER; // 0x00

volatile unsigned int OTYPER; // 0x04

volatile unsigned int OSPEEDR; // 0x08

volatile unsigned int PUPDR; // 0x0C

volatile unsigned int IDR; // 0x10

volatile unsigned int ODR; // 0x14

volatile unsigned int BSRR; // 0x18

volatile unsigned int LCKR; // 0x1C

volatile unsigned int AFRL; // 0x20

volatile unsigned int AFRH; // 0x24

volatile unsigned int BRR; // 0x28

volatile unsigned int res;

volatile unsigned int SECCFGR; // 0x30

}gpio_t;

#define GPIOA ((gpio_t *)0x50002000)

#define GPIOB ((gpio_t *)0x50003000)

#define GPIOC ((gpio_t *)0x50004000)

#define GPIOD ((gpio_t *)0x50005000)

#define GPIOE ((gpio_t *)0x50006000)

#define GPIOF ((gpio_t *)0x50007000)

#define GPIOG ((gpio_t *)0x50008000)

#define GPIOH ((gpio_t *)0x50009000)

#define GPIOI ((gpio_t *)0x5000A000)

#define GPIOJ ((gpio_t *)0x5000B000)

#define GPIOK ((gpio_t *)0x5000C000)

#define GPIOZ ((gpio_t *)0x54004000)

#endif // __STM32MP1xx_GPIO_H__

4.4stm32mp1xx_rcc.h

#ifndef __STM32MP1XX_RCC_H__

#define __STM32MP1XX_RCC_H__

typedef struct {

volatile unsigned int TZCR; // 0x000

volatile unsigned int res1[2]; // 0x004-0x008

volatile unsigned int OCENSETR; // 0x00C

volatile unsigned int OCENCLRR; // 0x010

volatile unsigned int res2[1]; // 0x014

volatile unsigned int HSICFGR; // 0x018

volatile unsigned int CSICFGR; // 0x01C

volatile unsigned int MPCKSELR; // 0x020

volatile unsigned int ASSCKSELR; // 0x024

volatile unsigned int PCK12SELR; // 0x028

volatile unsigned int MPCKDIVR; // 0x02C

volatile unsigned int AXIDIVR; // 0x030

volatile unsigned int res3[2];

volatile unsigned int APB4DIVR; // 0x03C

volatile unsigned int APB5DIVR; // 0x040

volatile unsigned int RTCDIVR; // 0x044

volatile unsigned int MSSCKSELR; // 0x048

volatile unsigned int res4[13];

volatile unsigned int PLL1CR; // 0x080

volatile unsigned int PLL1CFGR1; // 0x084

volatile unsigned int PLL1CFGR2; // 0x088

volatile unsigned int PLL1FRACR; // 0x08C

volatile unsigned int PLL1CSGR; // 0x090

volatile unsigned int PLL2CR; // 0x094

volatile unsigned int PLL2CFGR1; // 0x098

volatile unsigned int PLL2CFGR2; // 0x09C

volatile unsigned int PLL2FRACR; // 0x0A0

volatile unsigned int PLL2CSGR; // 0x0A4

volatile unsigned int res5[6];

volatile unsigned int I2C46CKSELR; // 0x0C0

volatile unsigned int SPI6CKSELR; // 0x0C4

volatile unsigned int UART1CKSELR; // 0x0C8

volatile unsigned int RNG1CKSELR; // 0x0CC

volatile unsigned int CPERCKSELR; // 0x0D0

volatile unsigned int STGENCKSELR; // 0x0D4

volatile unsigned int DDRITFCR; // 0x0D8

volatile unsigned int res6[9];

volatile unsigned int MP_BOOTCR; // 0x100

volatile unsigned int MP_SREQSETR; // 0x104

volatile unsigned int MP_SREQCLRR; // 0x108

volatile unsigned int MP_GCR; // 0x10C

volatile unsigned int MP_APRSTCR; // 0x110

volatile unsigned int MP_APRSTSR; // 0x114

volatile unsigned int res7[10];

volatile unsigned int BDCR; // 0x140

volatile unsigned int RDLSICR; // 0x144

volatile unsigned int res8[14];

volatile unsigned int APB4RSTSETR; // 0x180

volatile unsigned int APB4RSTCLRR; // 0x184

volatile unsigned int APB5RSTSETR; // 0x188

volatile unsigned int APB5RSTCLRR; // 0x18C

volatile unsigned int AHB5RSTSETR; // 0x190

volatile unsigned int AHB5RSTCLRR; // 0x194

volatile unsigned int AHB6RSTSETR; // 0x198

volatile unsigned int AHB6RSTCLRR; // 0x19C

volatile unsigned int TZAHB6RSTSELR;// 0x1A0

volatile unsigned int TZAHB6RSTCLRR;// 0x1A4

volatile unsigned int res9[22];

volatile unsigned int MP_APB4ENSETR;// 0x200

volatile unsigned int MP_APB4ENCLRR;// 0x204

volatile unsigned int MP_APB5ENSETR;// 0x208

volatile unsigned int MP_APB5ENCLRR;// 0x20C

volatile unsigned int MP_AHB5ENSETR;// 0x210

volatile unsigned int MP_AHB5ENCLRR;// 0x214

volatile unsigned int MP_AHB6ENSETR;// 0x218

volatile unsigned int MP_AHB6ENCLRR;// 0x21C

volatile unsigned int MP_TZAHB6ENSELR;// 0x220

volatile unsigned int MP_TZAHB6ENCLRR;// 0x224

volatile unsigned int res10[22];

volatile unsigned int MC_APB4ENSETR; // 0x280

volatile unsigned int MC_APB4ENCLRR; // 0x284

volatile unsigned int MC_APB5ENSETR; // 0x288

volatile unsigned int MC_APB5ENCLRR; // 0x28C

volatile unsigned int MC_AHB5ENSETR; // 0x290

volatile unsigned int MC_AHB5ENCLRR; // 0x294

volatile unsigned int MC_AHB6ENSETR; // 0x298

volatile unsigned int MC_AHB6ENCLRR; // 0x29C

volatile unsigned int res11[24];

volatile unsigned int MP_APB4LPENSETR; // 0x300

volatile unsigned int MP_APB4LPENCLRR; // 0x304

volatile unsigned int MP_APB5LPENSETR; // 0x308

volatile unsigned int MP_APB5LPENCLRR; // 0x30C

volatile unsigned int MP_AHB5LPENSETR; // 0x310

volatile unsigned int MP_AHB5LPENCLRR; // 0x314

volatile unsigned int MP_AHB6LPENSETR; // 0x318

volatile unsigned int MP_AHB6LPENCLRR; // 0x31C

volatile unsigned int MP_TZAHB6LPENSETR; // 0x320

volatile unsigned int MP_TZAHB6LPENCLRR; // 0x324

volatile unsigned int res12[22];

volatile unsigned int MC_APB4LPENSETR; // 0x380

volatile unsigned int MC_APB4LPENCLRR; // 0x384

volatile unsigned int MC_APB5LPENSETR; // 0x388

volatile unsigned int MC_APB5LPENCLRR; // 0x38C

volatile unsigned int MC_AHB5LPENSETR; // 0x390

volatile unsigned int MC_AHB5LPENCLRR; // 0x394

volatile unsigned int MC_AHB6LPENSETR; // 0x398

volatile unsigned int MC_AHB6LPENCLRR; // 0x39C

volatile unsigned int res13[24];

volatile unsigned int BR_RSTSCLRR; // 0x400

volatile unsigned int MP_GRSTCSETR; // 0x404

volatile unsigned int MP_RSTSR; // 0x408

volatile unsigned int MP_IWDGFZSETR; // 0x40C

volatile unsigned int MP_IWDGFZCLRR; // 0x410

volatile unsigned int MP_CIER; // 0x414

volatile unsigned int MP_CIFR; // 0x418

volatile unsigned int PWRLPDLYCR; // 0x41C

volatile unsigned int MP_RSTSS; // 0x420

volatile unsigned int res14[247];

volatile unsigned int MCO1CFGR; // 0x800

volatile unsigned int MCO2CFGR; // 0x804

volatile unsigned int OCRDYR; // 0x808

volatile unsigned int DBGCFGR; // 0x80C

volatile unsigned int res15[4];

volatile unsigned int RCK3SELR; // 0x820

volatile unsigned int RCK4SELR; // 0x824

volatile unsigned int TIMG1PRER; // 0x828

volatile unsigned int TIMG2PRER; // 0x82C

volatile unsigned int MCUDIVR; // 0x830

volatile unsigned int APB1DIVR; // 0x834

volatile unsigned int APB2DIVR; // 0x838

volatile unsigned int APB3DIVR; // 0x83C

volatile unsigned int res16[16];

volatile unsigned int PLL3CR; // 0x880

volatile unsigned int PLL3CFGR1; // 0x884

volatile unsigned int PLL3CFGR2; // 0x888

volatile unsigned int PLL3FRACR; // 0x88C

volatile unsigned int PLL3CSGR; // 0x890

volatile unsigned int PLL4CR; // 0x894

volatile unsigned int PLL4CFGR1; // 0x898

volatile unsigned int PLL4CFGR2; // 0x89C

volatile unsigned int PLL4FRACR; // 0x8A0

volatile unsigned int PLL4CSGR; // 0x8A4

volatile unsigned int res17[6];

volatile unsigned int I2C12CKSELR; // 0x8C0

volatile unsigned int I2C35CKSELR; // 0x8C4

volatile unsigned int SAI1CKSELR; // 0x8C8

volatile unsigned int SAI2CKSELR; // 0x8CC

volatile unsigned int SAI3CKSELR; // 0x8D0

volatile unsigned int SAI4CKSELR; // 0x8D4

volatile unsigned int SPI2S1CKSELR; // 0x8D8

volatile unsigned int SPI2S23CKSELR; // 0x8DC

volatile unsigned int SPI45CKSELR; // 0x8E0

volatile unsigned int UART6CKSELR; // 0x8E4

volatile unsigned int UART24CKSELR; // 0x8E8

volatile unsigned int UART35CKSELR; // 0x8EC

volatile unsigned int UART78CKSELR; // 0x8F0

volatile unsigned int SDMMC12CKSELR; // 0x8F4

volatile unsigned int SDMMC3CKSELR; // 0x8F8

volatile unsigned int ETHCKSELR; // 0x8FC

volatile unsigned int QSPICKSELR; // 0x900

volatile unsigned int FMCCKSELR; // 0x904

volatile unsigned int res18[1];

volatile unsigned int FDCANCKSELR; // 0x90C

volatile unsigned int res19[1];

volatile unsigned int SPDIFCKSELR; // 0x914

volatile unsigned int CECCKSELR; // 0x918

volatile unsigned int USBCKSELR; // 0x91C

volatile unsigned int RNG2CKSELR; // 0x920

volatile unsigned int DSICKSELR; // 0x924

volatile unsigned int ADCCKSELR; // 0x928

volatile unsigned int LPTIM45CKSELR; // 0x92C

volatile unsigned int LPTIM23CKSELR; // 0x930

volatile unsigned int LPTIM1CKSELR; // 0x934

volatile unsigned int res20[18];

volatile unsigned int APB1RSTSETR; // 0x980

volatile unsigned int APB1RSTCLRR; // 0x984

volatile unsigned int APB2RSTSETR; // 0x988

volatile unsigned int APB2RSTCLRR; // 0x98C

volatile unsigned int APB3RSTSETR; // 0x990

volatile unsigned int APB3RSTCLRR; // 0x994

volatile unsigned int AHB2RSTSETR; // 0x998

volatile unsigned int AHB2RSTCLRR; // 0x99C

volatile unsigned int AHB3RSTSETR; // 0x9A0

volatile unsigned int AHB3RSTCLRR; // 0x9A4

volatile unsigned int AHB4RSTSETR; // 0x9A8

volatile unsigned int AHB4RSTCLRR; // 0x9AC

volatile unsigned int res21[20];

volatile unsigned int MP_APB1ENSETR; // 0xA00

volatile unsigned int MP_APB1ENCLRR; // 0xA04

volatile unsigned int MP_APB2ENSETR; // 0xA08

volatile unsigned int MP_APB2ENCLRR; // 0xA0C

volatile unsigned int MP_APB3ENSETR; // 0xA10

volatile unsigned int MP_APB3ENCLRR; // 0xA14

volatile unsigned int MP_AHB2ENSETR; // 0xA18

volatile unsigned int MP_AHB2ENCLRR; // 0xA1C

volatile unsigned int MP_AHB3ENSETR; // 0xA20

volatile unsigned int MP_AHB3ENCLRR; // 0xA24

volatile unsigned int MP_AHB4ENSETR; // 0xA28

volatile unsigned int MP_AHB4ENCLRR; // 0xA2C

volatile unsigned int res22[2];

volatile unsigned int MP_MLAHBENSETR; // 0xA38

volatile unsigned int MP_MLAHBENCLRR; // 0xA3C

volatile unsigned int res23[16];

volatile unsigned int MC_APB1ENSETR; // 0xA80

volatile unsigned int MC_APB1ENCLRR; // 0xA84

volatile unsigned int MC_APB2ENSETR; // 0xA88

volatile unsigned int MC_APB2ENCLRR; // 0xA8C

volatile unsigned int MC_APB3ENSETR; // 0xA90

volatile unsigned int MC_APB3ENCLRR; // 0xA94

volatile unsigned int MC_AHB2ENSETR; // 0xA98

volatile unsigned int MC_AHB2ENCLRR; // 0xA9C

volatile unsigned int MC_AHB3ENSETR; // 0xAA0

volatile unsigned int MC_AHB3ENCLRR; // 0xAA4

volatile unsigned int MC_AHB4ENSETR; // 0xAA8

volatile unsigned int MC_AHB4ENCLRR; // 0xAAC

volatile unsigned int MC_AXIMENSETR; // 0xAB0

volatile unsigned int MC_AXIMENCLRR; // 0xAB4

volatile unsigned int MC_MLAHBENSETR; // 0xAB8

volatile unsigned int MC_MLAHBENCLRR; // 0xABC

volatile unsigned int res24[16];

volatile unsigned int MP_APB1LPENSETR; // 0xB00

volatile unsigned int MP_APB1LPENCLRR; // 0xB04

volatile unsigned int MP_APB2LPENSETR; // 0xB08

volatile unsigned int MP_APB2LPENCLRR; // 0xB0C

volatile unsigned int MP_APB3LPENSETR; // 0xB10

volatile unsigned int MP_APB3LPENCLRR; // 0xB14

volatile unsigned int MP_AHB2LPENSETR; // 0xB18

volatile unsigned int MP_AHB2LPENCLRR; // 0xB1C

volatile unsigned int MP_AHB3LPENSETR; // 0xB20

volatile unsigned int MP_AHB3LPENCLRR; // 0xB24

volatile unsigned int MP_AHB4LPENSETR; // 0xB28

volatile unsigned int MP_AHB4LPENCLRR; // 0xB2C

volatile unsigned int MP_AXIMLPENSETR; // 0xB30

volatile unsigned int MP_AXIMLPENCLRR; // 0xB34

volatile unsigned int MP_MLAHBLPENSETR; // 0xB38

volatile unsigned int MP_MLAHBLPENCLRR; // 0xB3C

volatile unsigned int res25[16];

volatile unsigned int MC_APB1LPENSETR; // 0xB80

volatile unsigned int MC_APB1LPENCLRR; // 0xB84

volatile unsigned int MC_APB2LPENSETR; // 0xB88

volatile unsigned int MC_APB2LPENCLRR; // 0xB8C

volatile unsigned int MC_APB3LPENSETR; // 0xB90

volatile unsigned int MC_APB3LPENCLRR; // 0xB94

volatile unsigned int MC_AHB2LPENSETR; // 0xB98

volatile unsigned int MC_AHB2LPENCLRR; // 0xB9C

volatile unsigned int MC_AHB3LPENSETR; // 0xBA0

volatile unsigned int MC_AHB3LPENCLRR; // 0xBA4

volatile unsigned int MC_AHB4LPENSETR; // 0xBA8

volatile unsigned int MC_AHB4LPENCLRR; // 0xBAC

volatile unsigned int MC_AXIMLPENSETR; // 0xBB0

volatile unsigned int MC_AXIMLPENCLRR; // 0xBB4

volatile unsigned int MC_MLAHBLPENSETR; // 0xBB8

volatile unsigned int MC_MLAHBLPENCLRR; // 0xBBC

volatile unsigned int res26[16];

volatile unsigned int MC_RSTSCLRR; // 0xC00

volatile unsigned int res27[4];

volatile unsigned int MC_CIER; // 0xC14

volatile unsigned int MC_CIFR; // 0xC18

volatile unsigned int res28[246];

volatile unsigned int VERR; // 0xFF4

volatile unsigned int IDR; // 0xFF8

volatile unsigned int SIDR; // 0xFFC

}rcc_t;

#define RCC ((rcc_t *)0x50000000)

#endif // __STM32MP1XX_RCC_H__

4.5stm32mp1xx_exti.h

#ifndef __STM32MP1XX_EXTI_H__

#define __STM32MP1XX_EXTI_H__

typedef struct{

volatile unsigned int RTSR1; // EXTI rising trigger selection register

volatile unsigned int FTSR1; // EXTI falling trigger selection register

volatile unsigned int SWIER1; // EXTI software interrupt event register

volatile unsigned int RPR1; // EXTI rising edge pending register

volatile unsigned int FPR1; // EXTI falling edge pending register

volatile unsigned int TZENR1; // EXTI TrustZone enable register

volatile unsigned int RES1[2];

volatile unsigned int RTSR2; // EXTI rising trigger selection register

volatile unsigned int FTSR2; // EXTI falling trigger selection register

volatile unsigned int SWIER2; // EXTI software interrupt event register

volatile unsigned int RPR2; // EXTI rising edge pending register

volatile unsigned int FPR2; // EXTI falling edge pending register

volatile unsigned int TZENR2; // EXTI TrustZone enable register

volatile unsigned int RES2[2];

volatile unsigned int RTSR3; // EXTI rising trigger selection register

volatile unsigned int FTSR3; // EXTI falling trigger selection register

volatile unsigned int SWIER3; // EXTI software interrupt event register

volatile unsigned int RPR3; // EXTI rising edge pending register

volatile unsigned int FPR3; // EXTI falling edge pending register

volatile unsigned int TZENR3; // EXTI TrustZone enable register

volatile unsigned int RES3[2];

volatile unsigned int EXTICR1; // EXTI external interrupt selection register 1

volatile unsigned int EXTICR2; // EXTI external interrupt selection register 2

volatile unsigned int EXTICR3; // EXTI external interrupt selection register 3

volatile unsigned int EXTICR4; // EXTI external interrupt selection register 4

volatile unsigned int RES4[4];

volatile unsigned int C1IMR1; // EXTI CPU1 wakeup with interrupt mask register

volatile unsigned int C1EMR1; // EXTI CPU1 wakeup with event mask register

volatile unsigned int RES5[2];

volatile unsigned int C1IMR2; // EXTI CPU1 wakeup with interrupt mask register

volatile unsigned int C1EMR2; // EXTI CPU1 wakeup with event mask register

volatile unsigned int RES6[2];

volatile unsigned int C1IMR3; // EXTI CPU1 wakeup with interrupt mask register

volatile unsigned int C1EMR3; // EXTI CPU1 wakeup with event mask register

volatile unsigned int RES7[6];

volatile unsigned int C2IMR1; // EXTI CPU2 wakeup with interrupt mask register

volatile unsigned int C2EMR1; // EXTI CPU2 wakeup with event mask register

volatile unsigned int RES8[2];

volatile unsigned int C2IMR2; // EXTI CPU2 wakeup with interrupt mask register

volatile unsigned int C2EMR2; // EXTI CPU2 wakeup with event mask register

volatile unsigned int RES9[2];

volatile unsigned int C2IMR3; // EXTI CPU2 wakeup with interrupt mask register

volatile unsigned int C2EMR3; // EXTI CPU2 wakeup with event mask register

volatile unsigned int RES10[2];

}exti_t;

#define EXTI ((exti_t*)0x5000D000)

#endif //__STM32MP1XX_EXTI_H__

4.6stm32mp1xx_gic.h

#ifndef __STM32MP1XX_GIC_H__

#define __STM32MP1XX_GIC_H__

typedef struct {

volatile unsigned int CTRL;

volatile unsigned int TYPER;

volatile unsigned int IIDR;

volatile unsigned int RES1[29];

volatile unsigned int IGROUPR[9];

volatile unsigned int RES2[23];

volatile unsigned int ISENABLER[9];

volatile unsigned int RES3[23];

volatile unsigned int ICENABLER[9];

volatile unsigned int RES4[23];

volatile unsigned int ISPENDR[9];

volatile unsigned int RES5[23];

volatile unsigned int ICPENDR[9];

volatile unsigned int RES6[23];

volatile unsigned int ISACTIVER[9];

volatile unsigned int RES7[23];

volatile unsigned int ICACTIVER[9];

volatile unsigned int RES8[23];

volatile unsigned int IPRIORITYR[72];

volatile unsigned int RES9[184];

volatile unsigned int ITARGETSR[72];

volatile unsigned int RES10[184];

volatile unsigned int ICFGR[18];

volatile unsigned int RES11[46];

}gicd_t;

#define GICD ((gicd_t*)0xA0021000)

typedef struct {

volatile unsigned int CTRL;

volatile unsigned int PMR;

volatile unsigned int BRR;

volatile unsigned int IAR;

volatile unsigned int EOIR;

volatile unsigned int RPR;

volatile unsigned int HPPIR;

volatile unsigned int ABPR;

volatile unsigned int AIAR;

volatile unsigned int AEOIR;

volatile unsigned int AHPPIR;

volatile unsigned int RES1[41];

volatile unsigned int APR0;

volatile unsigned int RES2[3];

volatile unsigned int NSAPR0;

volatile unsigned int RES3[6];

volatile unsigned int IIDR;

volatile unsigned int RES4[960];

volatile unsigned int DIRDIR;

}gicc_t;

#define GICC ((gicc_t*)0xA0022000)

#endif // __STM32MP1XX_GIC_H__

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?