一、为什么要讨论信号完整性的问题

在低速数字设计中,功能实现与否基本上不需要关注PCB上的走线,当时钟频率超过100MHz或者上升边小于1ns,就要考虑互连线对数字信号电压电流波形的影响。所造成的不良影响体现在以下三个方面:

1、 时序。

2、 噪声。

3、 电磁干扰。

而对于第二项噪声,又分为以下的四个方面:

1、 单一网络信号完整性。

2、 两个或多个网络间串扰。

3、 电源和地分配中的轨道塌陷。

4、 来自整个系统的电磁干扰和辐射。

二、如何判断需要进行信号完整性考虑的重要信号线

1、对于这个问题,《AT91-AN02: Signal Integrity and AT91 Products》4.1 Signal Slope and Critical Trace Length Criteria中给出如下论证:

• A propagation delay on digital trace < 16% of the TF provides a “clean” digital signal trace in terms of being without reflection. But we cannot say there will not be overshoot and ringing

when that trace is connected to a capacitive load (it is usually the case). We will examine this

case when we present the Series Termination method.

• A propagation delay on digital trace equal to 30% of the TF causes some small ringing on the

digital signal trace.

• A propagation delay on digital trace equal to 40% of the TF causes some ringing on the digital

signal trace.

• A propagation delay on the digital trace up to 50% of the TF can be acceptable.

You must not forget that the 50% criteria can be acceptable for the intrinsic digital signal but not for the whole application, nor to be successful for EMC certification. And inversely, 16% will be the best but that is going to compel you to add termination resistors on a lot of traces. This

choice is fully arbitrary.

Note:

Often this 50% is assumed to be the limit, over which a trace becomes a distributed system.

2、在《高速电路设计实践》1.2节中描述了三步:获得有效频率Fknee和走线长度L;利用Fknee计算出信号的有效波长;判断L和1/6有效波长之间的关系,若L大于1/6有效波长,就是高速信号。

说明:本判断仅限于1GHz以下的信号。

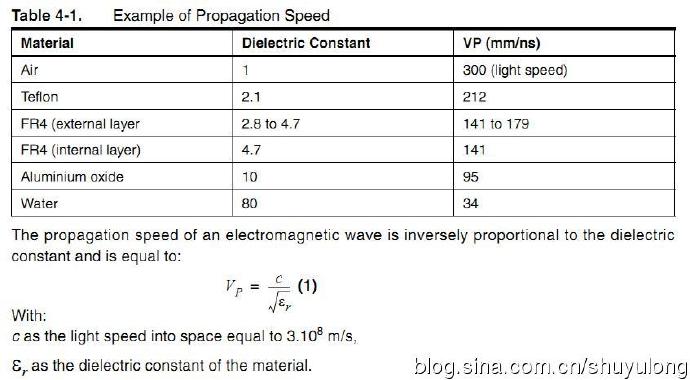

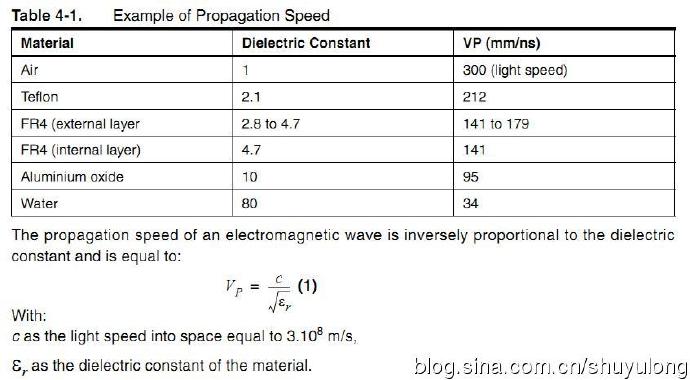

计算走线延时所需要的信号传播速度:

Remark:

The external layers always have one side where the dielectric constant is the Air and the other is FR4 (true for both external sides). This is why external layers are used for critical lines, the propagation speed is higher on external layers than on inner layers.

三、端接

1、器件输出驱动器阻抗:通过分压定律求解。

2、互连线特性阻抗:polar软件或者其他公式等方法。

3、端接方式:

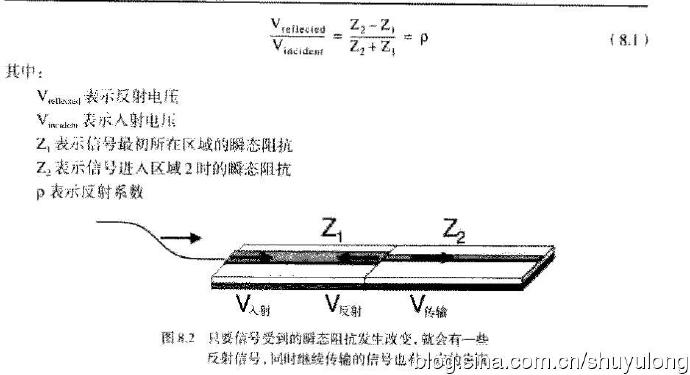

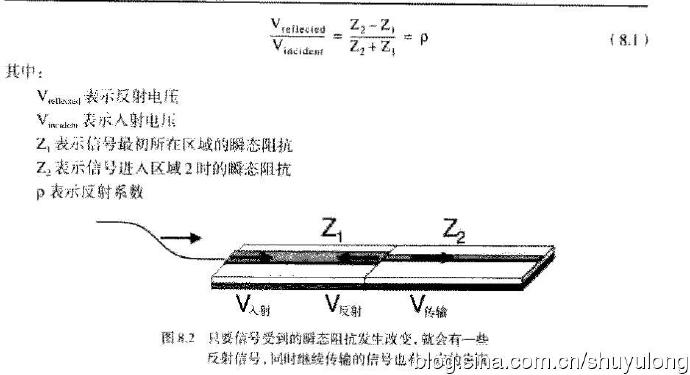

将反射系数控制为0,是端接的目的。

发送端串联匹配:适合点到点互联线;电阻尽量靠近源端放置;选值为Rs = (Zo - Zs)。

接收端并联匹配:不会影响边沿速率;功耗大,影响判决门限。

接收端阻容并联匹配:功耗低;要考虑rc时间常数大于信号周期。

戴维南匹配:

接收端二极管匹配:

228

228

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?