上一章节讲了CPU和外设的Memory Map,现在是时候实战AXI接口扩展外设。

作为一个攻城狮可不能边看别人操作边流口水,喜欢的东西就要挽起袖子自己上。

先从点个灯开始吧,接触硬件的人点个灯和编程界的hello world同样具有划时代的意义。一起来看一下操作步骤:

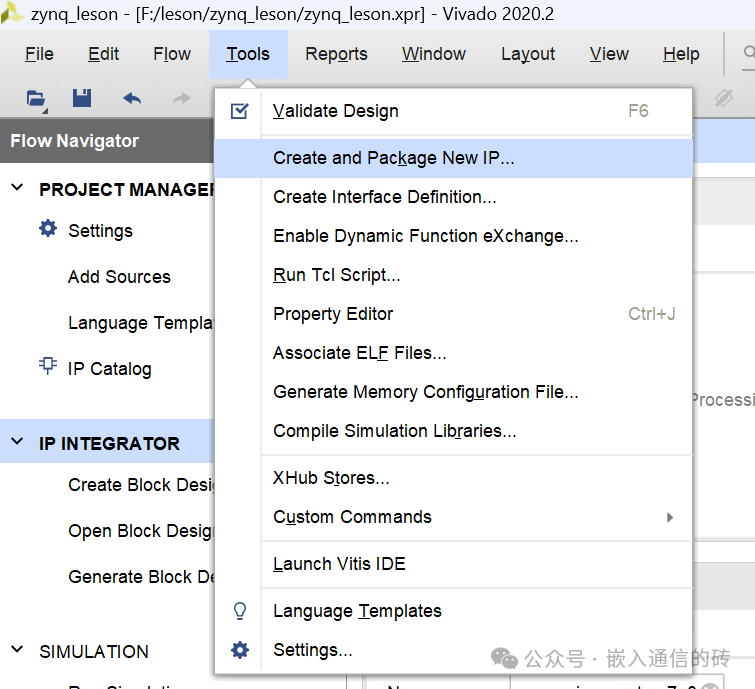

第一步选Create and Package New IP,快速创建AXI外设的机关就藏在这里面

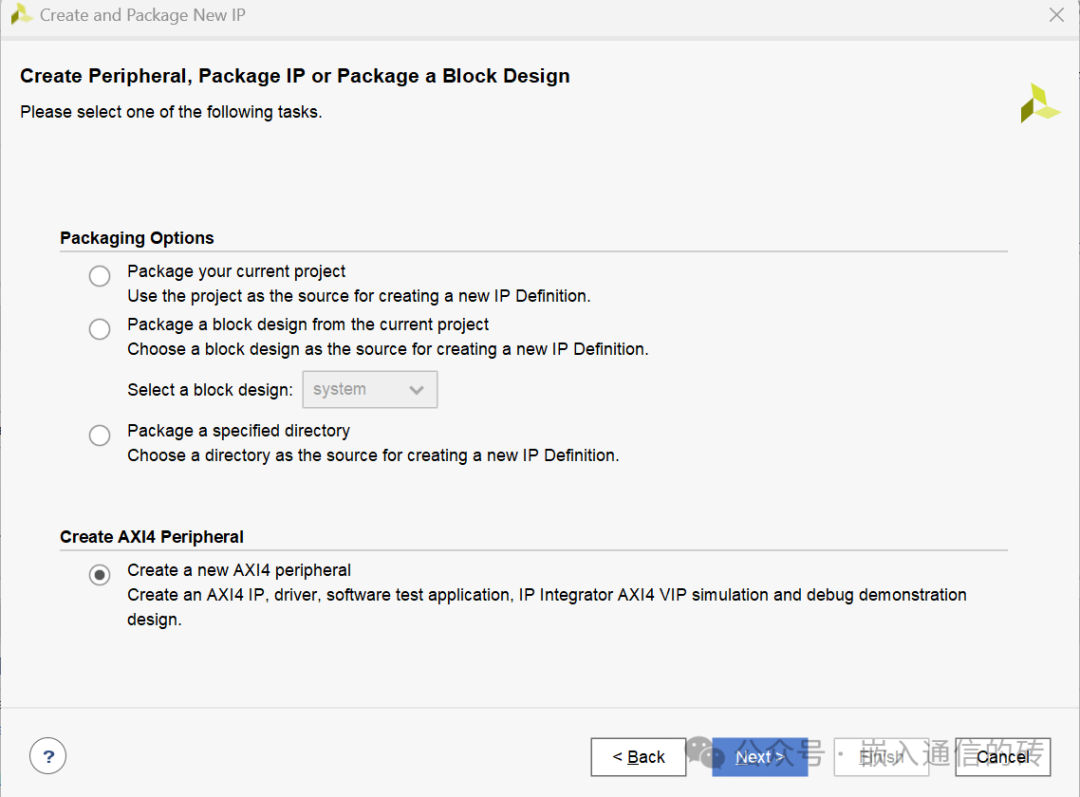

第二步 英语好的可以看下介绍,像砖头这种英语不好的就直接点NEXT。

第三步 看名字就知道选Create a new AXI4 peripheral,创建一个AXI4接口的外设。

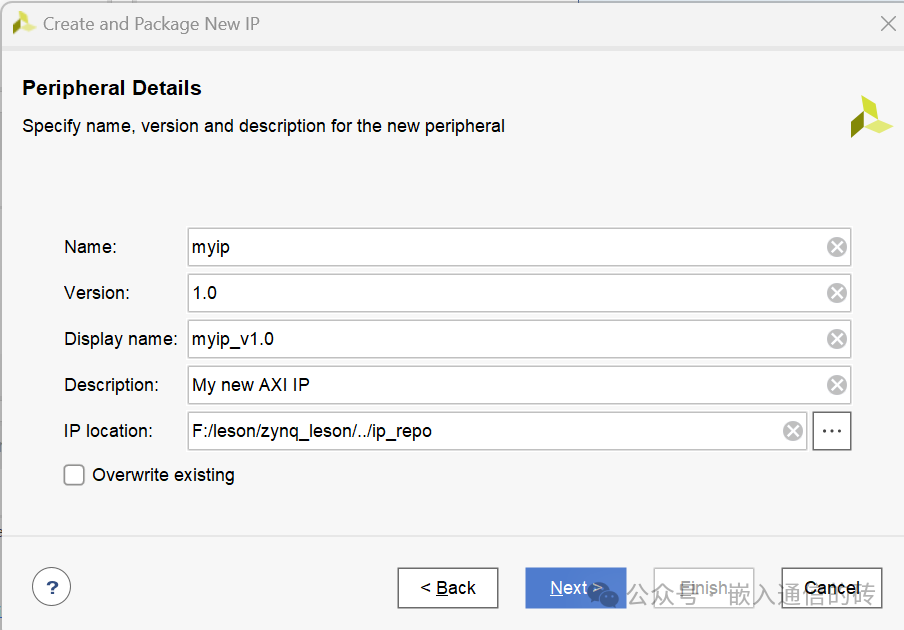

第四步 选择创建的文件要保存位置,各位看客自便。

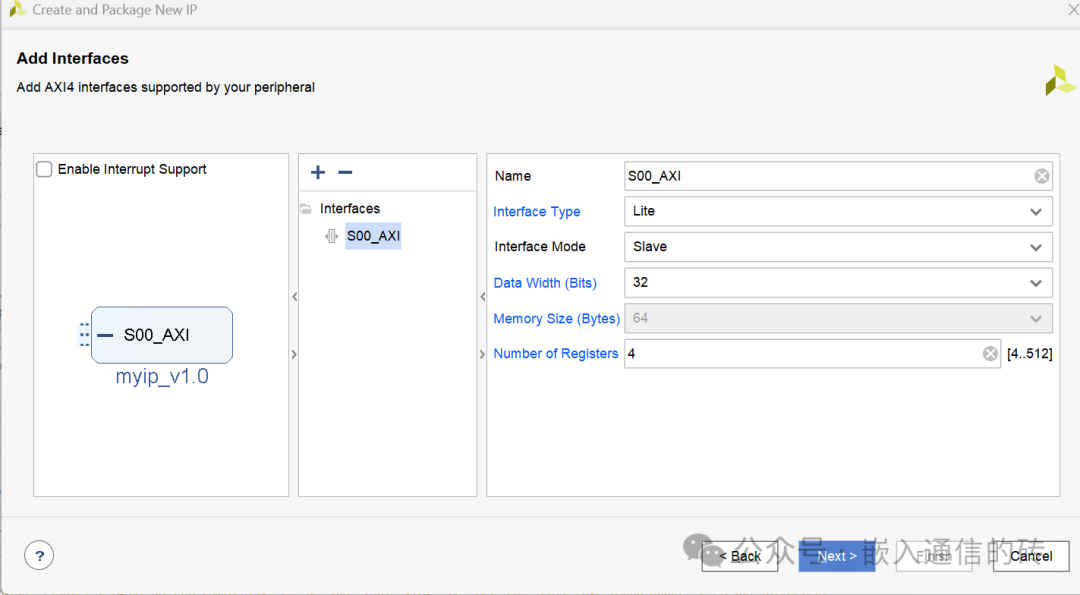

第五步 配置AXI接口参数

第六步 选择Edit IP,接下来需要使用这里面的源码

第七步 myip_v1_0_S00_AXI.v就是一个最基本的AXI-LITE接口外设。

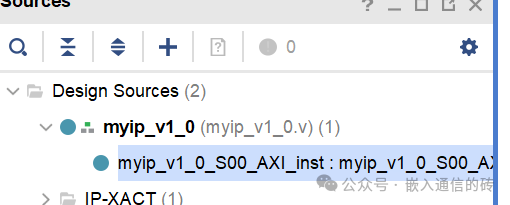

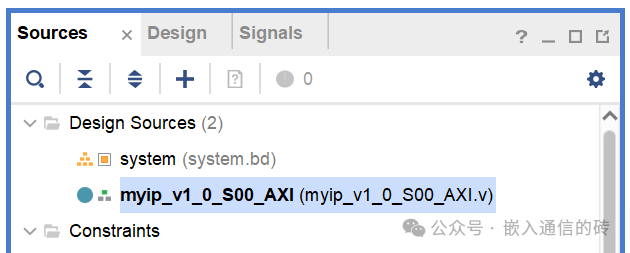

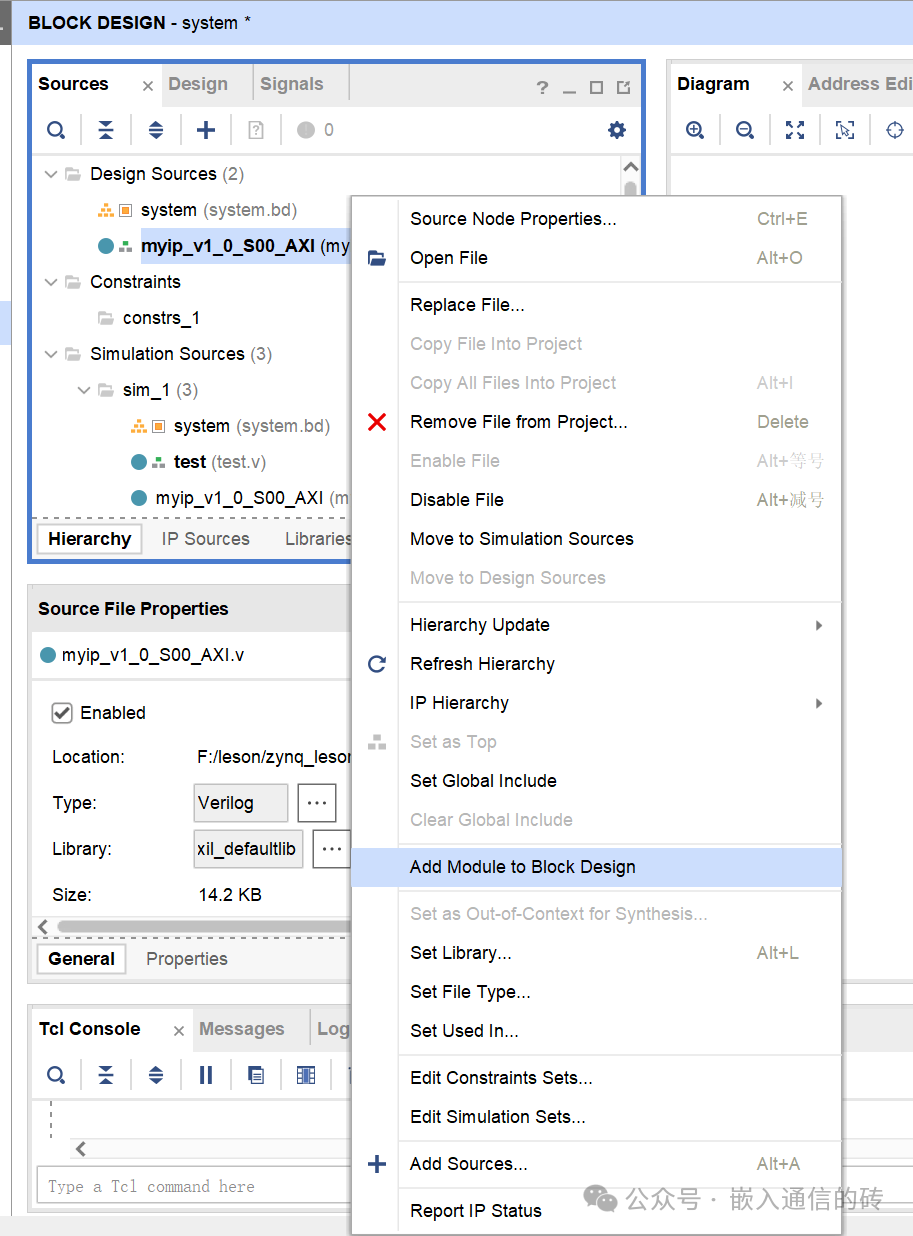

第8步 另外新建一个ZYNQ最小系统工程(详细步骤参考开发板教程,此处省略),然后将第七步的myip_v1_0_S00_AXI.v文件添加到此工程里。完成后如下图:

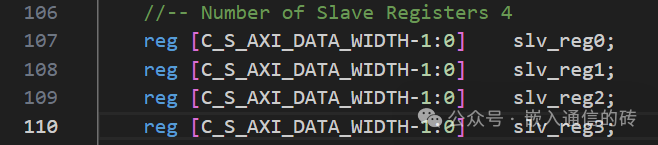

第九步 打开myip_v1_0_S00_AXI.v文件,这个文件很容易理解,就是实现AXI总线读写slv_reg0-slv_reg3寄存器的功能。

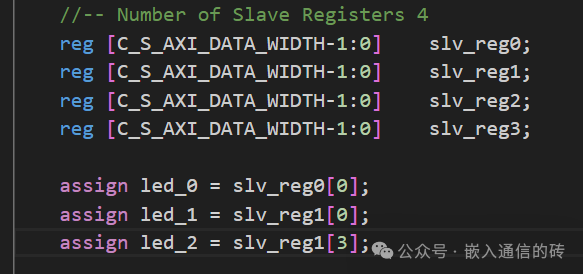

第十步 底层逻辑电路是连接软件和硬件的桥梁,FPGA最终和硬件的桥梁就是顶层Module定义的output/input信号,output对应的引脚输出高低电平,input获取对应引脚的高低电平(FPGA工程师:这我熟)。假设我现在有3个LED灯,要控制LED灯,那我们只需要把这3个LED灯对应的输出接口和reg寄存器的值关联起来即可。

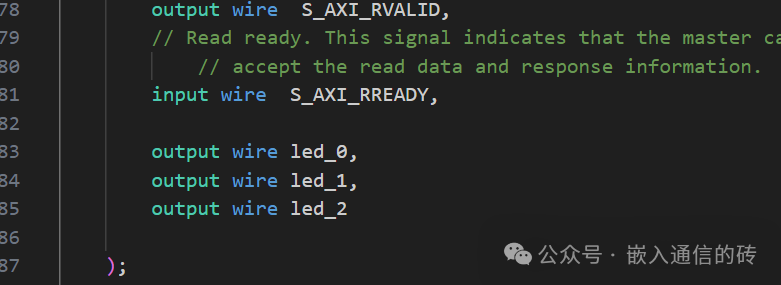

别忘了在port部分导出接口:

第十二步 在myip_v1_0_S00_AXI.v文件上右击,选择Add Module to Block Design

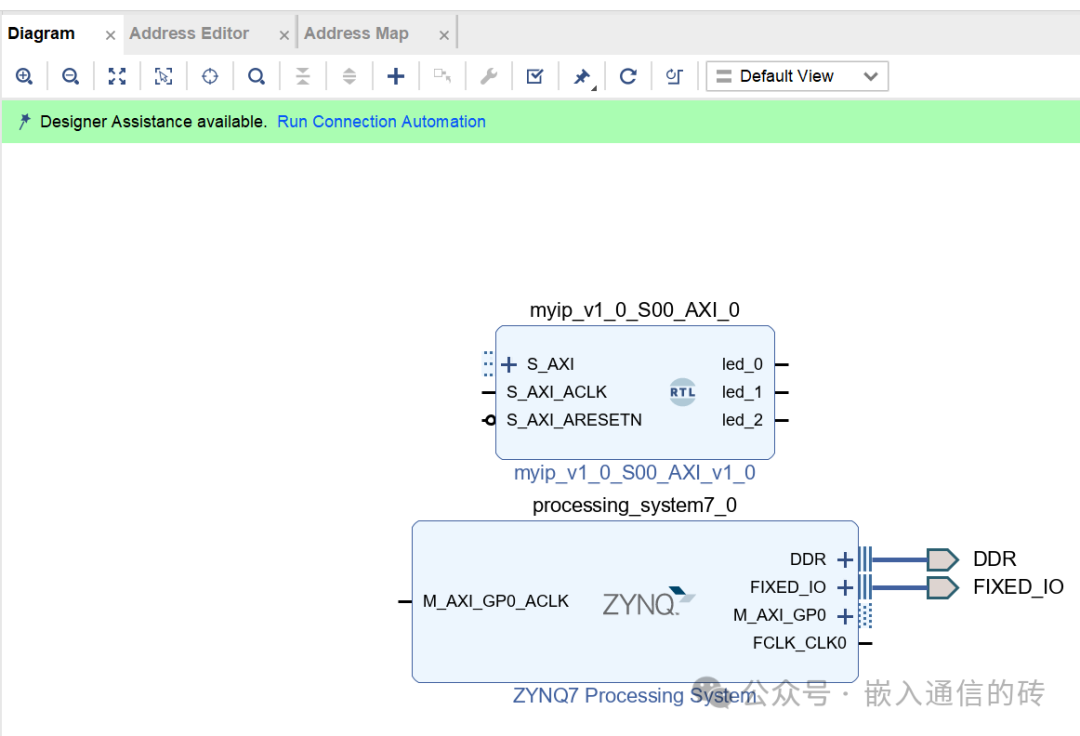

第十三步 点击Run Connection Automation ,自动完成Block Design设计

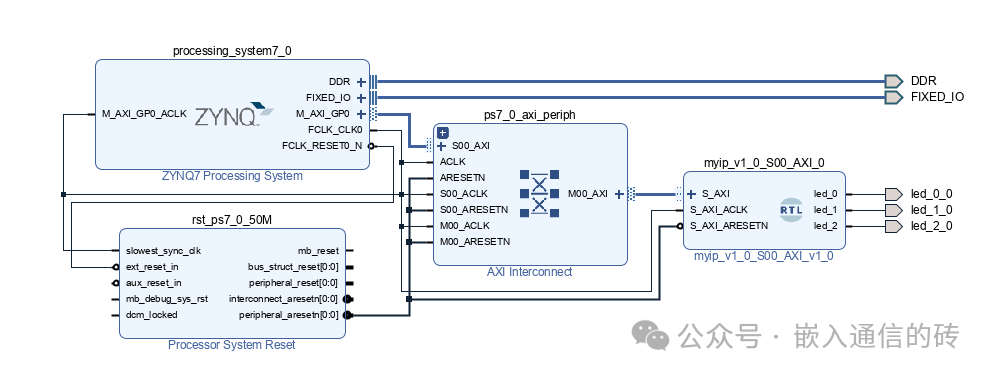

然后在myip_v1_0_S00_AXI_V1_0上右击并选择Make Extern导出led引脚,完成后如下图:

这样就给PS添加了一个自定义的外设,这个外设有3个输出接口(这个外设真是盖中盖)。后面生成顶层文件、bit文件等常规操作步骤省略。

本章节描述了如何给PS添加一个自定义外设在PL端的实现步骤,下一节讲如何在PS端使用这个外设。

公众号:嵌入通信的砖 每周更新嵌入式技术

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?