先回忆下上两章讲的C语言底层在CPU里的实现,仔细理解地址+数据在CPU里的实现方式。

回忆虽然美好,但回忆的目的是让未来的路越走越宽。继续拥抱未来吧。

我们把一颗处理器分成负责算逻辑处理和算术运算的CPU(同之前章节,这里的CPU指的是ARM内核)和负责实现具体功能的外设部分。内核只是一颗处理器的一部分,同一个内核不同的厂家加上不同的外设可以做成不同的处理器,就像LPC4357和STM32F407都是基于coretx-M4内核,但是是两个完全不同的处理器。

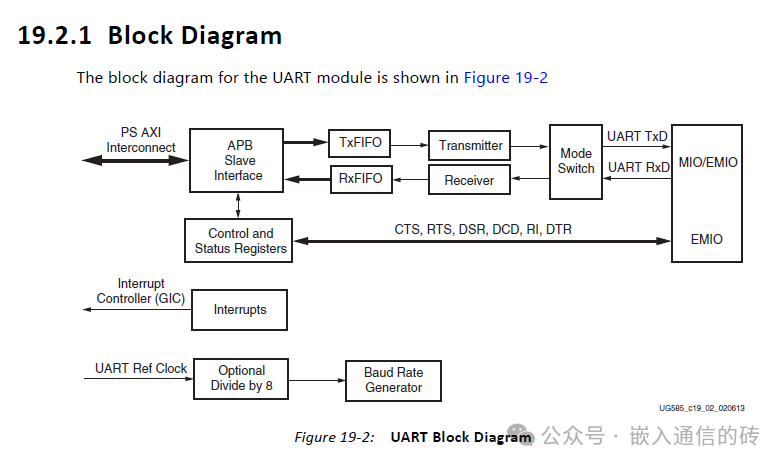

如下图是ZYNQ里串口外设的功能框图。PS AXI Interconnect就是上一章节讲过的Central Interconnect,CPU通过它来访问和控制串口这个外设。

ZYNQ里有很多这种类似的外设。那么多外设,CPU怎么分的清谁谁谁?聪明的你肯定想到了靠地址来区分。

就像LINUX将所有东西当成文件处理,CPU将所有挂载的外设、内存等都按照地址+数据的方式处理。每一个挂载的外设或内存都有独立的地址及占用空间,它们之间不能重叠。

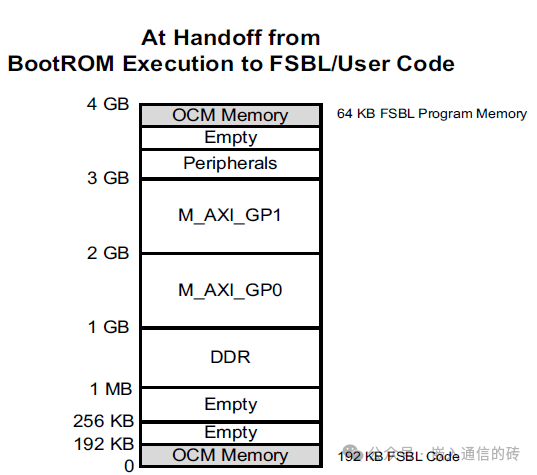

当然了CPU地址不是无限的,32位CPU理论上可访问空间是2^32 = 4GB。分配地址的时候不要搞得像东拼西凑的PDD货,看下ZYNQ里面给CPU做的memory map。

从上图可以看出来,CPU预分配的DDR内存地址是1GB,也就是说PS端的DDR控制器支持的最大内存是1GB,你原理图上给个4GB的DDR除了拉动GDP外没其它作用。

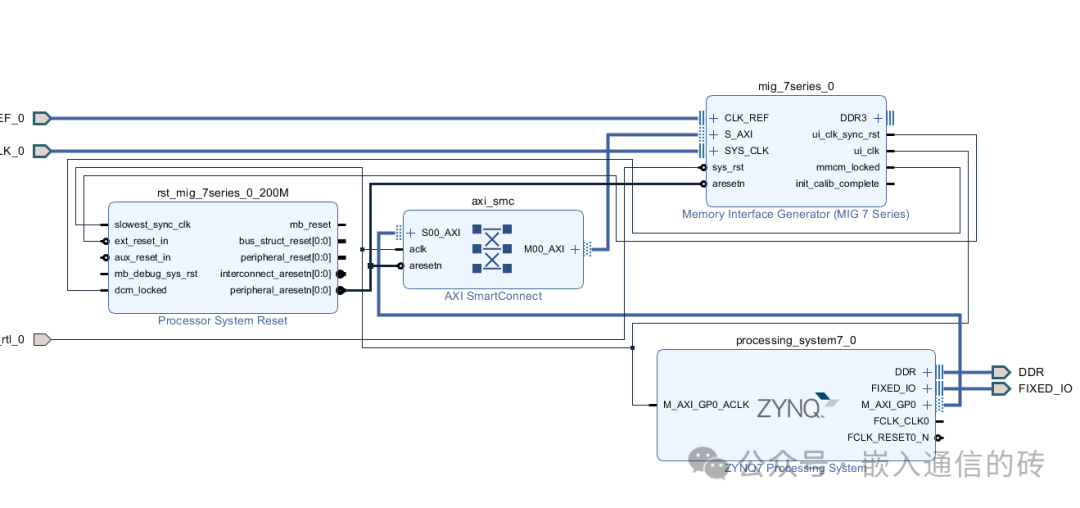

啥?我堂堂A9还是double只配使用1GB内存?这就涉及到深入理解文章了,CPU反正都是地址+数据的AXI总线,走哪不是走,我走M_AXI_GP接口扩展一个内存不可以吗?小伙子,你这BUG卡的很到位,学到了ZYNQ异构SOC的精髓。ZYNQ可以通过FPGA实现DDR控制器来扩展内存,就像下面这样,mig_7series_0是PL端实现的DDR控制器,PS通过AXI_GP接口扩展了1GB的内存。

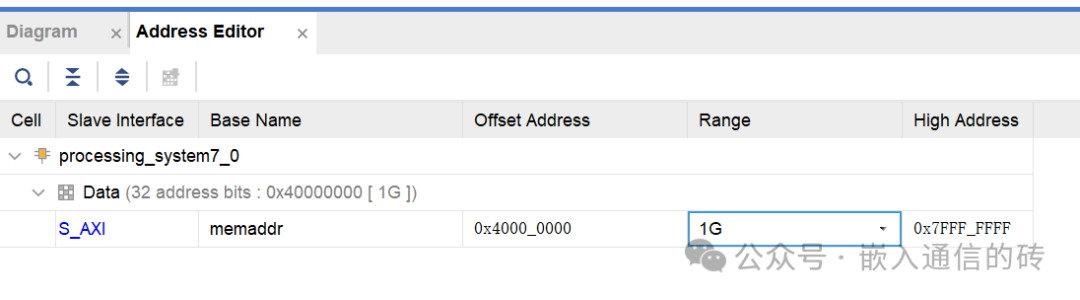

VIVADO里可以直观的看出给M_AXI_GP接口分配的AXI总线地址:

本章讲了CPU和外设的关系,外设在CPU里的地址映射,核心还是CPU处理外设都是通过地址+数据总线的方式。下一章开始实战C映射到FPGA。

893

893

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?