使用PWM来模拟DAC:PWM频率打算输出100KHZ,一次谐波频率就是100KHZ。

设计输出DAC精度8位,1次谐波对输出电压的影响不要超过1个位的精度,本人实际项目中将3.3V-MCU引脚电压抬升至5V,所以也就是5/256=0.0195V。假设VH为5V,VL为0V,那么一次谐波的最大值是2*5/Π=3.1831V,这里就计算出RC滤波电路至少提供-20lg(3.1831/0.0195)=-44dB的衰减。

通过输出频率、DAC精度、输出电压值等参数得出RC滤波电路要达到-44dB的衰减。

如果使用一阶RC滤波,根据幅频特性:-10lg[1+(f/fp)^2]; fp为截止频率(RC参数调整),f为100KHZ输入频率。代入公式:-10lg[1+(f/fp)^2] = -44; 得到f/fp=158.486,即fp=100/158.486=0.63Khz。

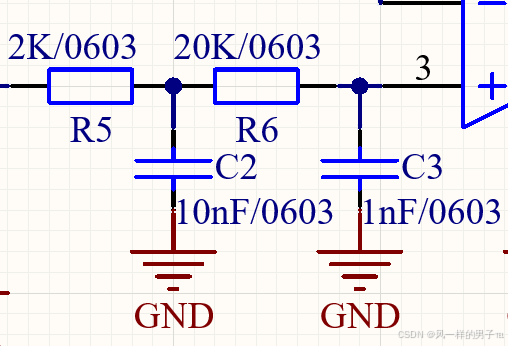

如果使用二阶RC滤波,根据幅频特性:-20lg[1+(f/fp)^2];fp为截止频率(RC参数调整),f为100KHZ输入频率。代入公式:-20lg[1+(f/fp)^2] = -44; 得到f/fp=12.549,即fp=100/12.549=7.96Khz。

二阶RC滤波截止频率计算公式:f=1/2ΠRC,较大的RC意味着较长的稳态时间,影响系统的暂态响应。当电容C较小时,电子R较大时,输出电压损耗较小,纹波较大;当电容C较大时,电阻R较小时,输出电压损耗较大,纹波较小。所以为了获取线性度较高的准确DAC转换,一般采用较小电容并尽量不要使用电解电容。

这里选取R5=2K,C2=10nF。截止频率:7.9Khz。

以上仅供参考,学识有限,有错误的地方欢迎大家指出共同进步,多多包涵。

7564

7564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?