1,zynq7000结构

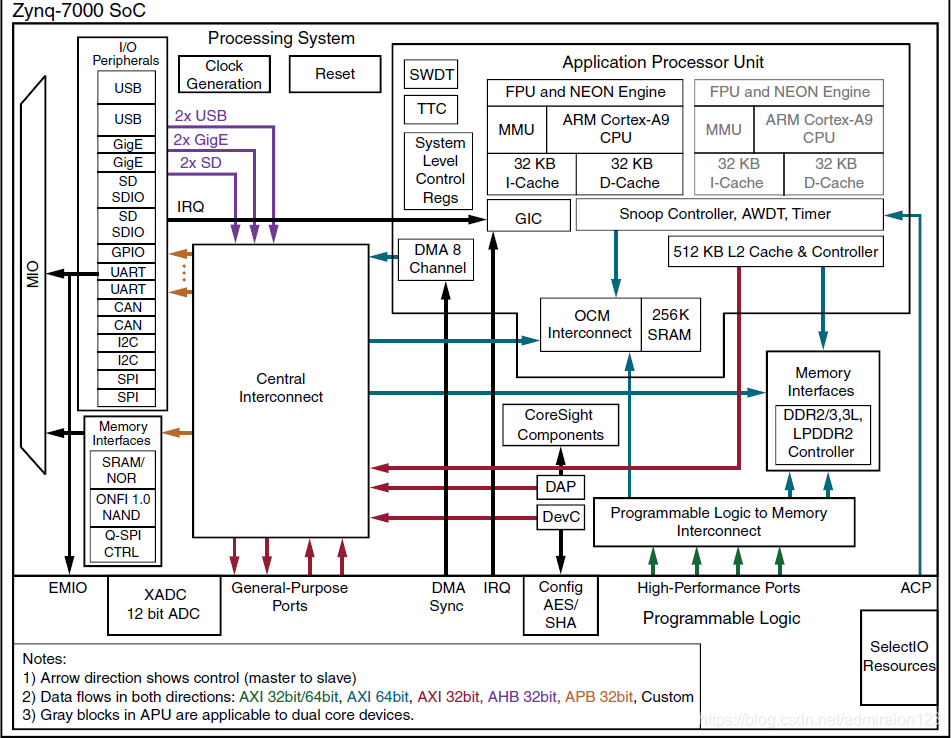

zynq7000系列的大体结构如下图所示。PL端结构与A7系列相似,大体就包括电源模块、时钟CMT、IO模块(IOB、GTP、memory interface、pcie)、CLB、BRAM、GTP、DSP、jtag调试口等。PS端包含1个APU单元,APU内有两个cotex-a9核用于运算,一个SCU用于处理数据的一致性,然后包含L1、L2级缓存,一个GIC用于中断控制,一个256KB SRAM用于程序运行,另外包含TTC、看门狗、DAP调试口等。PS端还包含一个Central Interconnect,用于互连IOP(CAN、SPI、UART、SD、USB、ETHERNET等外设),互连flash,互连DDR,互连OCM Interconnect。PS端还包含clock生成模块、复位模块等。PS与PL的连接端口有以下几个:1,axi gp口用于中心互连模块与pl外设通信,如pl侧的ram、gpio等,分为slave和master。2,axi hp用于PL侧访问DDR3,PL侧为主,一般用于DMA。3,EMIO,用于PS侧MIO口不够用时,将外设引脚通过PL侧IO口输出。4,ACP(accelerator coherence port)用于PL侧加速器直接与APU交互。5,另外还有一些PL侧中断引脚引入到GIC,同样有一些PS侧中断信号引出到PL。6,PS侧时钟和复位信号引出到PL侧。

2,启动流程

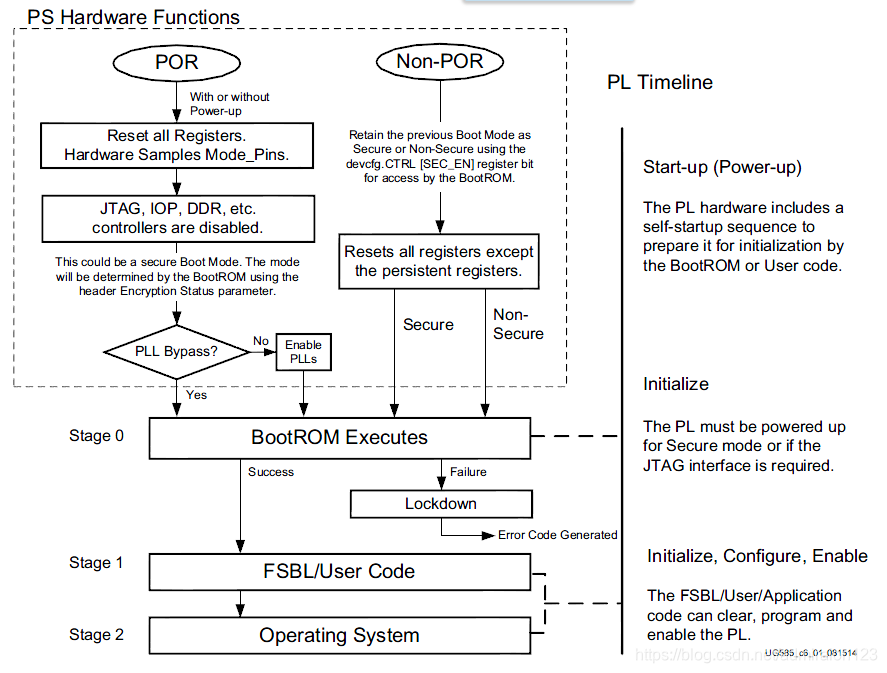

zynq7000系列的启动流程如下图所示,zynq的启动需要从ps端开始,因此zynq可以只使用ps端,但无法只使用pl端。启动过程分为三步:stage0,BootRom;stage1,FSBL/User code;stage2,U-boot/System/App。

stage0:ps端电源稳定后,ps端会复位所有寄存器、采样boot引脚、初始化配置时钟,然后执行BootRom(对用户不可见,出厂即固化在128KB的ROM中,初始地址为0。zynq7000的OCM分为256KB的RAM和128KB的ROM。如果为双核,则固定在CPU0执行,CPU1执行WFE指令,处于等待状态。);而非上电复位则不会造成硬件的重采样。BootRom的主要功能就是根据采样的启动引脚,从相应启动设备搜索BootRom Header,如果没有知道有效的header,BootRom跳转32KB地址,继续查找,直到遍历整个存储(对于Qspi flash,存储空间为16MB),并将后续加载流程交给FSBL。另外,BootRom也会将TAP与DAP口级联,并禁止ROM的访问。

stage1:FSBL主要功能是初始化ps端外设、时钟等;然后加载bit文件初始化PL侧逻辑(start-up、initialization、configura,tion、enable);最后加载用户程序的elf文件到DRAM或者OCM中,并执行。

stage2:如果带操作系统,会继续加载U-boot,并由U-boot加载操作系统内核、设备树、根目录等文件。

3,MultiBoot

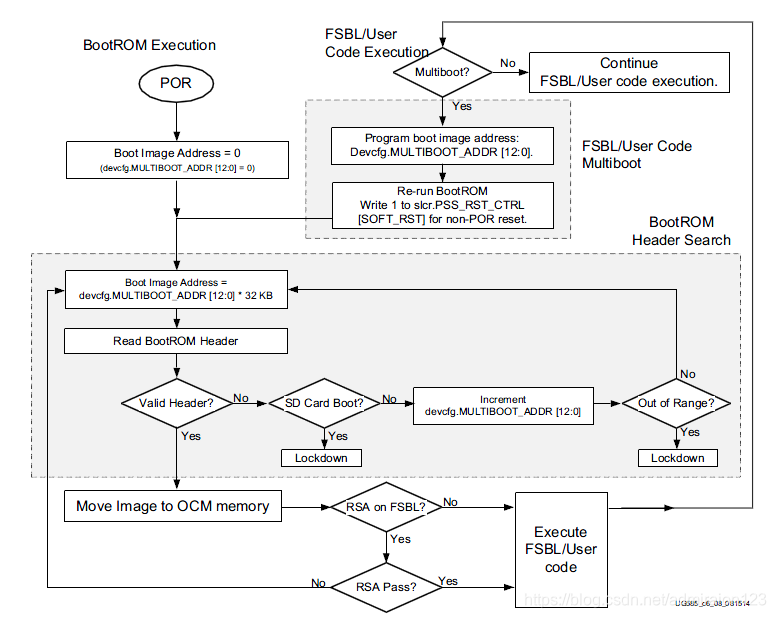

Multiboot的启动过程如下图所示。zynq7000中的.bin文件由BootRom header(0x0~0x8bf,该区域包含同步字、id、partition header的地址、第一个partition区域的地址等)、Partition Header(0x8c0~0x8ff,该区域包含所有分区信息,即包含了哪些文件)、FSBL.elf、fpga.bit、user.elf文件组成。BootRom从0地址开始,查询BootRom header,当查询到有效头时,则执行后面操作;当未查询到有效头,则偏移32KB地址,继续查询,直到遍历整个flash(采用single qspiflash时,只会遍历16MB的空间)。执行FSBL时,用户可以先配置devcfg.MULTIBOOT_ADDR,然后写slcr.PSS_RST_CTRL寄存器产生软复位,重新进行查询过程,查询的地址为MULTIBOOT_ADDR*32KB。注意,如果FSBL损坏(其余可以,bootrom header有校验码,partition header也有校验码,fpga.bit和user.elf可由生产boot.bin文件时勾选MD5校验码添加校验,但fsbl损坏,则无法识别),则无法执行fallback,也就无法实现multiboot。详细可参考https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842174/Zynq-7000+AP+SoC+Boot+-+Multiboot+Tech+Tip#Zynq-7000APSoCBoot-MultibootTechTip-DocumentHistory

本文介绍了Xilinx Zynq7000系列SoC的架构,包括PL端与PS端的具体组件及它们之间的互联方式。阐述了Zynq7000的启动流程,分为BootRom、FSBL/Usercode和U-boot/System/App三个阶段。并详细解释了多启动机制的工作原理,包括.bin文件结构和如何实现多启动。

本文介绍了Xilinx Zynq7000系列SoC的架构,包括PL端与PS端的具体组件及它们之间的互联方式。阐述了Zynq7000的启动流程,分为BootRom、FSBL/Usercode和U-boot/System/App三个阶段。并详细解释了多启动机制的工作原理,包括.bin文件结构和如何实现多启动。

442

442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?