1、问题描述

1、样机(BCM68385)在烽火进行静电测试,水平耦合+/-6KV测试fail;

2、具体表现为:设备GE和FE两个网口打流,语音口接电话,电话摘机,水平耦合+/-6KV静电测试,一两枪设备就挂死(现象:PON指示灯常亮,此时SMARTBIT上显示打流仍然正常;拔掉光纤,LOS灯不亮,

PON灯仍然常亮,再次插上光纤,SMARTBIT显示打流不正常)。

2、问题分析及实验对策

2.1 问题分析:

1、设备形态为倒扣式,外壳内主板的器件面朝下,与水平耦合板平行,敏感信号容易受影响。

2、确认静电敏感部位和异常模块:故障时,PON灯常亮,需要确认是CPU挂死还是BOB部分出现异常;另外、板子上那些部位对静电比较敏感;

3、系统死机一般都是电源,时钟、复位信号异常引起,重点需要对系统中这几类重要信号进行静电防护处理;

4、静电比较敏感的外部接口信号受到干扰:如JTAG接口、UART接口,引出来但未做端接处理的BoardID接口(GPIO)等;另外,IO接口的上下拉强度不够也会导致受干扰时电平异常,进而导致系统异常;

5、高速信号的信号完整性差导致系统抗干扰性差:如DDR3信号受到静电干扰,导致信号异常,数据错乱;

6、软件问题:如软件是否有容错机制,对系统状态进行刷新、检验和重新写入;

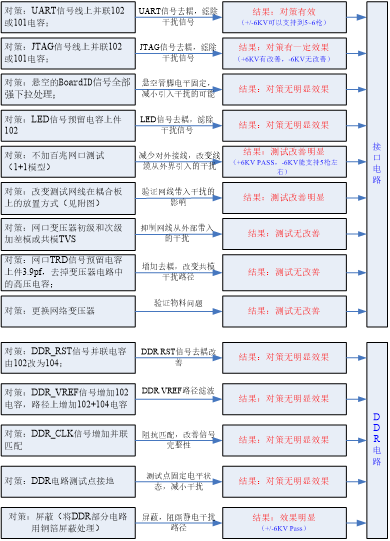

2.2 实验对策与验证:

1、设备死机时,插拔光纤,测试RX_SD信号会发生变化(插上光纤为高电平,拔掉光纤为低电平),说明BOB部分电路正常,PON灯常亮是CPU不响应RD_SD信号变化导致;接上串口,发现串口无任何信息输出,也不相应外部输入,说明系统已经挂死;

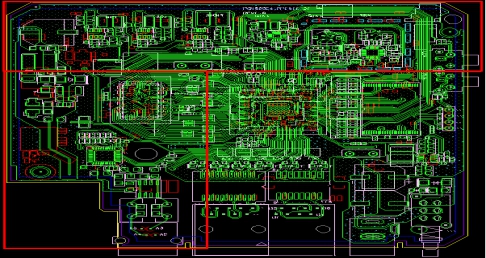

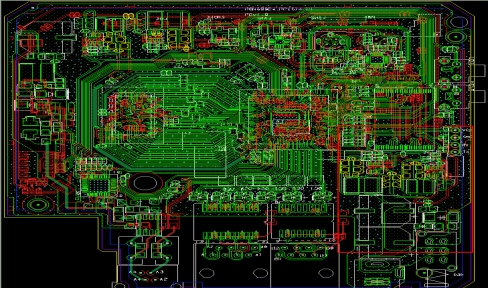

2、确定板子的敏感区域:通过局部测试的方法确认板子的敏感区域如下图所示;

如上图:红色框区域都很敏感,说明板子整体都比较弱,对静电严重敏感;在该区域内包含电源、时钟、复位等重要电路,以及DDR3这样的高速数字电路;任何部分受到干扰都有可能导致系统异常;

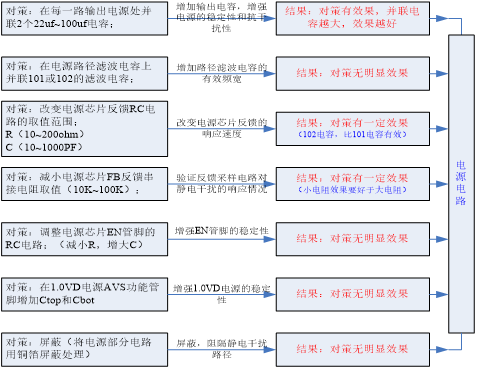

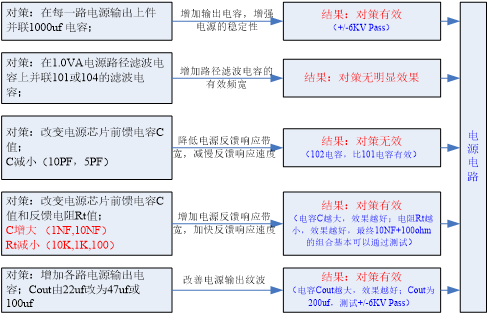

3、电源对策:

分析:通过上述对电源部分的整改,发现对系统1.0VD电路输出端增加200uf电容,抗静电有很大提升,但还是不能完全通过6kV静电测试;调整电源芯片反馈RC电路和反馈电阻,调节电源芯片的动态响应,对静电性能也有改善,但可能带来电源芯片环路不稳定的问题,需要慎重更改并进行相关性验证。

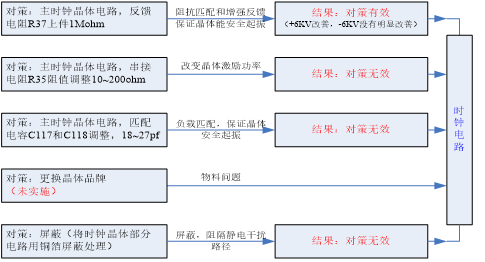

4、时钟对策:

说明:从上面对时钟电路的整改对策中,可以发现时钟电路有受到静电干扰,但时钟电路不是导致系统死机的根本原因;

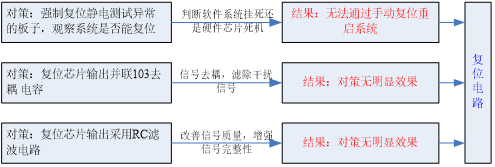

5、复位对策:

说明:由于测试中并没有出现复位现象,基本认为不是主复位电路的问题,通过第一个测试,发现死机很彻底;其余对策更多的只是尝试;

6、其余对策:

说明:项目中UART和JTAG接口对干扰比较敏感,对接口施加对策,对整机静电性能有不小的改善;DDR部分主要是从高速信号完整性方面进行考虑,因为PCB设计没有按照Demo设计对信号进行包地处理;从采用屏蔽措施得到的效果看,DDR部分信号抗静电干扰的能力比较弱;到此基本判定为DDR信号受干扰导致;

DDR部分信号抗静电干扰的能力比较弱;到此基本判定为DDR信号受干扰为导致静电测试失败的主要原因;

思考:实际测试时,将DDR只屏蔽一半,在屏蔽铜箔接地点比较少的时候,发现测试不是一定通过,在增加屏蔽铜箔接地点后发现可以稳定的通过测试;所以,对DDR屏蔽提高了DDR信号的抗干扰性能,同时也改变了整个PCB的地平面环路,这两种改变那种对静电性能改善比较大?测试过程中,还直接将PCB地引导线直接连到大地,都无法测试通过。

A:测试不能通过时的网线放置方式 B:测试可以通过时的网线放置方式

C:DDR屏蔽图

综上:根据以上测试情况,判断板子静电问题主要是DDR部分信号完整性问题和电地完整性问题导致,无法直接在原版的基础上整改通过,只能改板;另外、从本次验证情况和以往经验看,电源芯片MP1470/71本身对静电干扰也是比较敏感的,可以考虑采用抗干扰性能较好的芯片验证,改版时注意电源部分的兼容设计。

3、改版实施与效果验证

V0.02样机静电验证:

全业务静电测试:+6KV Pass,-6KV Fail;

通过局部验证法,验证发现,V0.02样机比较敏感的地方在1.0VD电源区域,如下图红色框内:

实验对策(V0.02版本)

说明:从测试情况看,加快电源芯片反馈的动态响应速度,增大电源输出电容,可以解决耦合静电

问题;尤其是对负压的静电有效,这说明在静电耦合测试时,板上的电源受到了干扰,若板上输出电容和滤波电容不足以吸收掉这些干扰,电源或地平面就会出现电压异常,对后级系统造成影响;此时就需要电源快速调节输出,保证系统电源正常;

对于增大电源芯片输出电容的方式,通过进一步的排除测试,确认只需要将V1.0VD电源的输出电容增加到1000uf即可解决静电问题。

实施方案1: MP1470\1471芯片的RC反馈回路参数调整为10NF+100ohm,电源输出电容为2*22uf。

实施方案2:MP1470\1471芯片的RC反馈回路参数不调整,电源输出电容为2*100uf.或将V1.0VD电源的输出电容增加到1000uf即可。

4、可靠性分析与验证

1、第一种方案整改存在的风险:调整电源的前馈电容C、减小反馈电阻Rt都是加快电源动态响应速度方法。

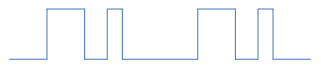

厂家提供的判断电源系统是否未定的依据是芯片SW输出波形是否出现大小波情况;如下图所示:

MPS厂商认为如果SW输出波形出现大小波,表示电源系统存在很大的不稳定性;测试我们板上的4路电源,发现在1.0VD输出端出现上述波形;

通过更改输出电容发现,当输出电容为2*22uf时,不会出现上述情况,当输出电容大于等于2*47uf。

时会出现上述情况。

2.第二种整改方案主要是影响快速开关机,经过整改样机验证,快速开关机并无问题。

3.综合成本和整改方便性考虑,采用将V1.0VD电源的输出电容增加到1000uf的方式。

5、案例总结

Ø 由于结构设计问题,主要芯片所在的TOP层在实际产品中全部朝下正对着静电耦合板,这样在芯片全部暴露在耦合板所形成的强电场中,这是产生本次静电问题的一个很大因素,对于本项目,设计初期,我们有关注到热问题和EMI问题,但是对ESD问题没有过多的关注;

Ø 个人认为静电问题是EMC中最让人琢磨不透的问题,主要是其耦合、放电路径不确定,导致定位困难;同时,针对问题所下的每一个对策,都有可能改变干扰路径;例如:对于耦合板,主要是强电场的干扰,我们假定静电放电电流从正向负流动,那么正电压放电的时候,电流从静电枪流向被测物上相对电压低且路径通畅的地方,负电压放电的时候,电流从被测物上相对电压高的地方沿通畅路径流向枪;

Ø 任何系统中的模拟电路部分(电源、时钟、复位)都是非常重要的电路,定位问题时需要充分考虑这些电路出现异常,及出现什么样的情况会导致故障的现象;

Ø 两层板设计中,地平面是非常重要的,在PCB设计时一定要尽量保证地的完整性,尤其是DDR,Serdes等高速信号下方;

5598

5598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?