1. 背景

FPGA智能网卡的价值在于卸载网络业务,减轻CPU的负担;网络卸载是以流级别作为粒度;那么配置流表是智能网卡芯片卸载业务的前提,

2. 分析配置流表的原理

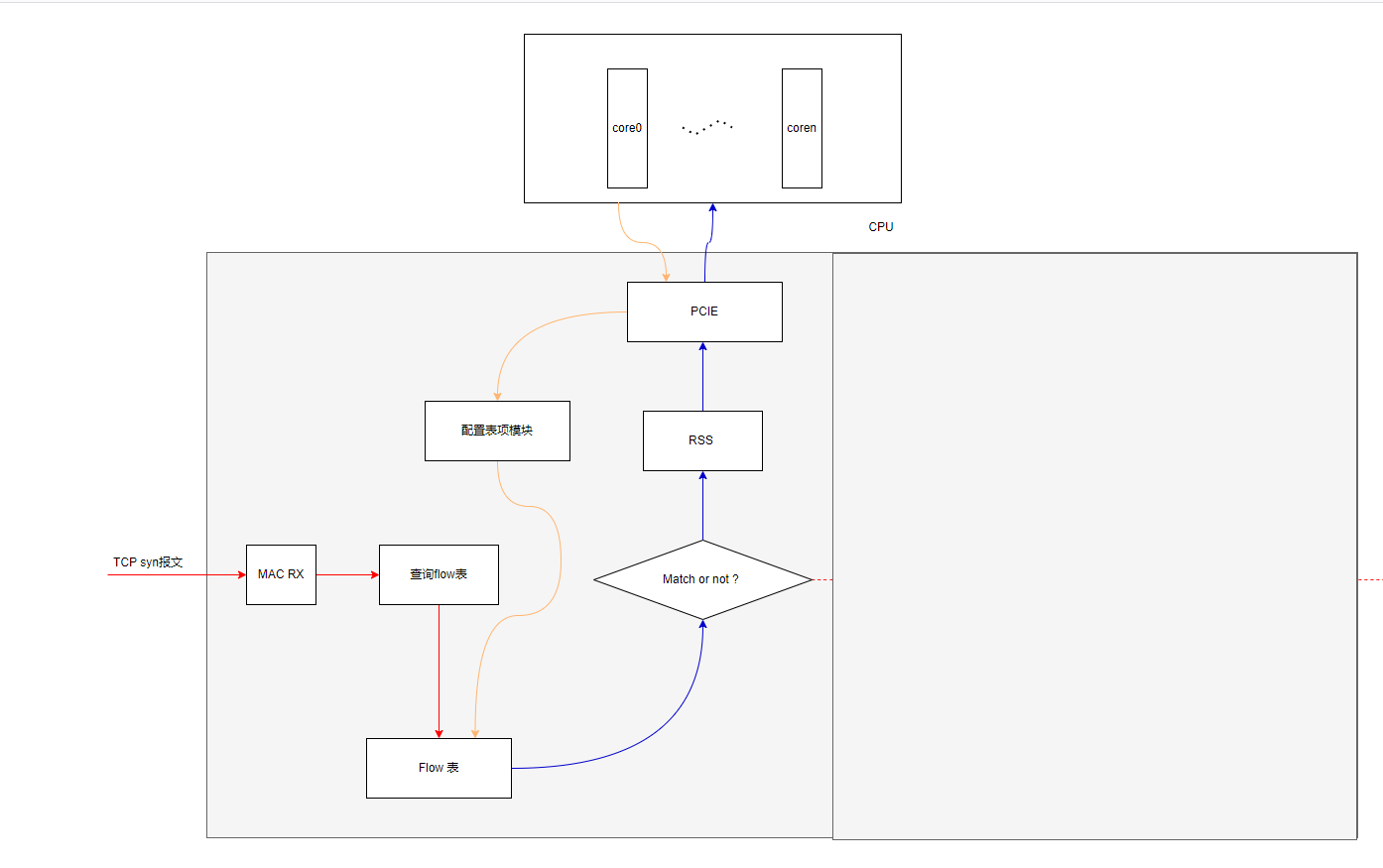

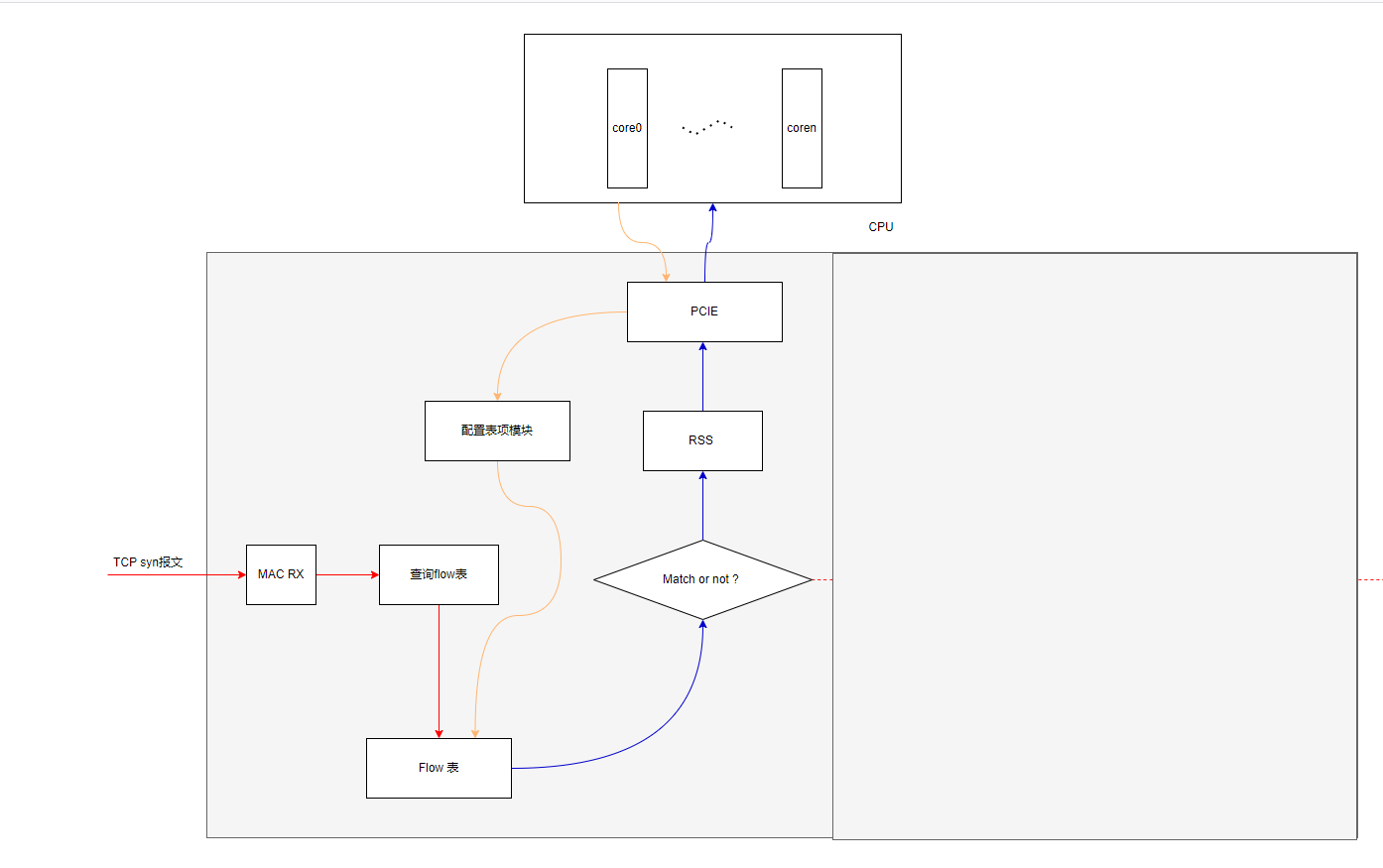

2.1 TCP报文

在TCP建立链接的过程中,智能网卡收到TCP的握手的syn报文的时候,智能网卡上送syn报文给业务,业务收到报文后,下发配置给智能网卡;具体流程如下:

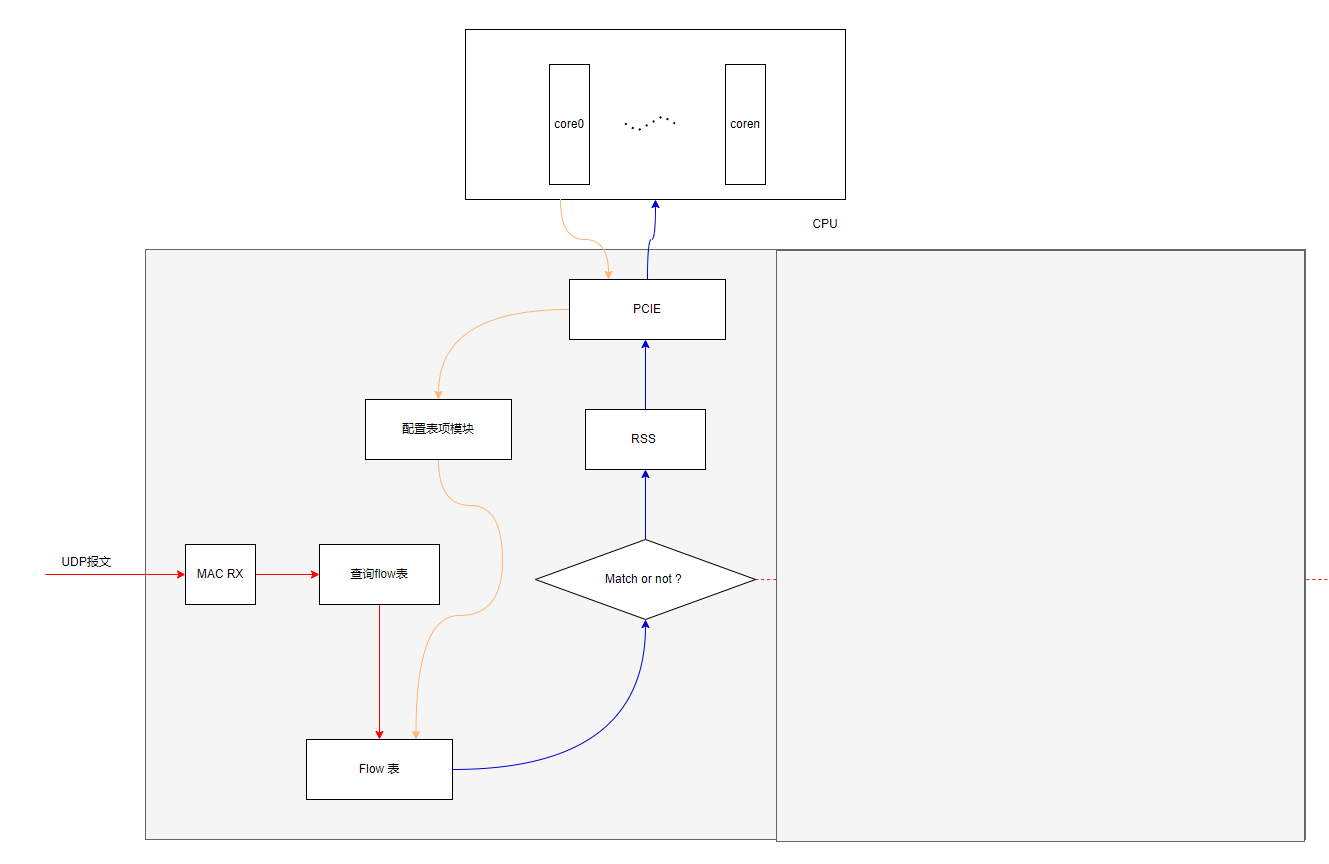

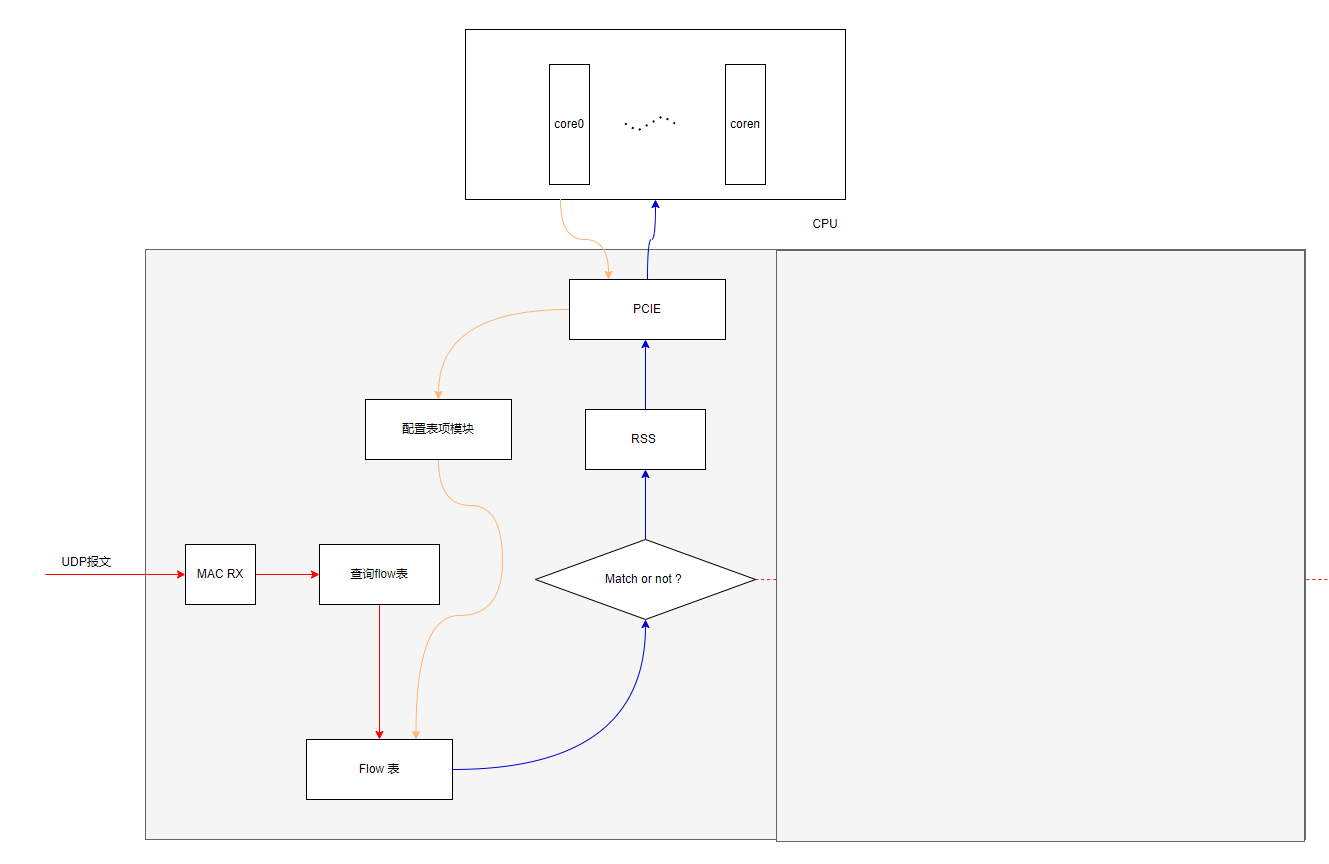

2.2 UDP报文

因为TCP的链接没有状态,智能网卡收到UDP报文的时候,智能网卡上送相应的报文给业务,业务收到报文后,下发配置给智能网卡;具体流程如下:

FPGA智能网卡的价值在于卸载网络业务,减轻CPU的负担;网络卸载是以流级别作为粒度;那么配置流表是智能网卡芯片卸载业务的前提,

在TCP建立链接的过程中,智能网卡收到TCP的握手的syn报文的时候,智能网卡上送syn报文给业务,业务收到报文后,下发配置给智能网卡;具体流程如下:

因为TCP的链接没有状态,智能网卡收到UDP报文的时候,智能网卡上送相应的报文给业务,业务收到报文后,下发配置给智能网卡;具体流程如下:

1375

1375

1252

1252

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?