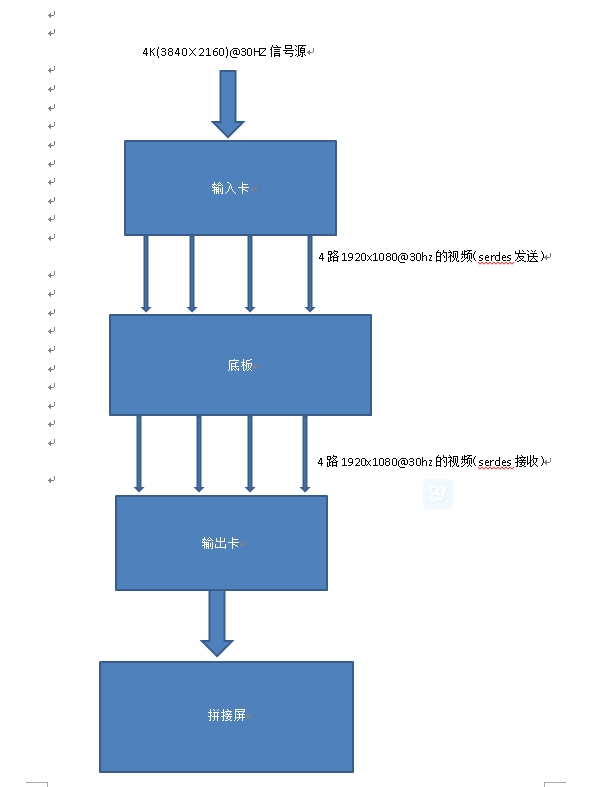

如下图:

输入卡上的FPGA先把3840 x 2160@30hz的视频裁剪为 4个 1920x1080@30hz的视频,因为 4K@30HZ的频率是 297MHZ,到 serdes 那边就变为了5.8G的带宽,对于一般的serdes带宽还是太高了 。对于FPGA内部也没有办法去处理那么高的频率,所以要降频。 所以我们把 4k 裁剪为 4个 1080p,走4路 serdes,这样接口的带宽可以将为 148.5Mhz。 然后通过底板的切换芯片,把数据传给输出卡的4路serdes, 输出卡接收到4路serdes视频信号,再把4路视频信号拼接成一个完整的3840x2160@30hz的视频。这样就可以点对点显示 4k@30hz的视频。

8500

8500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?