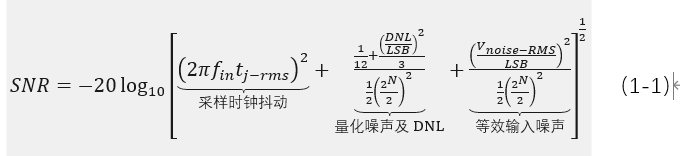

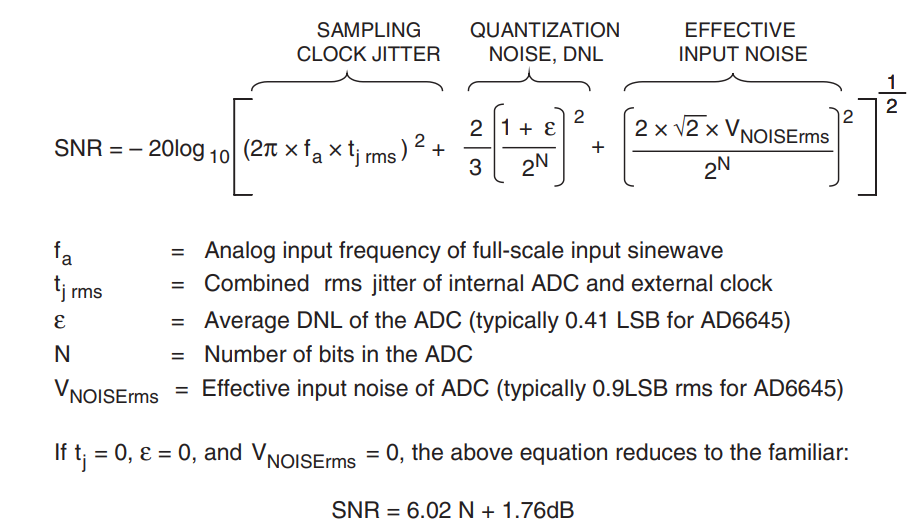

在一般奈奎斯特ADC的理论性能中常常见到如下公式(1-1),我们可以简单聊聊这个公式的来源及其背后的隐形知识。

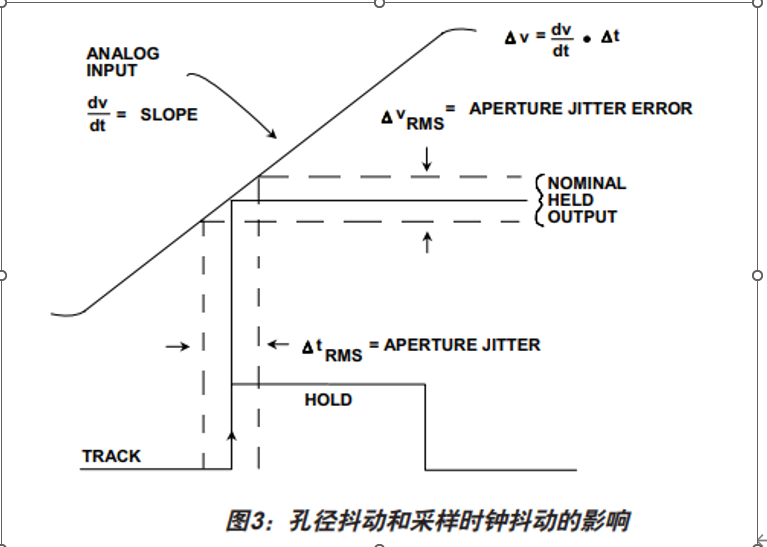

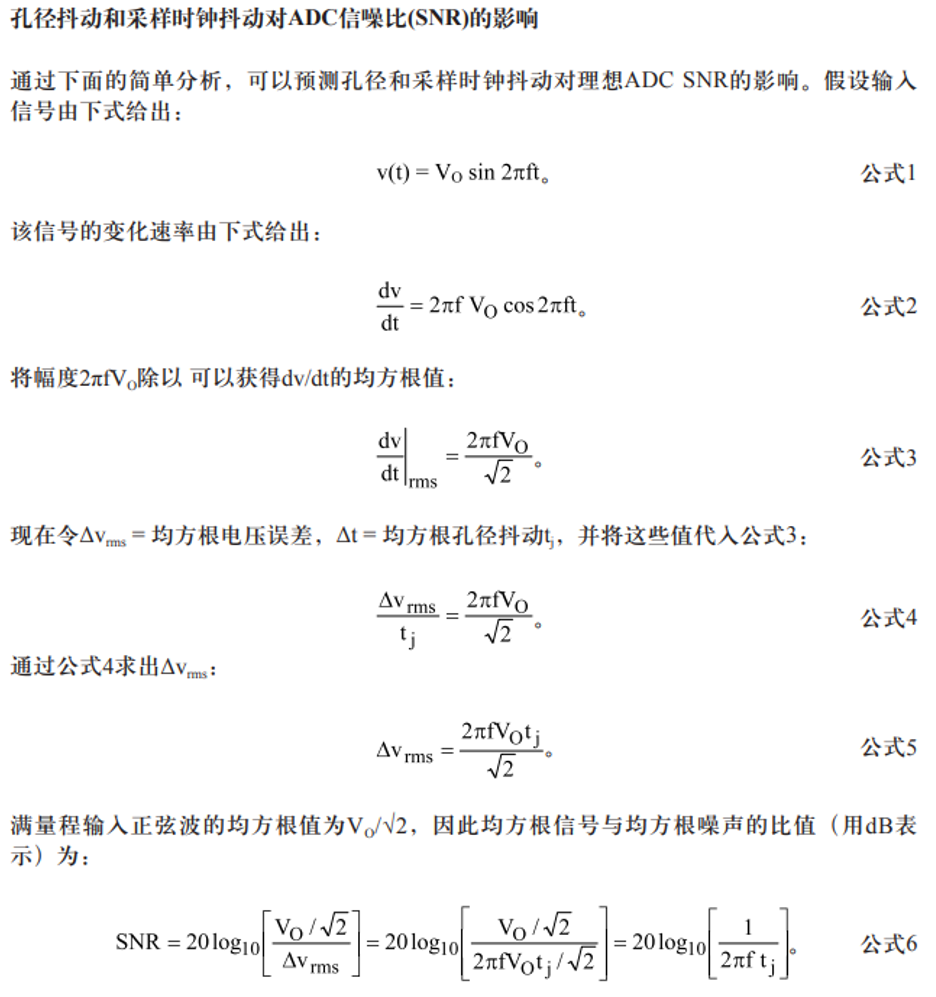

(1)采样时钟抖动部分是第一项,是一个满幅输入信号的频率,注意这里要求的是满幅,在之前的文章《从ADC性能角度对时钟相位噪声积分区间进行确定》文章已经说明了采样时钟抖动的积分区间问题,对于该部分内容,直接引用ADI的《孔径时间、孔径抖动、孔径延迟时间——正本清源》文章:

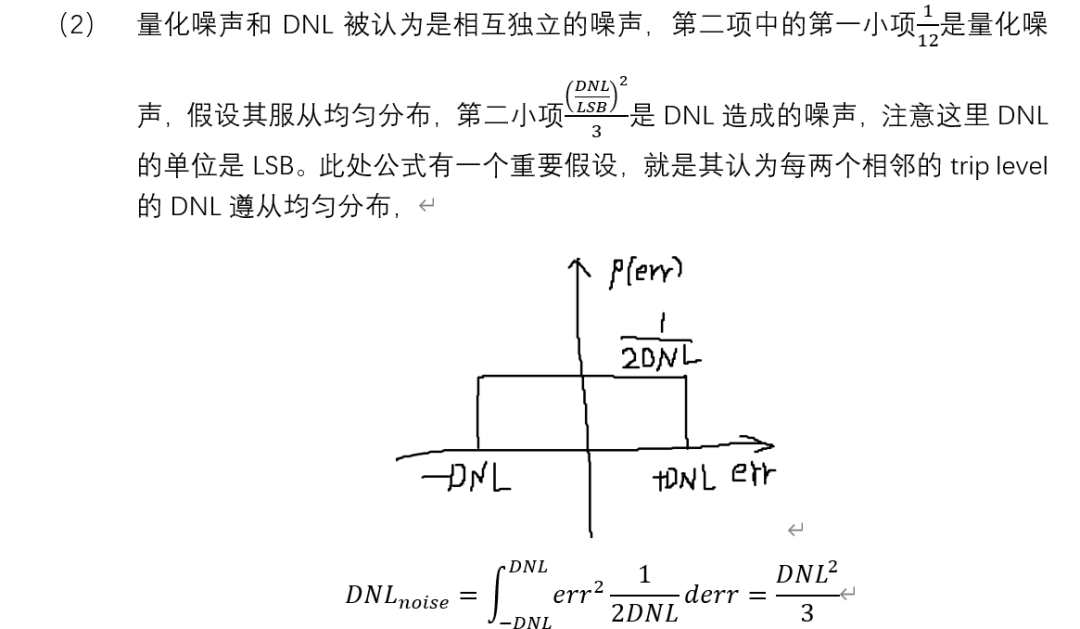

这里我们采用的是《ADC Nonlinearity—Missing Codes, Monotonicity, and Nonlinearity Effect on SNR》资料中的关于两个噪声独立的观点。

注意这两项噪声与输入信号是满幅的假设相关。但实际上DNL差分非线性噪声被假设为均匀分布并不是十分合理的,具体关于高斯假设的情形,可以参考《Analog-to-Digital Conversion》Fourth Edition书籍。

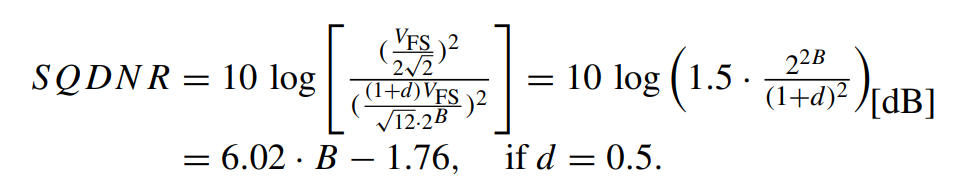

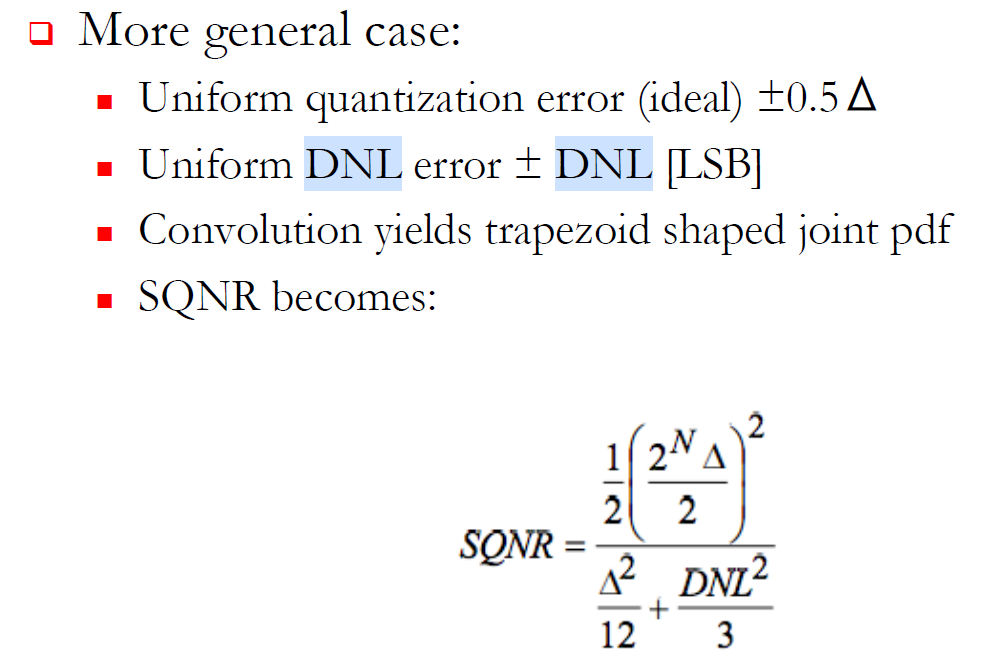

同时关于该内容ADI的官方资料和书籍《Multi-Gigahertz Nyquist Analog-to-Digital Converters Architecture and Circuit Innovations in Deep-Scaled CMOS and FinFET Technologies》有不同看法,尤其是对量化噪声与DNL噪声的关系有不同看法,它们认为整体的噪声表达为

伯克利的PPT资料《ESE 568: Mixed Signal Design and Modeling》观点为:

(3)公式的第三项是假设没有信号输入时,ADC产生的等效输入噪声, 该噪声与输入信号的大小没有关系,所以在有信号输入时和没有信号 输入时,ADC的噪底应当是有所不同的。

5228

5228

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?