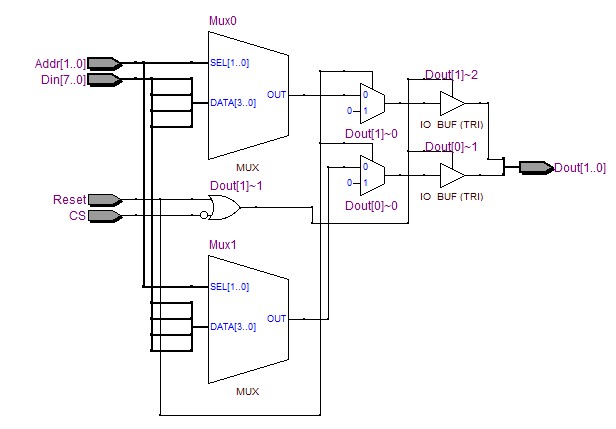

在Verilog中最常用的两种数据类型是wire和reg,一般来说,wire型指定的数据和网线通过组合逻辑实现,而reg型指定的数据不一定用寄存器实现。也就是说reg型数据不一定综合成寄存器。下面的例子中将输出信号Dout定义为reg型,但是综合与实现结果却没有使用FF,该电路是一个纯组合逻辑设计。

module reg_cmd(

input Reset,

input CS,

input [7:0] Din,

input [1:0] Addr,

output reg[1:0] Dout

);

always@(Reset or CS or Addr or Din)

if(Reset)

Dout=0;

else if(!CS)

begin

case(Addr)

2'b00:Dout=Din[1:0];

2'b01:Dout=Din[3:2];

2'b10:Dout=Din[5:4];

default:Dout=Din[7:6];

endcase

end

else

Dout=2'bzz;

endmodule 如图所示综合结果为纯组合逻辑,没有用到FF。

本文探讨了Verilog中reg类型的使用,并不总是综合成寄存器。通过一个具体的例子说明了即使定义为reg类型的数据也可以实现纯组合逻辑电路。

本文探讨了Verilog中reg类型的使用,并不总是综合成寄存器。通过一个具体的例子说明了即使定义为reg类型的数据也可以实现纯组合逻辑电路。

1138

1138

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?