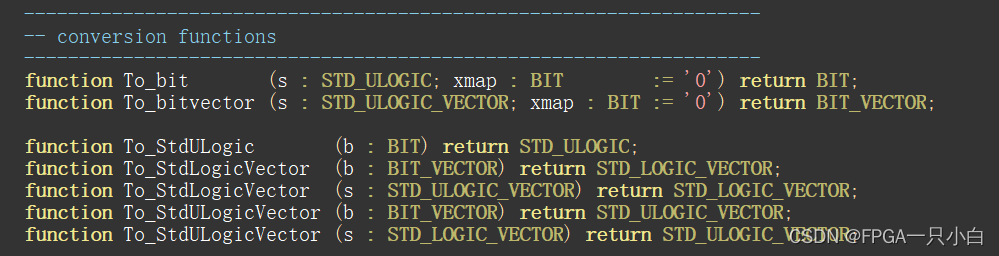

本文对常见的函数进行描述,其程序通过Quartus18.0进行编译,在编译to_stdlogic编译报错,在Quartus18.0安装目录E:\Quartus18\quartus\libraries\vhdl\ieee\2008\下STD_LOGIC_1164包下没有发现函数to_stdlogic(A),因此本文只对to_stdulogic进行编译。具体函数可以查看std_logic_1164不同版本的包,下图是std_logic_1164_vhdl2008.vhd中的数据类型转换函数。

图1、具体转换函数

| 函数 | 功能描述 |

|---|---|

| to_bit(A) | 将std_logic的数据A转换成bit类型 |

| to_stdulogic(A) | 将bit的数据A转换成std_ulogic类型 |

| to_bitvector(A) | 将std_logic_vector的数据A转换成bit_vector类型 |

| to_stdlogicvector(A) | 将bit_vector、std_ulogic_vector的数据A转换成std_logic_vector类型 |

图2、部分函数功能描述

(1)、to_bit(A)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.all;

USE IEEE.STD_LOGIC_UNSIGNED.all;

USE IEEE.STD_LOGIC_ARITH.all;

ENTITY data IS

PORT(

a : IN STD_LOGIC;

b : IN STD_LOGIC;

c : OUT BIT

);

END ENTITY;

ARCHITECTURE rtl OF data IS

BEGIN

--a异或b

c <= TO_BIT(a XOR b);

END rtl;(2)、to_stdulogic(A)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY data IS

PORT(

a : IN BIT;

b : IN BIT;

c : OUT STD_ULOGIC

);

END ENTITY;

ARCHITECTURE rtl OF data IS

BEGIN

--a异或b

c <= TO_STDULOGIC(a XOR b);

END rtl;

(3)to_bitvector(A)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY data IS

PORT(

a : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

b : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

c : OUT BIT_VECTOR(7 DOWNTO 0);

d : OUT BIT_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE rtl OF data IS

BEGIN

--a异或b

c <= TO_BITVECTOR(a XOR b);

d <= TO_BITVECTOR(a + b);

END rtl;(4)to_stdlogicvector(A)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY data IS

PORT(

a : IN BIT_VECTOR(7 DOWNTO 0);

b : IN BIT_VECTOR(7 DOWNTO 0);

c : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

);

END ENTITY;

ARCHITECTURE rtl OF data IS

BEGIN

--a异或b

c <= TO_STDLOGICVECTOR(a XOR b);

END rtl;参考:本文参考Quartus软件中的std_logic_1164_vhdl2008.vhd完成。

备注:本文编译采用GVIM进行完成。

1080

1080

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?