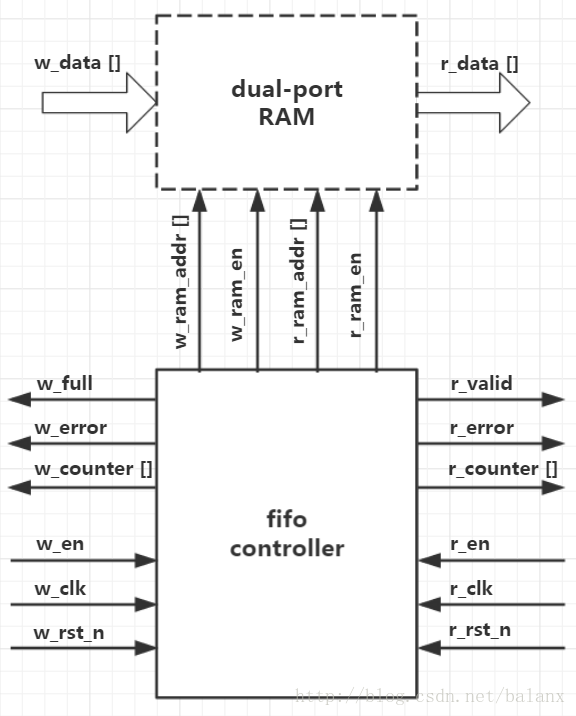

异步 FIFO 控制器 (Asynchronous FIFO Controller)

Introduction

FIFO 是设计中常用的器件,用于跨时钟域的数据传送。一般从厂家库中直接调用即可,是不需要自己设计的。

但学习和理解 FIFO 设计方法,对于理解跨时钟域异步信号的处理方法很有帮助。

项目地址:Laotzu

Feature

经典 FIFO 设计方法(见参考文档)

参数化数据宽度和 FIFO 深度

增强的同步数据有效指示

增强的首数据预读加速功能(可关闭)

Application

Input/Output

| Name | I/O | Description |

|---|---|---|

| w_rst_n | I | Reset in write-side |

本文介绍了异步FIFO控制器的设计与应用,重点讨论了首数据预读加速和同步数据有效指示功能,旨在提高跨时钟域数据传输的效率。通过参数化设置,该控制器能适应不同数据宽度和FIFO深度,且提供了可配置的预读功能以优化吞吐率。同时,采用r_valid信号同步指示读数据有效性,以增强FIFO的灵活性。

本文介绍了异步FIFO控制器的设计与应用,重点讨论了首数据预读加速和同步数据有效指示功能,旨在提高跨时钟域数据传输的效率。通过参数化设置,该控制器能适应不同数据宽度和FIFO深度,且提供了可配置的预读功能以优化吞吐率。同时,采用r_valid信号同步指示读数据有效性,以增强FIFO的灵活性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1454

1454

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?