随着国产替代、人工智能、车规电子等方向的高速发展,FPGA作为灵活、高性能的可编程逻辑器件,在众多行业场景中都发挥着重要作用。我国每年对FPGA开发人才的需求居高不下,发展前景广阔。那么,如何成为一名真正合格的FPGA工程师?

什么是FPGA?

FPGA(Field Programmable Gate Array,现场可编程门阵列),是一种用户可以在“现场”进行二次配置的集成电路。相较于传统的ASIC芯片,FPGA具有更高的灵活性和更短的开发周期,广泛应用于通信、视频处理、自动驾驶、工业控制、航空航天等领域。

其主要特性包括:

-

支持硬件重构,逻辑资源可动态配置;

-

具备高速并行处理能力,适合实时处理任务;

-

适合原型验证、低批量定制、边缘计算等多场景;

-

正在从传统的逻辑开发迈向软硬协同设计,逐步融合C/C++等高阶语言;

想成为一名FPGA工程师,需要掌握哪些知识?

1. 熟练掌握Verilog HDL

Verilog语言是FPGA开发的基础,掌握其语法结构、建模方式、常见的编码风格,是开发可综合逻辑的前提。重点包括:

-

组合逻辑、时序逻辑建模;

-

模块化设计与层级封装;

-

有限状态机(FSM)描述方法;

-

多位宽信号处理、参数化设计等技巧。

2. 了解器件架构

熟悉主流厂商(如Xilinx、Intel)的FPGA芯片架构非常关键。比如:

-

逻辑单元(LUT、Flip-Flop);

-

存储资源(BRAM、FIFO);

-

DSP资源、PLL/Clock管理;

-

器件内部的连接结构、时钟域分布等;

建议优先学习Spartan-3、Virtex-4等典型器件,理解其资源对Verilog代码的映射机制。

3. 掌握开发工具链

现代FPGA开发离不开EDA工具的支持。至少需要掌握:

-

综合工具:如Synplify、Vivado、Quartus;

-

仿真工具:如ModelSim、Vivado Simulator;

-

调试工具:如Chipscope、ILA、SignalTap;

-

时序分析与资源估算:静态时序、Slice/LUT/FF使用分析;

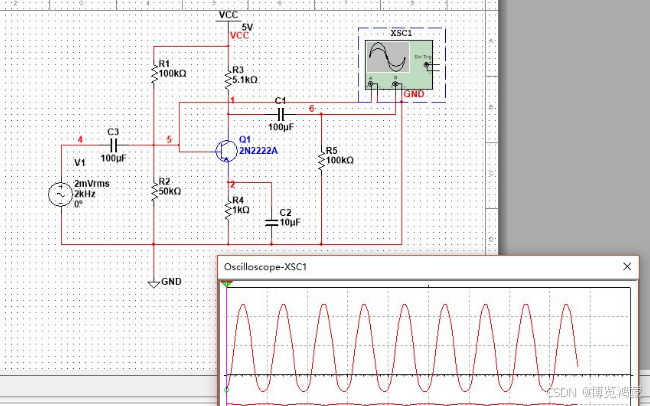

4. 数字电路基础扎实

掌握基础电路概念是写出高效、稳定Verilog代码的根本:

-

组合逻辑设计、布尔代数;

-

时序逻辑(尤其是D触发器应用);

-

分频器、奇偶检测、码流识别等基础模块;

-

时钟同步与跨时钟域处理;

5. 熟悉设计流程

一个标准的FPGA设计流程包括:

设计需求分析 → RTL编码 → 功能仿真 → 逻辑综合 → 静态时序分析 → 布局布线 → Bitstream生成 → 下载验证

对流程中每一步的常见问题、调试方法和资源消耗估算要有深入理解。

6. 掌握同步设计原理

FPGA工程师应当避免异步设计带来的毛刺、竞争冒险等问题,需掌握以下概念:

-

建立时间、保持时间;

-

异步信号同步、多时钟域数据传输;

-

消除毛刺的编码技巧;

-

时序约束与约束文件编写(SDC/XDC);

7. 注重设计经验与思路积累

没有实战经验,再多的理论都难以真正落地。建议从小模块着手,逐步掌握:

-

数据通路与控制通路划分;

-

流水线设计与打拍;

-

工程资源与功耗的平衡考虑;

-

RTL调试与仿真覆盖;

对于在校生而言,可以从毕业设计或开源项目中积累经验。

FPGA工程师的发展前景如何?

FPGA的应用边界不断扩展,对工程师的要求也在迅速提升。从纯RTL工程师向系统级设计、硬件架构、异构计算等方向延伸,都是非常典型的发展路线。

在很多小型或中型企业中,FPGA开发者往往身兼系统设计、调试、硬件接口定义等多项职责,是整个产品实现的关键角色。在大型公司中,FPGA工程师也常与算法工程师、嵌入式开发工程师深度协作,共同完成复杂系统实现。

此外,未来FPGA编程会更加靠近高级语言,如HLS(高层次综合)、C/C++协同设计等将成为主流趋势,进一步推动软硬融合。

FPGA作为硬件工程中的重要方向之一,不存在“吃青春饭”的问题,只要技术硬核、经验丰富,年纪越大越吃香,很多资深工程师仍活跃在一线岗位。对在校学生而言,FPGA是一个非常具性价比的切入点。

推荐书籍:

1.《Verilog数字系统设计教程》

通过算法与逻辑的结合,详细讲解Verilog建模方法,含大量实验案例,适合初学者入门。

2.《数字电路与逻辑设计》

系统介绍数字电路基础和分析方法,并结合中大型器件做应用示范。

3.《Xilinx新一代FPGA设计套件Vivado应用指南》

从Vivado设计流程出发,结合Tcl脚本、时序优化等进阶技能,是掌握Xilinx平台不可或缺的资料。

需要学习资料的同学,可以私信留下正确的联系方式,或者填写入行指导表单,宸极教育的老师会主动联系你发送资料包!

181

181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?