手机、平板、电脑、座舱上广泛使用屏幕和摄像头,依赖MIPI信号,做下总结。

序:1、关于C-PHY和D-PHY的演进:D-PHY从2009年v1.0的1.5Gbps/lane发展到v2.5的4.5Gbps/lane,并通过C-PHY兼容模式延续生命;C-PHY则从v1.0的2.5Gsps发展到v3.0的6.0Gsps,凭借三相编码的带宽优势成为高端选择。这背后是移动设备对带宽需求的指数级增长——4K/8K显示屏、多摄像头系统需要比传统D-PHY更高的数据吞吐量。

2、测试方面,C-PHY的复杂编码(16b/7符号)带来的独特挑战:比如用VNA测S参数时要关注所有端口组合(SDD11/SDD21/SCC11/SCD21),示波器需要3通道以上且支持C-PHY解码,以及如何用BERT进行接收机容限测试。验收标准必须严格遵循MIPI CTS,比如回损<-12dB、插损满足不同速率下的模板要求。

3、C-PHY虽高效但设计复杂(需要严格控制三线间偏移<160ps),D-PHY更成熟稳定。若项目追求极致带宽且有能力处理高速信号完整性,选C-PHY;若优先级是降低风险和成本,D-PHY v2.5可能是更安全的选择。

一、协议演进历史与规划

D-PHY 版本演进

D-PHY是MIPI联盟最早推出的物理层标准,多年来持续迭代,以满足日益增长的带宽需求。

| 版本 | 推出时间 | 核心演进 | 最高速率 (Per Data Lane) | 关键特性 |

|---|---|---|---|---|

| D-PHY v1.0 | ~2007 | 奠定基础 | 1 Gbps | 定义HS/LP模式,支持CSI-2/DSI-1 |

| D-PHY v1.1 | 2009 | 性能提升 | 1.5 Gbps | 优化时序,提高速率 |

| D-PHY v1.2 | 2014 | 能效与可靠性 | 1.5 Gbps | 引入ULPS(Ultra-Low Power State) |

| D-PHY v2.0 | 2017 | 性能翻倍 | 2.5 Gbps | 新齿轮(Gear),支持C-PHY兼容模式 |

| D-PHY v2.5 | 2020 | 延续与过渡 | 4.5 Gbps (Gear 5) | 进一步提升速率,支持更高速的传感器和显示屏 |

演进规划: D-PHY的发展已趋于成熟。其未来角色主要是作为低成本、低复杂度应用的可靠选择,并与C-PHY组合使用。MIPI联盟的发展重点已转向更先进的M-PHY(用于高速存储、汽车等)和A-PHY(汽车长距离串行器-解串器器)。

C-PHY 版本演进

C-PHY作为后来者,以其极高的带宽效率,旨在解决D-PHY在引脚数和带宽上面临的瓶颈。

| 版本 | 推出时间 | 核心演进 | 最高符号率 (Per Trio) | 有效带宽 (Per Trio) | 关键特性 |

|---|---|---|---|---|---|

| C-PHY v1.0 | ~2013 | 奠定基础 | 2.5 Gsps | ~5.71 Gbps | 引入三相符号编码,嵌入式时钟 |

| C-PHY v1.1 | 2015 | 性能提升 | 3.0 Gsps | ~6.85 Gbps | 优化电气参数 |

| C-PHY v1.2 | 2016 | 能效提升 | 3.5 Gsps | ~8.00 Gbps | 引入ALP(Alternate Low-Power)模式 |

| C-PHY v2.0 | 2019 | 重大升级 | 4.5 Gsps | ~10.28 Gbps | 大幅提升速率,增强抗噪能力 |

| C-PHY v2.1 | 2021 | 持续优化 | 6.0 Gsps | ~13.7 Gbps | 支持8K+显示和超高分辨率传感器 |

演进规划: C-PHY将继续向更高符号率(可能达到8.0+ Gsps) 发展,并进一步优化功耗和抗干扰能力,以巩固其在高端移动设备摄像头和显示屏接口中的主导地位。

二、技术原理与数据传输

D-PHY:源同步差分传输

-

工作模式:

-

高速(HS)模式: 用于传输有效数据。采用低压差分信号(LVDS),摆幅约为200mV(140mV - 270mV),电流模式驱动。

-

低功耗(LP)模式: 用于控制信令、行场同步、传输开始结束(SoT/EoT)包。采用单端信号,电压摆幅在1.2V左右(0V - 1.2V),电压模式驱动。

-

超低功耗状态(ULPS): 一种比LP模式更深的休眠状态,漏电流极低。

-

-

数据传输与编码:

-

D-PHY本身不负责高层数据编码,它仅为上层协议(如CSI-2 for camera, DSI for display)提供物理通道。

-

在HS模式下,数据通过差分对传输。时钟lane提供连续的时钟,数据lane在时钟的边沿被采样。

-

CSI-2/DSI协议会在数据包中加入错误校验码(CRC),但物理层无复杂编码。

-

-

波形示意:

-

HS模式波形: 标准的LVDS眼图,差分交叉点。

-

LP模式波形: 类似CMOS的单端方波。

-

HS->LP切换: 有一段严格的“桥接”时间,防止总线冲突。

-

D-PHY 操作模式转换时序图

C-PHY:三相嵌入式时钟传输

-

物理基础 - 三线系统:

一个C-PHY通道称为一个Trio,包含A, B, C三根信号线。它们之间是差分关系(A-B, B-C, C-A),但并非传统意义上的差分对。在任一时刻,这三根线的电流之和为零。 -

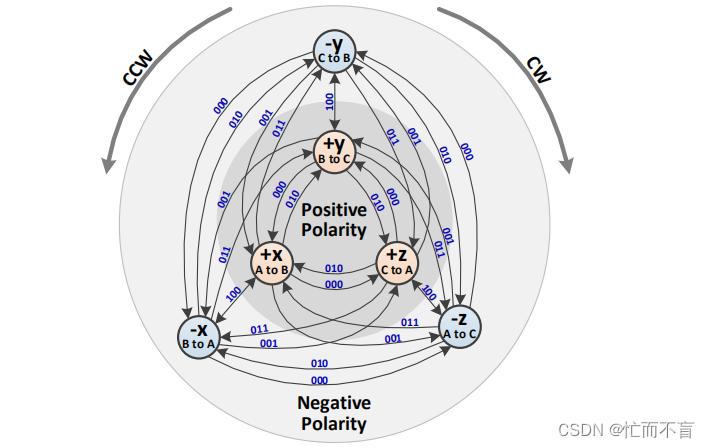

核心:三相符号编码(3-Phase Symbol Encoding)

这是C-PHY的灵魂。其数据表示不依赖于信号的绝对电压,而依赖于线态(Wire State)之间的转换。-

线态(Wire State): 在任一时刻,A, B, C三根线被驱动到三个不同的电压电平(例如,0mV, 100mV, 200mV)。由于三者各不相同,共有6种可能的排列组合,即6种线态。

-

符号(Symbol): 数据信息由从一个线态到另一个线态的跳变来承载。每次跳变定义了一个符号。共有 16种有效的符号跳转(因为不是所有跳转都是允许的)。

-

编码效率: 每个符号携带 log2(16) = 4 bits 的信息。但C-PHY采用 16b/7符号 的块编码,即16位有效数据被映射为7个连续的符号(共可表示 4 bits/symbol * 7 symbols = 28 bits,但只用了其中16位)。因此,其编码效率为 16/7 ≈ 2.28 bits per symbol。

-

嵌入式时钟: 由于每次符号跳变都意味着信号变化,接收端可以从中恢复出时钟(CDR),从而无需独立的时钟通道。

-

-

工作模式:

-

高速(HS)模式: 用于数据传输,采用上述的符号编码。

-

低功耗(LP)模式: 类似于D-PHY,用于控制。

-

交替低功耗(ALP)模式: C-PHY v1.2引入的关键特性。它复用HS模式的电路来传输LP信令,不仅显著降低了IO电路的漏电功耗,还极大地扩展了控制指令的传输距离(最长可达4米),为伸缩屏、折叠屏等创新设计提供了可能。

-

-

波形示意:

C-PHY的波形非常独特,三根线相互交织,无法用简单的眼图分析,必须使用多通道示波器进行同步测量和解码。

C-PHY 三线信号与符号转换示意图

三、使用场景与设计注意点

使用场景

-

D-PHY: 成熟稳定,IP成本较低。广泛应用于中高端智能手机的前/后置摄像头(CSI-2)和显示屏(DSI)。是过去十年的绝对主力。

-

C-PHY: 高性能、高带宽效率。主要用于超高分辨率传感器(亿级像素摄像头)、高刷新率显示屏(120Hz+)以及需要极致节省引脚的紧凑型设计。是目前高端旗舰设备的首选。

设计注意点(PCB/SI)

| 方面 | D-PHY | C-PHY |

|---|---|---|

| 布线拓扑 | 点对点 | 点对点 |

| 阻抗控制 | 差分100Ω ±10% | 松耦合差分,目标差分阻抗100Ω,单端50Ω。这是关键!阻抗当前也在演进,可调阻抗 |

| 等长要求 | 数据lane内差分对等长(<10mil),lane间等长(<100ps) | Trio内三根线必须严格等长(通常要求< 2.5 ps/mm 累积偏移,整条链路 < 160 ps)。这是最严峻的挑战! |

| 损耗要求 | 插入损耗(IL)需满足规范模板(如-3dB @ Nyquist) | 对损耗更敏感。需严格控制IL和回损(RL)。 |

| 端接 | 接收端差分并联端接(100Ω) | 接收端采用星形端接(中心点电压为共模电压)。 |

四、电气特性、插损/回损要求

电气特性(摘要)

| 参数 | D-PHY (HS Mode) | C-PHY (HS Mode) |

|---|---|---|

| 信号类型 | LVDS (电流模式) | 三线差分 (电流模式) |

| 电压摆幅 | ~200mV (差分) | ~200mV (线对线差分) |

| 共模电压 | ~200mV | ~200mV (每根线) |

| 终端匹配 | 100Ω 差分并联 | 50Ω 单端星形连接 |

插入损耗(Insertion Loss)与回波损耗(Return Loss)

这是高速串行链路设计的核心指标,通常通过S参数来衡量。

-

D-PHY:

-

回波损耗(RL, Sdd11/Scc11): 通常要求 > -10 dB 或 -12 dB 直到奈奎斯特频率(f<sub>NYQUIST</sub> = 1/2 * 比特率)。

-

插入损耗(IL, Sdd21): 需满足规范的“通道操作区域”模板。例如,总损耗(芯片+PCB+连接器)在奈奎斯特频率处需优于 -3.5 dB 或更严格的值。

-

-

C-PHY:

-

回波损耗(RL): 要求更为严格。通常要求 > -12 dB 甚至 -15 dB 直到符号率的奈奎斯特频率。需要测量所有端口组合(Sdd11, Scc11)。

-

插入损耗(IL): 需满足规范定义的模板。由于其更高的工作速率,对PCB材料的损耗(Df值)要求极高,通常需要高速板材(如Megtron 6/7/8)。

-

模式转换(SCD21): 由于是三线系统,还需要关注差分到共模的转换损耗,确保平衡性。

-

验收标准: 必须使用矢量网络分析仪(VNA)测量通道的S参数,并确认其完全符合MIPI规范中定义的一致性测试模板(Compliance Mask)。

五、测试仪器与方法

-

测试仪器选择:

-

高性能示波器: 核心工具。带宽至少为最高信号频率成分的2.5倍以上(例如,对于4.5Gsps的C-PHY,需要≥ 15 GHz 带宽的示波器)。需要3个或更多通道同步采样。

-

矢量网络分析仪(VNA): 用于测量S参数,验证通道的插损、回损是否达标。

-

协议分析仪: 用于解码上层协议(CSI-2/DSI),验证数据正确性。

-

误码率测试仪(BERT): 用于进行接收机容限测试(Receiver Margin Test),注入压力和抖动,测试接收机的鲁棒性。

-

-

测试方法:

-

物理层测试:

-

D-PHY: 测量HS模式眼高、眼宽、抖动、上升/下降时间;LP模式电压电平;模式转换时序。

-

C-PHY: 极其复杂。需同步捕获Trio的三根线,使用专业软件(如Keysight Infiniium Offline Analysis)进行符号解码,并分析符号间干扰(ISI)、抖动、共模噪声等。ALP模式也需要单独测试。

-

-

一致性测试: 遵循MIPI联盟发布的CTS(Conformance Test Suite) 文档,使用自动化测试软件和夹具,逐项验证物理层和协议层的每一项参数是否满足规范要求。

-

接收机测试: 使用BERT或具有压力输出功能的示波器,向接收机发送“压力眼图”( degraded signal),逐渐增加压力幅度直到出现误码,以此衡量接收机的性能裕量。

-

总结

C-PHY和D-PHY是MIPI联盟推出的两大移动设备物理层接口技术。D-PHY成熟稳定,易于实现;C-PHY通过复杂的三相编码实现了极高的带宽效率和引脚经济性,但设计和测试挑战巨大。选择哪一种取决于应用对带宽、功耗、成本、开发周期和风险的综合考量。目前,两者在移动设备领域并存,C-PHY正逐渐成为高端市场的首选。

1739

1739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?