好长时间没写博客了

下文中提到的文件可在此仓库下载:https://github.com/deadfffool/HUST-Computer-Organization-Big-Homework/tree/main

在转换为verilog之前,需要对logisim电路做以下几点改动:

- 首先将下载的

logisim_change.jar放在与logisim电路文件的同一目录下,打开logisim_change.jar文件,在logisim的==“文件”==界面可以发现“save verilog”选项。在界面中打开.circ文件。

- 删除顶部的输入输出和数字显示管,删除文本标签和

mips probe器件。删除ALU电路中不能被Verilog使用的乘法器和除法器部分(实际电路中也未使用)。 - 增加新的输入输出引脚,输入引脚为

RST(总复位)、Go(继续运行)以及CLK(时钟信号),输出引脚为SEG和NA。增加“输入/输出”库中的器件FPGADigit作为输出中转。

- 修改所有电路名称(不符合verilog规范的名称会弹出

the component name is illegal),将中文名称改为英文。修改隧道和引脚的名称使之符合verilog规范。

- 保证输入引脚不悬空,并将所有引脚的三态改成“否”。

- 为ROM、RAM添加标签。

- 更改所有的复用器(包括优先编码器、多路选择器等)的三态选项,选择禁用时输出0。

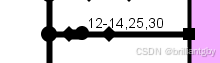

- 特别注意的是,verilog不支持分线器分为多段输出,因此需要将其改为两个分线器的对接。

6335

6335

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?