一个栗子:

verilog代码:(最简单的门的逻辑)

module n1( input a,b,

output [5:0]z

);

assign z = {a&b,~(a&b),a|b,~(a|b),a^b,~(a^b)};

endmoduleMap总结:

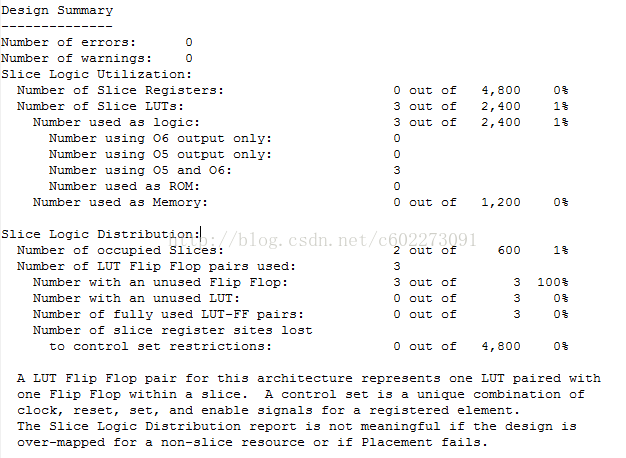

上图可以看到Number of LUT registers用了三个,还有Occupied Slice 2个。这里的意思是为了实现这个逻辑,使用了FPGA里面的2个slice,这个算综合的不错的了。

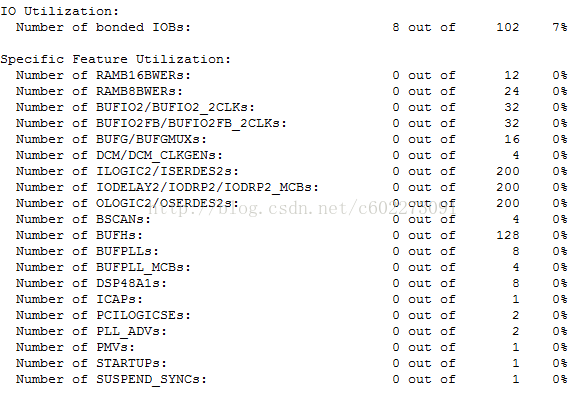

接着可以看到Number of bonded IOBs 8个,聪明的你肯定猜到了,这就是2个输入加上8个输出。

我们看一个设计的资源使用一般就看slice和IO的使用数量哦!

4953

4953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?