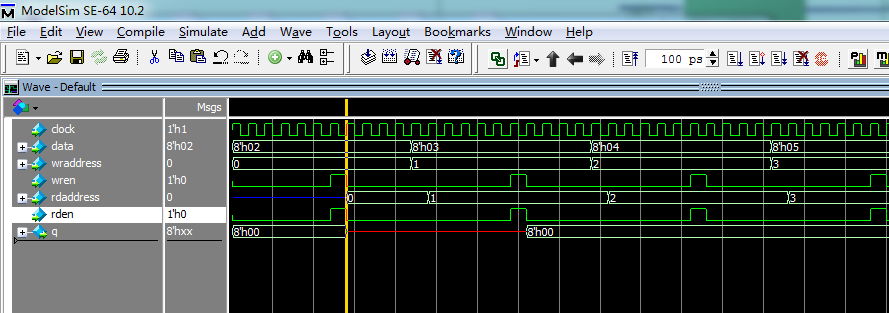

图(1)

关于 reading during writing 的论证

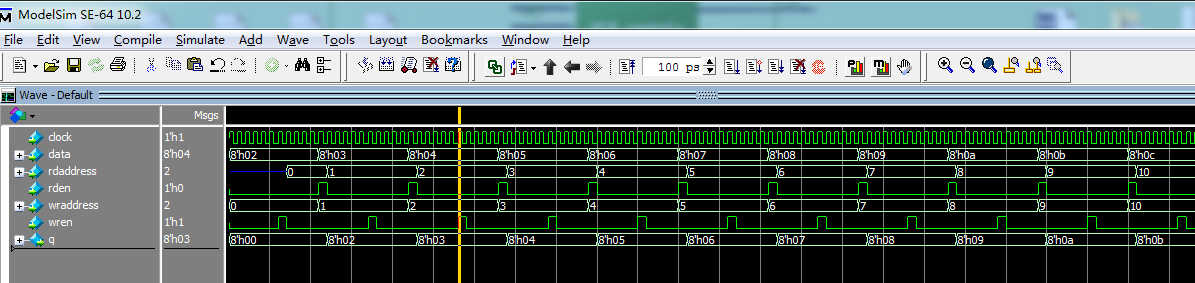

图(2)

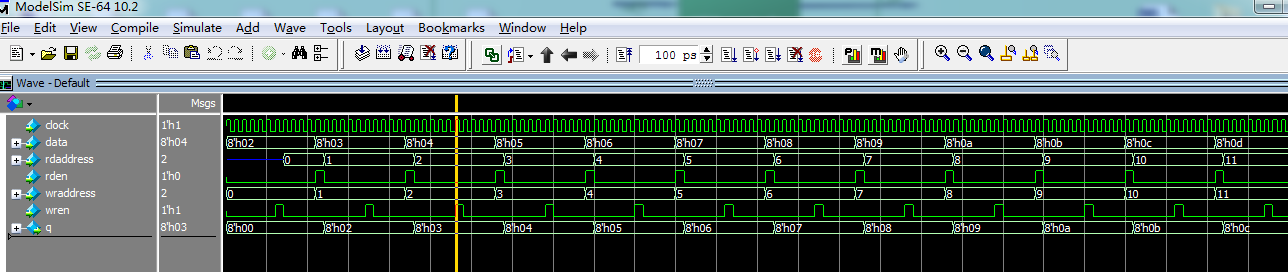

图(3)

第一种情况:

当没有出现 reading during writing 时(也就是 读使能和写使能 同时高低电平同步变),ram的输出 都是一样的。

//============================================================================//

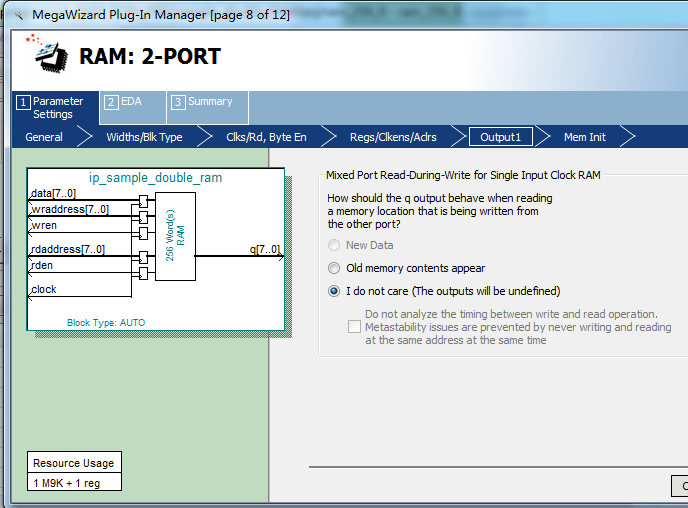

图(4)

图(5)

第二种情况:当我选择 i do not care(The outputs will be undefined),如图(4)所示

图(5)就是ram的输出情况:我的写数据,第一个是8’d2,但是第一个读出来的却是8’h00。

初始状态下,输出默认为8’h00;当读写使能同时为高电平时,读出的数据为不定态 xx;下一个读写使能同步高电平时,读出数据 8’h00;然后不论读使能拉高,输出持续为8’h00;

图(6)

图(6)的前段部分(局部放大)

图(6)后段部分(局部放大)

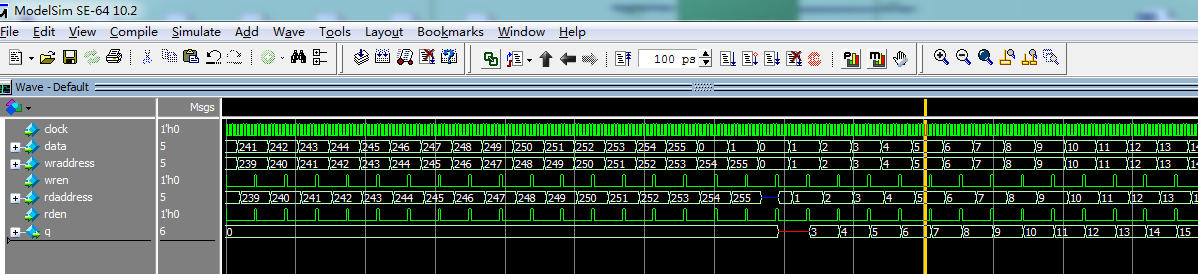

第三种情况:当我选择 old memory contests appear,如图(4)所示

从ram地址0到地址最大处,读出的数据都是 8’h00,(出现红线,是因为我规定了255后是高阻),FPGA的处理是:遇到高阻就是不定态;

当第一轮的数据写完后(第一轮,读出的都是8’h00),第二轮,读写使能同步高低电平时,读出的数据 优先于 写进的数据;

我的写进数据是:

起始点为2,然后不断加1,一直加到255,然后数据变为0,接着0~255周而复始

所以我们看到,读地址为1时,读使能拉高,则数据为3;

//因为第一轮写地址0时,写入的数据为2

//因为第一轮写地址1时,写入的地址为3;

//所以:我们才看的第二轮的数据,读地址为1时,数据为3;

//我观察了随后的波形,第三轮读出的数据为 第二轮写进去的数据;

//我没想到的是,第一轮读数据轮空,第二轮,读写使能同步拉高时,优先读出 第一轮对应地址处数据,然后在同一地址处,写进数据;

2303

2303

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?