1、参考标准:

《IEEE Std 802.3 -2002》

2、接口概述:

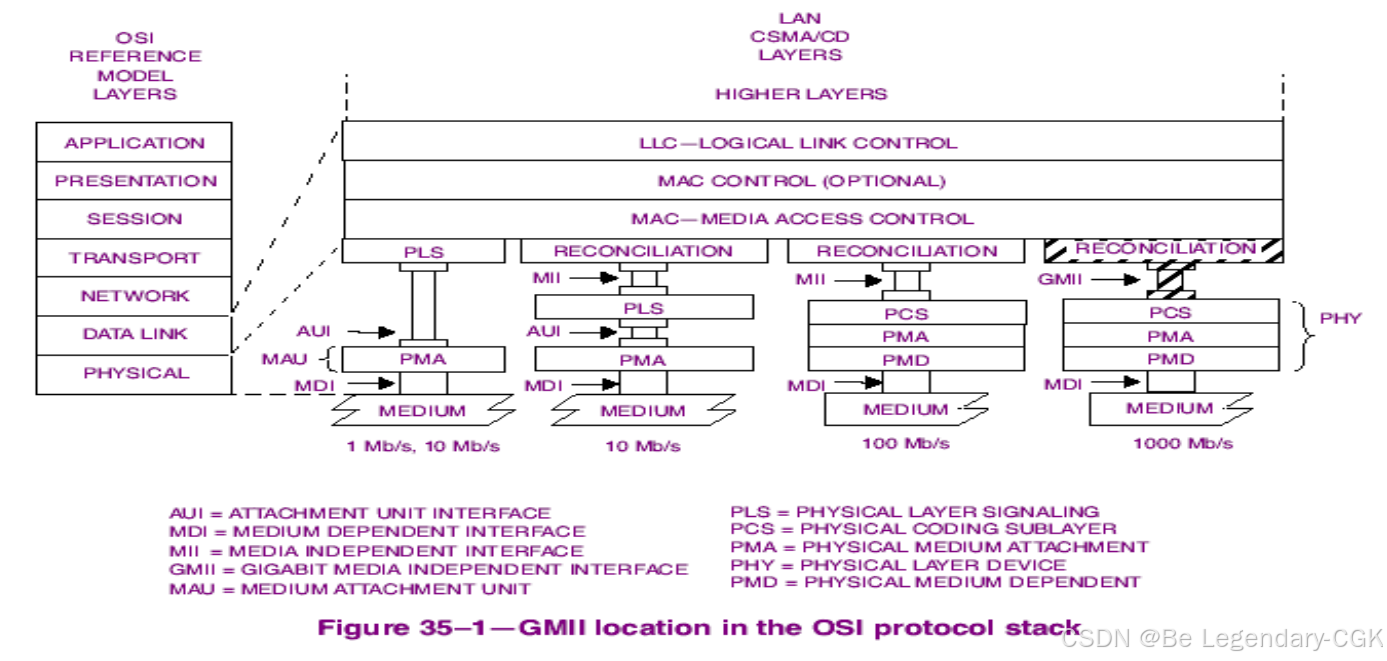

GMII接口是一个工作在125Mhz时钟下的8/10比特宽的数据总线接口。GMII由两个独立的数据通道、接收和发送各个数据通道的控制信号、网络状态信号、各个数据通道的时钟信号以及管理接口信号组成。在GMII中有一个在1000Mb/s速度工作时使用的独立时钟信号,协调子层接口使各种更高速度的PHY可以连接到千兆位MAC引擎上。

图2-1 包含GMII接口的OSI网络模型

GMII(千兆媒质无关接口)接口是在MII接口的基础上发展而来。提供了一种简单,可以容易实现互联且成本低的千兆接口,在MAC和PHY之间提供一条千兆位速率的通路。

GMII(千兆媒质无关接口)接口是在MII接口的基础上发展而来。提供了一种简单,可以容易实现互联且成本低的千兆接口,在MAC和PHY之间提供一条千兆位速率的通路。

- 工作能力达到1000Mb/s

- 独立的8位数据收发通道

- 数据需要时钟同步

- 提供一个简单管理接口

- 支持通用的CMOS接口和部分双极性器件接口

- 提供全双工操作

- 提供向下兼容,兼容MII接口和TBI接口

- 兼容10M及100M传输速率

3、接口信号介绍:

GMII接口为点对点连接,信号线有 GTXCLK、RXCLK、TXD[0:7]、RXD[0:7]、TXER、TXEN、COL、RXER、RXDV、CRS,一共24根信号线。

其中COL和CRS信号与时钟无关,其余信号是时钟同步信号。

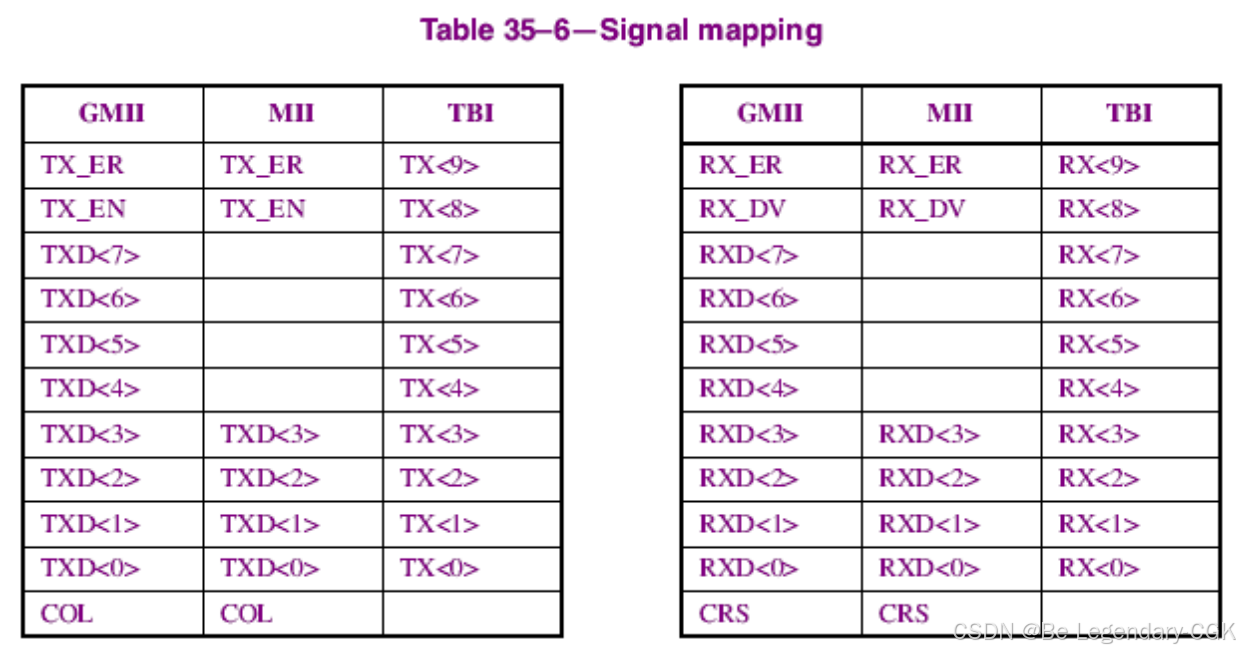

GMII规范规定,GMII接口同MII接口、TBI接口共享信号线,信号对应方式如下图3-1所示。

图3-1 GMII,MII,TBI输入输出引脚定义对照

3.1 信号详细说明:

GTXCLK:1000Mb/S transmit clk, 为TXD[0:7]、TXER、TXEN信号提供参考时钟,由MAC的Reconciliation sublayer层给出信号,PHY 在GTXCLK的上升沿采样。时钟频率为125MHz。

RXCLK:1000Mb/S receive clk, 为RXD[0:7]、RXER、RXDV信号提供参考时钟,由PHY发出信号,由MAC的Reconciliation sublayer层在RXCLK的上升沿采样。

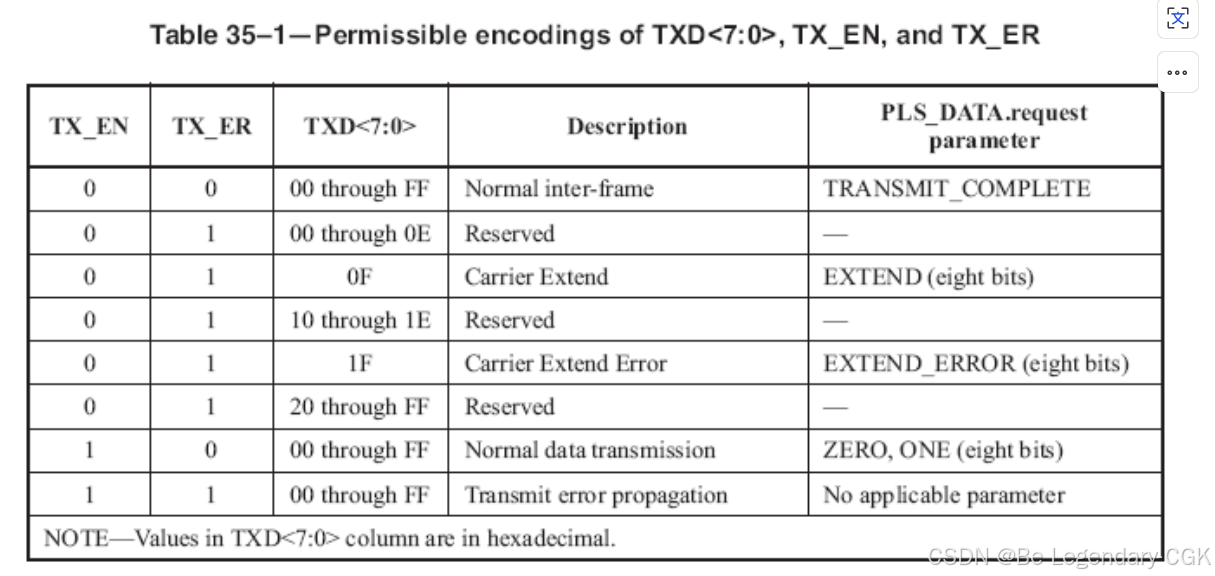

TXEN: Transmit enable ,TXEN和TXER是一起作用表示数据已经由Reconciliation Sublayer 放到GMII接口数据线上,同前导码的第一个字节同时有效,并且保持到所有的传送数据都已经放到GMII接口。TXEN信号是由MAC的Reconciliation sublayer 层提供,与GTXCLK保持同步。

TXER: Transmit code error,TXER有效代表在此段时间内在TXD信号线上传输的数据信号是无效的。TXER信号是由MAC的Reconciliation sublayer 层提供,与GTXCLK保持同步。

TXD:Transmit data,发送数据,8位数据宽度,由MAC 的Reconciliation sublayer提供,与GTXCLK 保持同步。 当TXEN和TXER都无效情况下,TXD上信号是无效的。

TXD,TXEN,TXER 在不同组合下的编码说明如图4-2。

RXDV:Receive data valid,接收数据有效,由PHY驱动,与RXCLK 保持同步,表示已经把经过恢复和解码好的信号放在了数据线上,此信号必须先于帧开始界定符(SFD)有效,在帧结束界定符(EFD)后无效。

RXER:Receive error,RXER有效且在RXDV有效的情况下,通知MAC的Reconciliation sublayer在当前已经发送到RXD信号线上的信号存在错误。RXER由PHY驱动,与RXCLK 保持同步。

RXD:Receive data, 接收数据,8位数据宽度,由PHY提供,与RXCLK 保持同步。

CRS:Carrier sense,由PHY提供,不需要同GTXCLK或RXCLK同步。在用在中继器时,PHY 在接收媒质非空闲状态下驱动CRS有效,在接收媒质空闲状态下,使CRS信号处于无效。 当用在非中继器模式下,PHY工作在半双工模式下时,当接收或发送媒质中任意一个处于非空闲模式下时由PHY驱动CRS有效,在接收和发送媒质都处于空闲模式时,使CRS信号处于无效。

注意:在全双工模式下CRS信号没有定义。

COL:Collision detected,冲突检测。 由PHY驱动,不需要同GTXCLK或RXCLK同步,当检测到媒质上有冲突的时候驱动有效,并且保持到冲突结束。

注意:在全双工模式下CRS信号没有定义。

3.2 不同操作下各个信号工作时序说明:

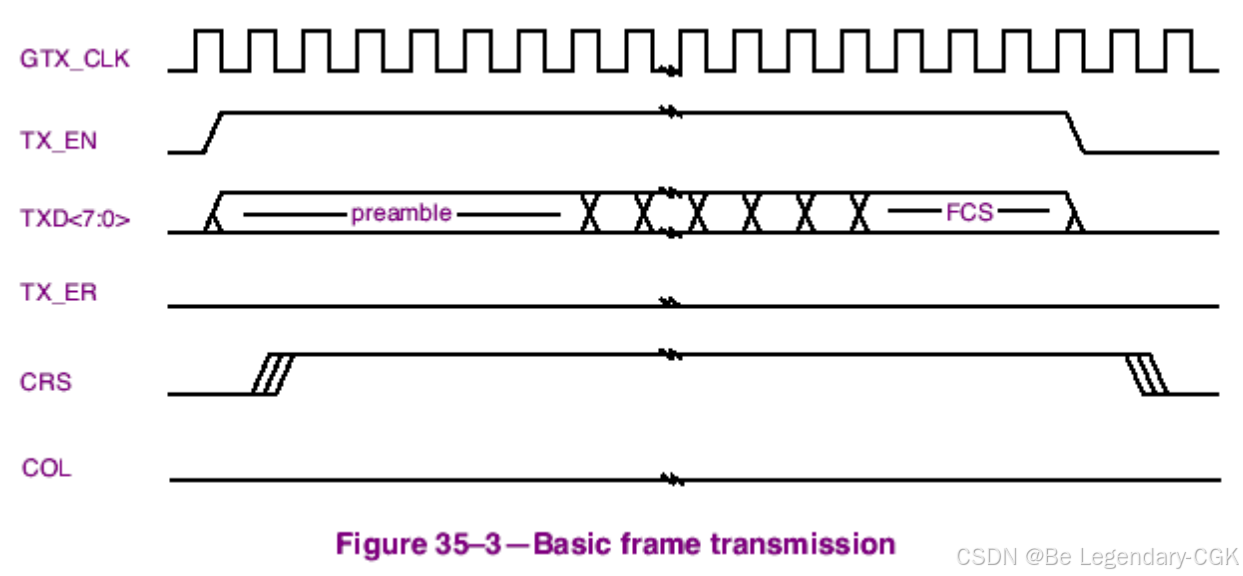

(1)正常帧传输操作:

TXEN在这个帧传输期间保持有效,CRS信号在传输期间保持有效。TXER和COL在整个帧传输过程中保持无效状态。

TXEN在这个帧传输期间保持有效,CRS信号在传输期间保持有效。TXER和COL在整个帧传输过程中保持无效状态。

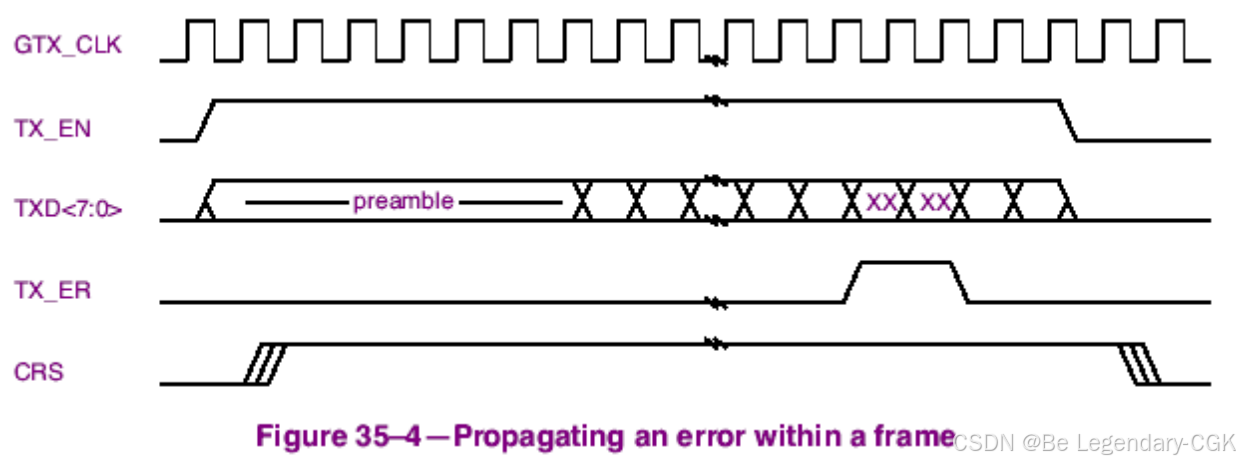

(2)传输中包含错误数据:

在传输过程中,TXEN始终保持有效,TXER 有效期间传输的数据无效。

在传输过程中,TXEN始终保持有效,TXER 有效期间传输的数据无效。

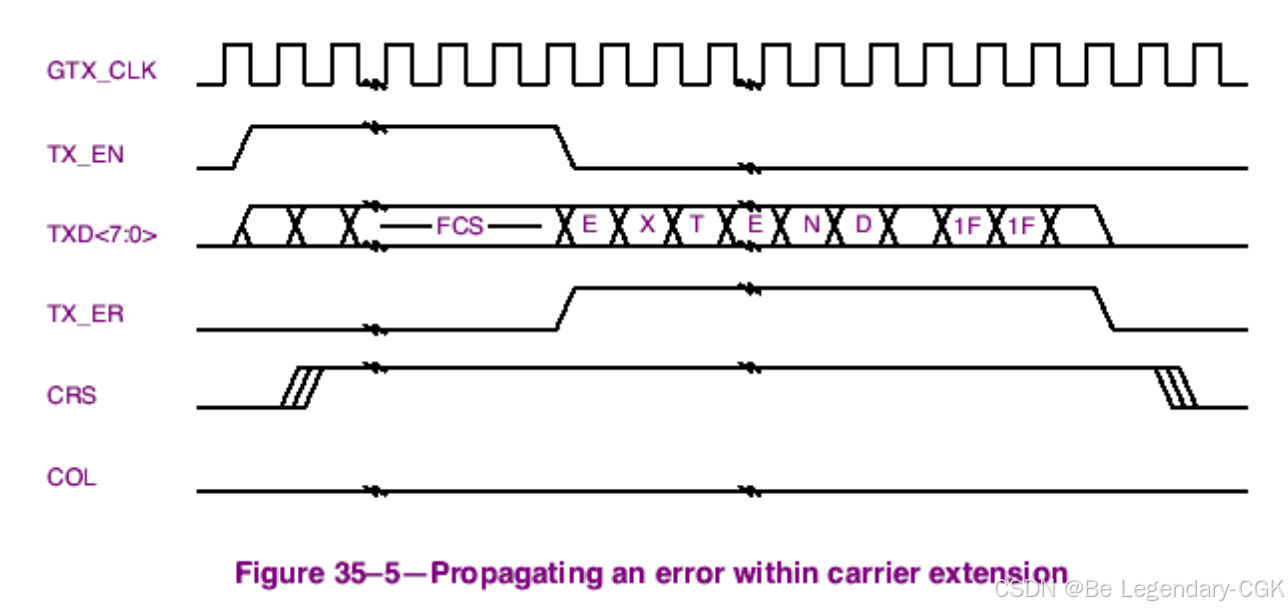

(3)载波扩展错误

CRS信号保持有效,TXEN信号无效,TXER信号有效,TXD上传输的信号为0x1F。

CRS信号保持有效,TXEN信号无效,TXER信号有效,TXD上传输的信号为0x1F。

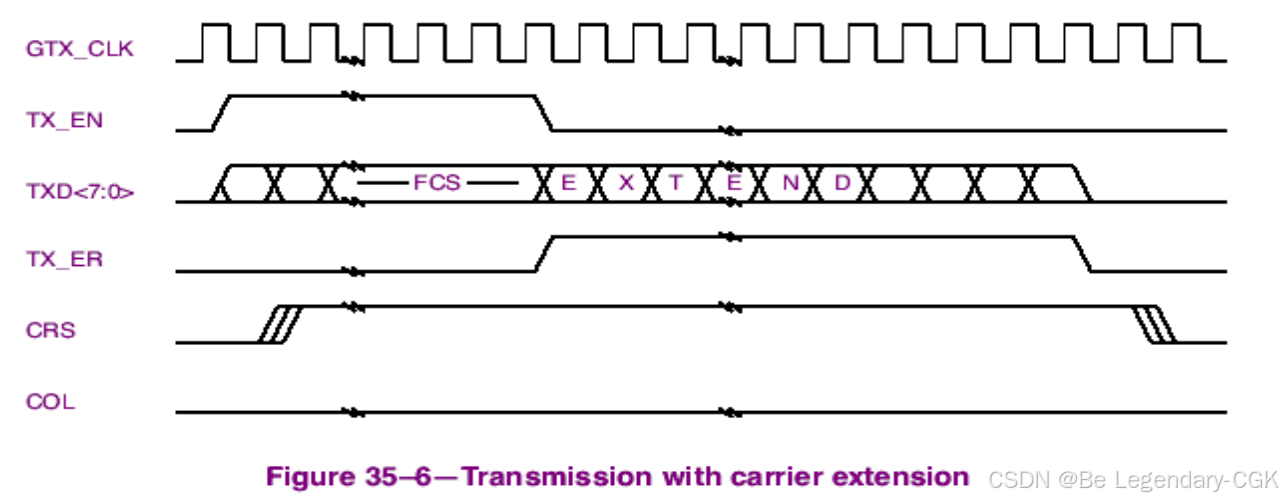

(4)载波扩展

TXEN 无效,CRS在上一个帧传输完后继续保持有效,TXER有效。

TXEN 无效,CRS在上一个帧传输完后继续保持有效,TXER有效。

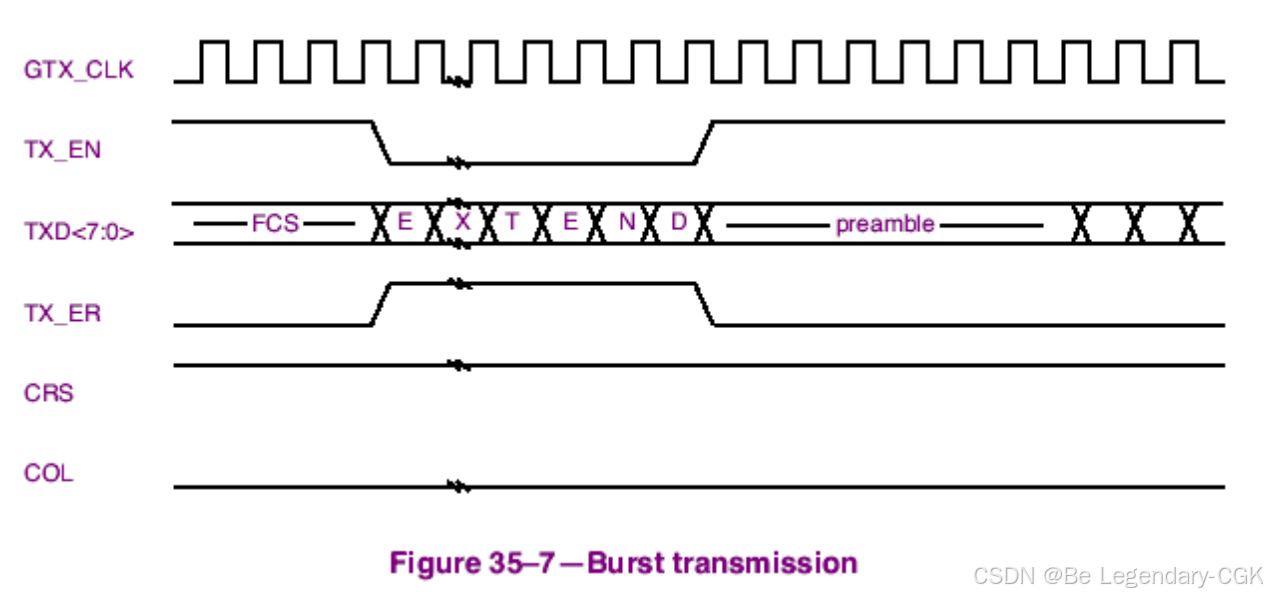

(5)Burst 传输

前一个帧传输完成后经过 一个载波扩展阶段,然后TXER无效,TXEN有效,CRS始终保持有效,开始传送下一个帧。

前一个帧传输完成后经过 一个载波扩展阶段,然后TXER无效,TXEN有效,CRS始终保持有效,开始传送下一个帧。

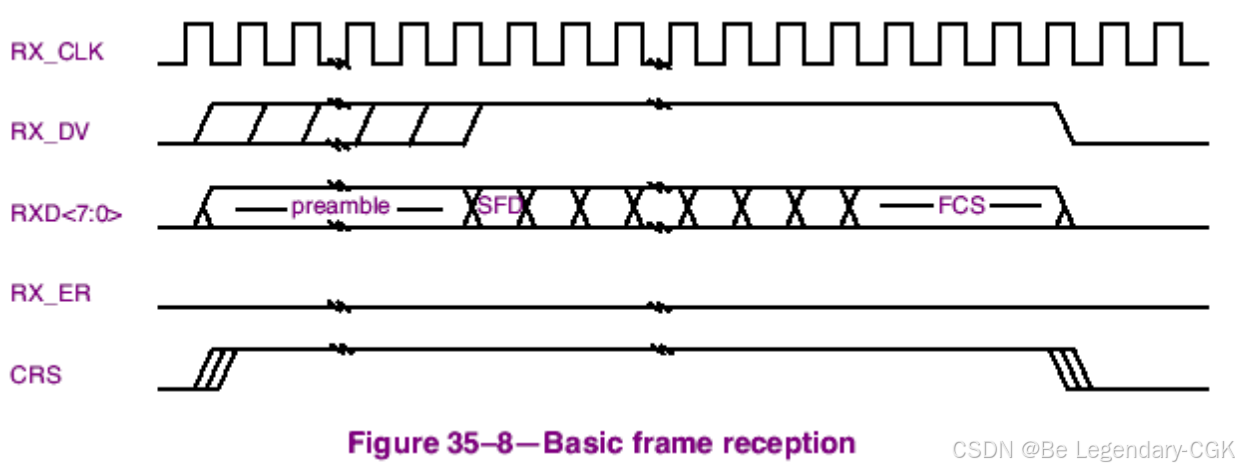

(6)普通帧接收

RXDV在前导码或是SFD 之前有效并保持到帧传输结束,RXER始终无效,CRS在传输过程中保持有效。

RXDV在前导码或是SFD 之前有效并保持到帧传输结束,RXER始终无效,CRS在传输过程中保持有效。

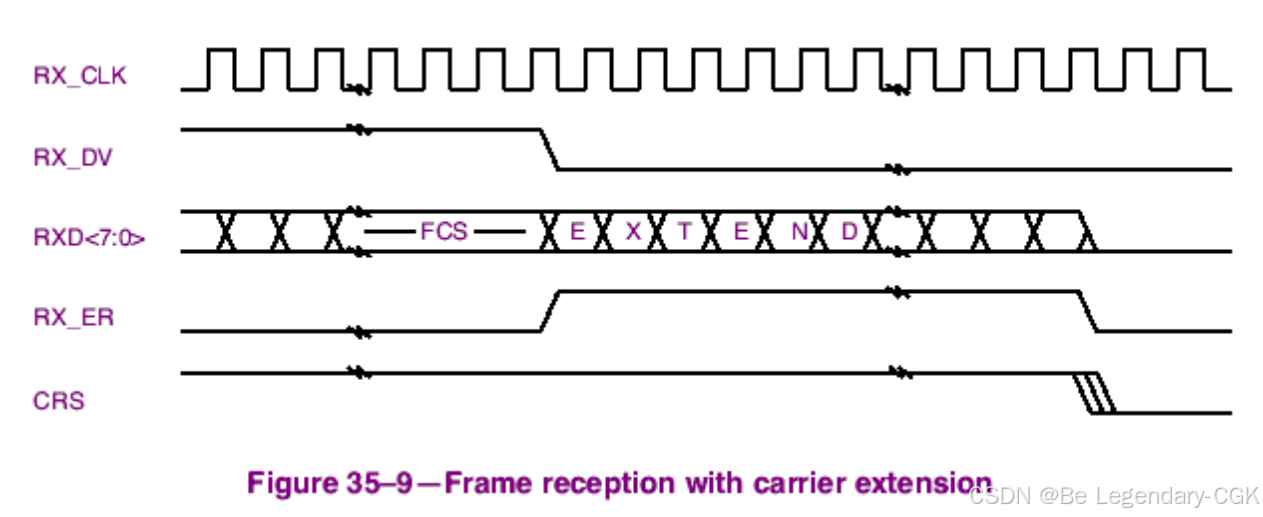

(7)帧接收载波扩展

上一个帧传输结束后,RXDV变为无效,RXER变为有效,CRS信号扩展到RXER无效。

上一个帧传输结束后,RXDV变为无效,RXER变为有效,CRS信号扩展到RXER无效。

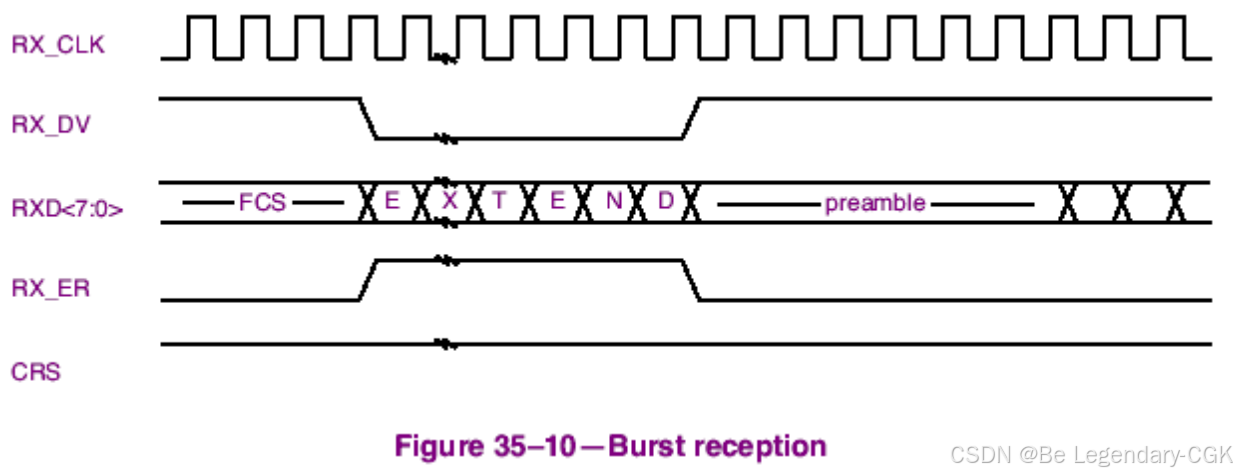

(8)Burst 接收

前一个帧接收完成后经过 一个接收载波扩展阶段,然后RXER无效,RXDV有效,CRS始终保持有效,开始接收下一个帧。

前一个帧接收完成后经过 一个接收载波扩展阶段,然后RXER无效,RXDV有效,CRS始终保持有效,开始接收下一个帧。

(9)帧接收过程中错误

上图中接收有两个错误,一个数据接收错误和一个载波扩展错误。

上图中接收有两个错误,一个数据接收错误和一个载波扩展错误。

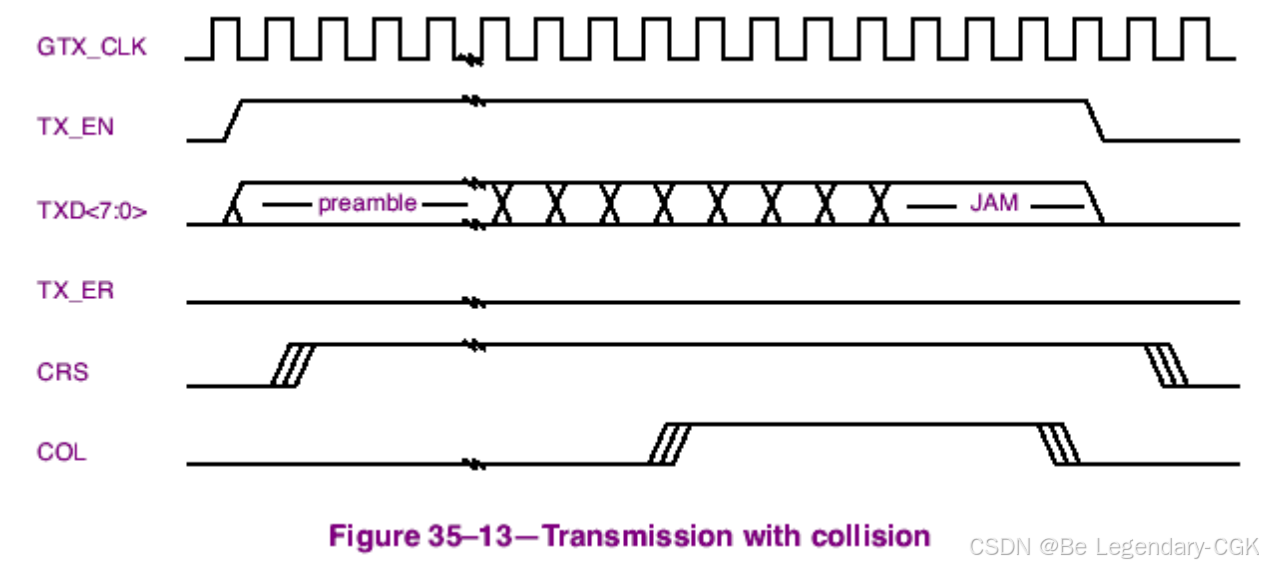

(10)传输中检测到冲突

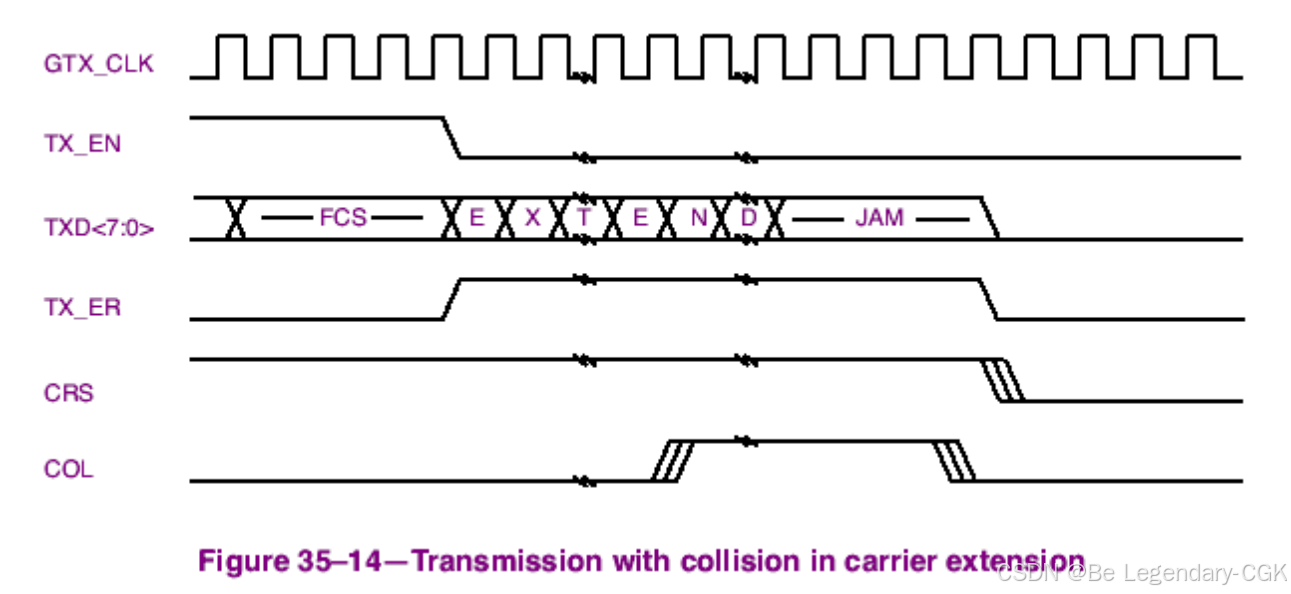

(11)载波扩展中检测到冲突

(11)载波扩展中检测到冲突

4、信号电平:

4、信号电平:

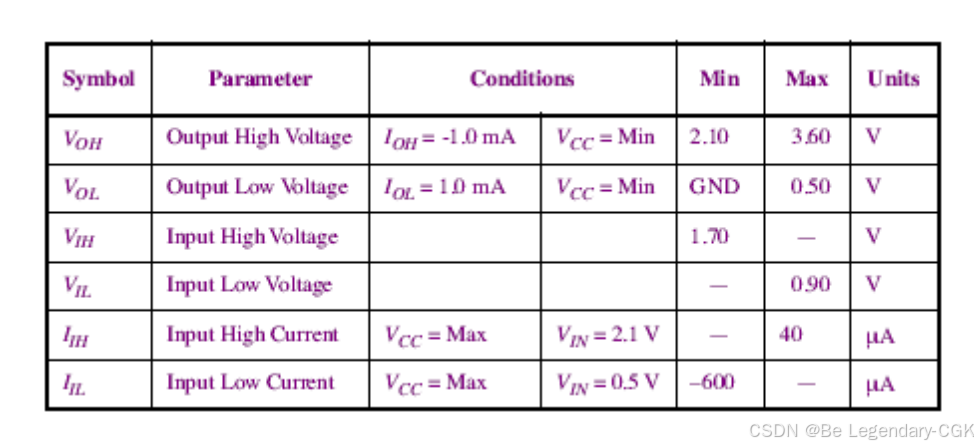

(1) DC指标:

IEEE802.3ae-2002规范指标:

图4-1 GMII接口DC指标

图4-1 GMII接口DC指标

GMII接口允许接收端和发送端供电电压不同,但这两个电压必须满足上述指标。

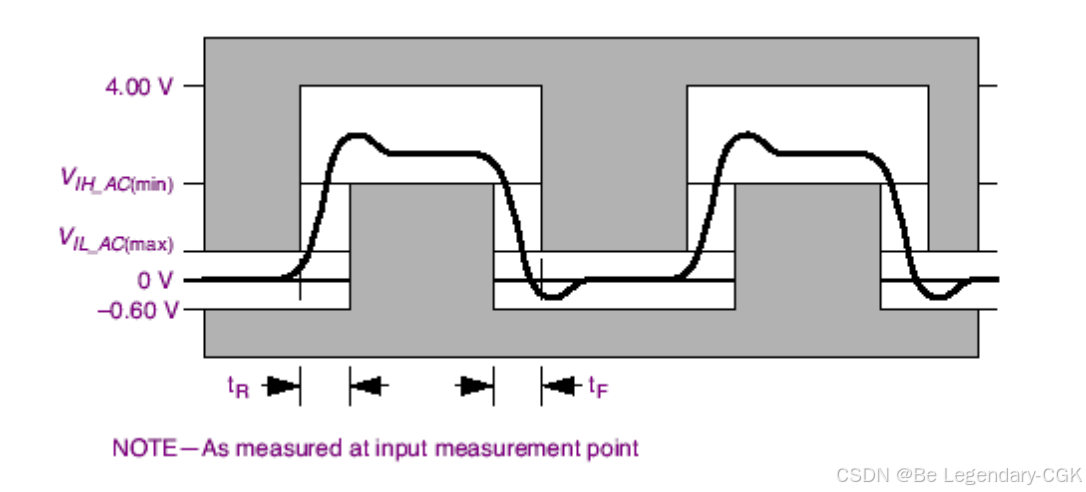

(2) AC 指标:

IEEE802.3ae-2002规范指出,所有的GMII接口信号都是点对点连接。对于GMII接口接收端信号电压,IEEE802.3ae-2002规范给出了一个模板,如图4-2 。

图4-2 GMII接口接收端信号电压模板

图4-2 GMII接口接收端信号电压模板

注意:GMII 接口信号容许的最高电平是4V,最低是-0.6V。

在实际应用中,具体指标需参考接口芯片的DataSheet,且指标不能超出规范要求。

5、PCB及原理设计要点:

PCB设计要点:IEEE802.3ae-2002规范没有给出PCB设计要求 。 在实际设计中,一般要求进行阻抗控制,单端阻抗控制在50欧。且要求TXD、GTXCLK、TXEN、TXER信号之间作等长处理,RXD、RXCLK、RXDV、RXER信号之间做等长处理。

原理设计要点:所有信号一对一连接,尽可能不分叉。一般要求要在信号的发送端根据走线长短和芯片特性加上相应的阻抗匹配电路。

6、信号速率及带宽:

GMII 接口工作频率最高为125MHz ,数据通路为8位并行通路,且GMII接口上传送的信号不需经过编码,故信号带宽最高为125* 8=1000 Mbps。

由于GMII接口要向下兼容,故GMII接口必须支持1000M、100M及10M的工作带宽。在不同的工作带宽下,接口信号的工作频率如表5-1:

表6-1

| 工作带宽 | 时钟频率 | 数据位宽 | 备注(使用的信号线) |

| 1000M | 125MHz | 8 bit | TXD[7:0];RXD[7:0] |

| 100M | 25MHz | 4 bit | TXD[3:0];RXD[3:0] |

| 10M | 2.5MHz | 4bit | TXD[3:0];RXD[3:0] |

7、编码方式:

GMII 接口是基于MII接口的,在数据传输中不对数据进行编码,TXD、RXD数据线直接传送原始数据。控制信息由TXEN、TXER、RXDV、RXER、COL、CRS 信号线传送。

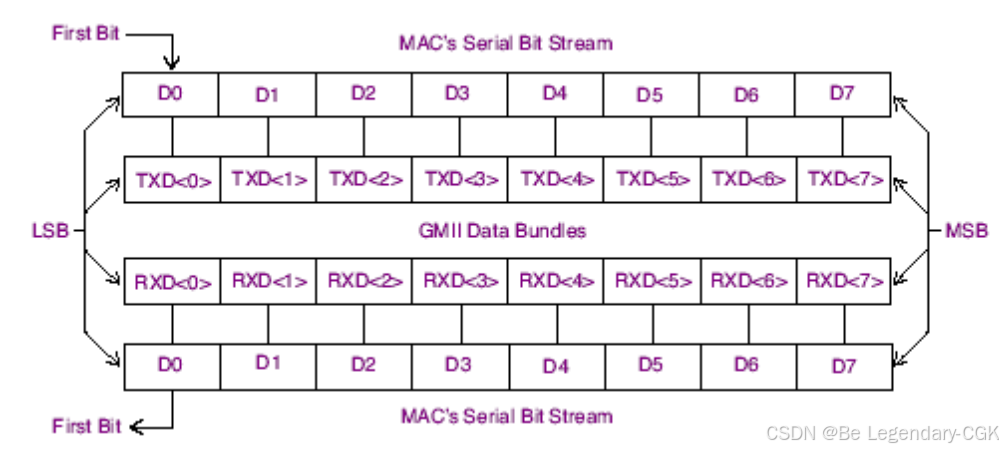

GMII传输帧格式如下图7-1所示:

图7-1 GMII传输帧格式

图7-1 GMII传输帧格式

GMII接口发送和接收数据位都为8位宽度,故一个时钟周期可以传输和接收一个字节的数据,每个数据位对应的数据如图7-2所示:

图7-2

图7-2

TXD,TXEN,TXER 在不同操作下的编码说明如图7-3。

图7-3TXEN、TXER、TXD编码表

图7-3TXEN、TXER、TXD编码表

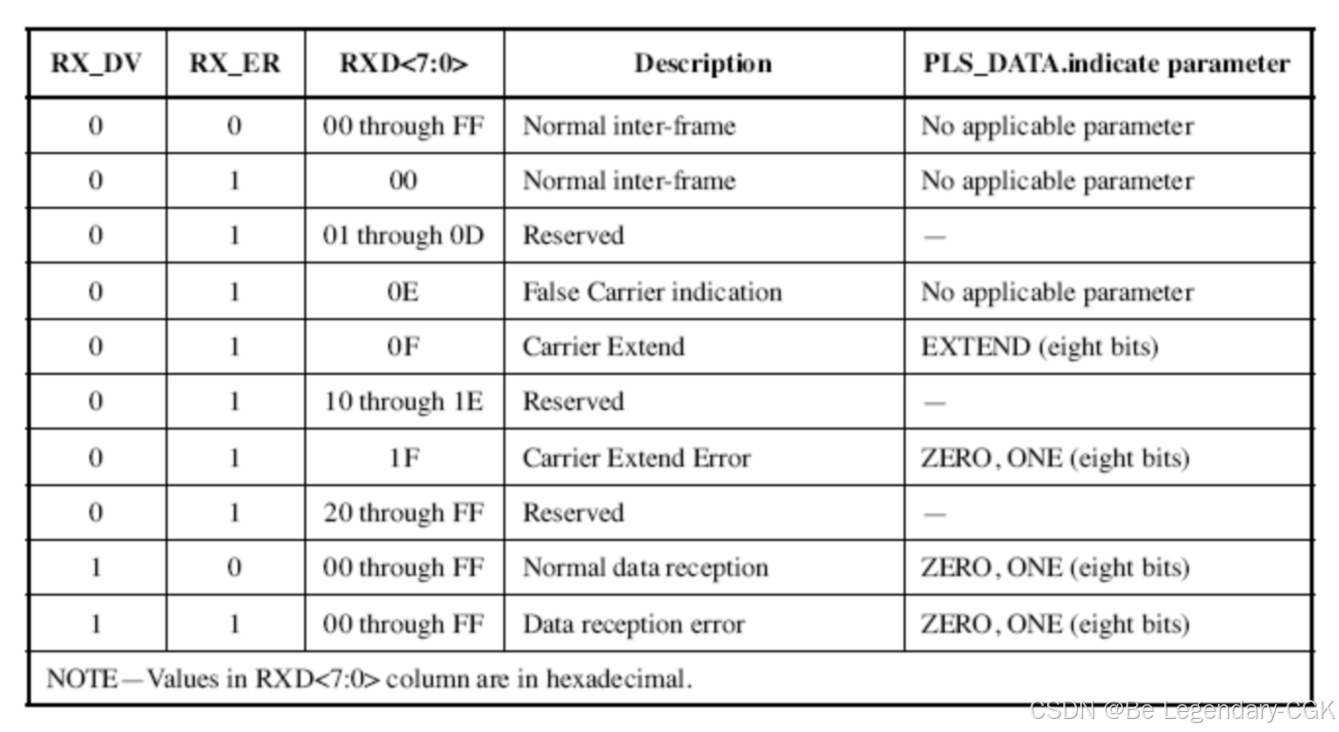

RXD,RXDV,RXER 在不同操作下的编码说明如图7-4。

图7-4 RXDV、RXER、RXD编码表

图7-4 RXDV、RXER、RXD编码表

8、测试指标

GMII 接口信号测试分为两类,一类是电气测试,一类是时序测试。

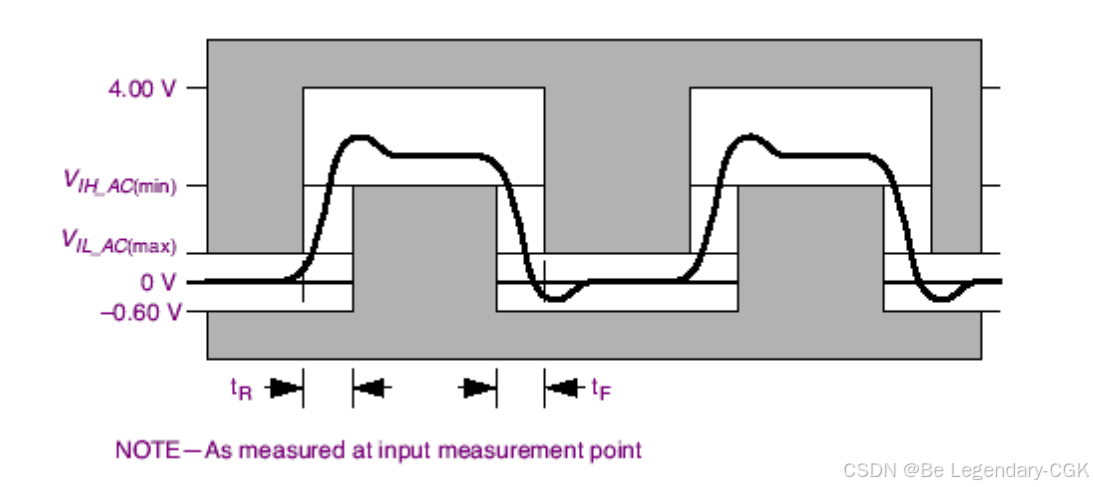

8.1 电气指标: 信号电平过冲最高不能超过4V,最低过冲不能低于-0.6V。如图8-1:

图8-1

图8-1

8.2 时序指标:

IEEE802.3-2002规范规定,所有的GMII接口时序指标都是在信号接收端测量。

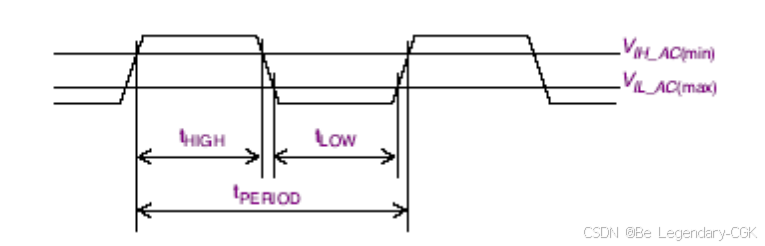

GMII 时钟信号测量参数如图8-2:

图8-2 GTXCLK及RXCLK测试参数

图8-2 GTXCLK及RXCLK测试参数

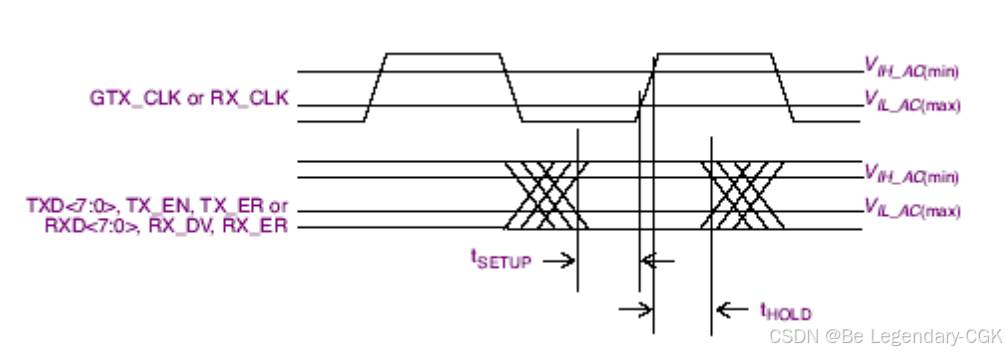

GMII 信号时序测量参数如图8-3:

图8-3 GMII 信号时序测试参数

图8-3 GMII 信号时序测试参数

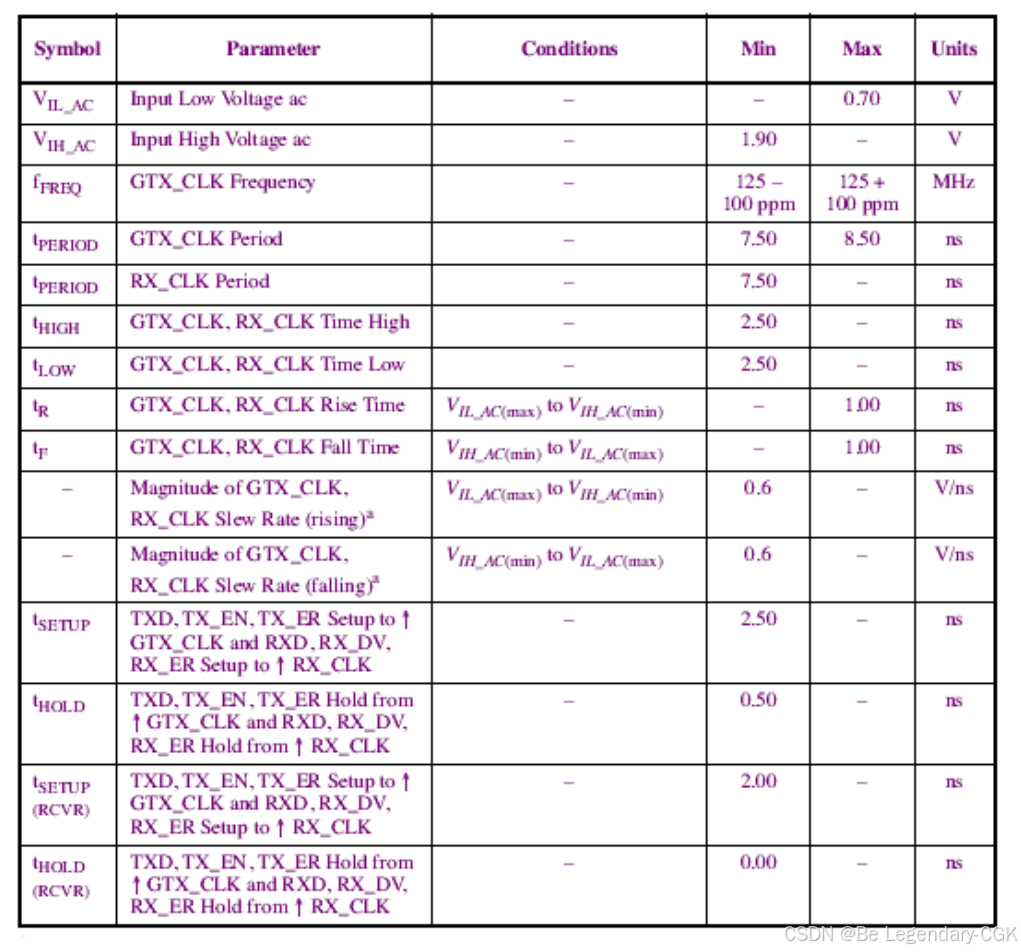

IEEE802.3ae-2002规范规定的GMII信号时序指标规范如图8-4:

图8-4 GMII 时序指标

图8-4 GMII 时序指标

图8-4 给出了两组Tsetup 和Thold 指标,第一组是在理想情况下,即CLK与Data是完全同步情况下的时序指标。第二组是CLK与Data不是完全同步,两者经过PCB走线后到达接收端时的时延不同,定义了一种最恶劣的情况下的指标。

9、应用环境

实现不同媒质千兆PHY 同千兆MAC 之间的连接,GMII仅支持板上连接,可以通过PCB板在有限的距离内实现连接,不支持使用电缆连接。

94

94

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?