RS485/RS232通信协议并不是单独协议,只是电气层的协议,依赖于串口。

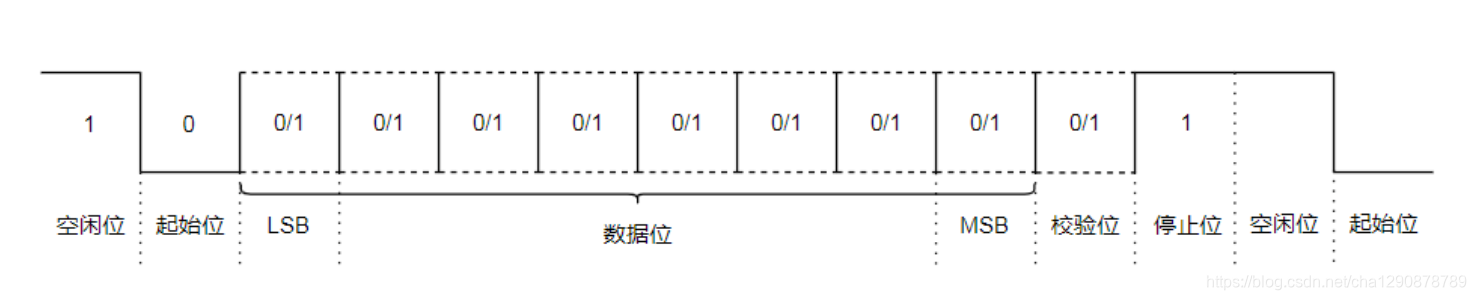

UART帧格式

1位起始位;

5-8位数据位(先发低位,后发高位);

校验位(可有可无);

(1/1.5/2位)停止位;

uart存在的问题:

电气接口不统一:

uart只是对信号的时序进行了定义,而未定义接口的电气特性;

uart通信时一般直接使用处理器使用的电平,即TTL电平,但不同的处理器使用的电平存在差异,所以不同的而处理器使用uart通信时一般不能直接相连;

uart没有规定不同器件连接时连接器的标准,所以不同器件之间通过uart通信时连接很不方便。

抗干扰能力差

uart一般直接使用TTL信号来表示0和1,但TTL信号的抗干扰能力差,数据在传输过程中很容易出错。

通信距离短:

因为TTL信号的抗干扰能力较差,所以其通信距离很短,一般只能用于一个电路板上的两个不同芯片之间的通信。

RS232:

软件层面与串口通信一样。

信号:

该标准规定逻辑1的电平为-5~-15V,逻辑0电平为+5v ~+15V,选用该电气标准的目的在于提高抗干扰能力,增大通信距离,其传输距离一般可达到15M;但是处理器一般都是TTL信号不符合RS232标准,所以一般还需要在处理器外部添加电路对信号电平进行转换两个器件之间通信的时候,两个器件都需要添加电平转换芯片。

232存在的问题

接口的信号电平值较高,已损坏接口电路芯片,又因为与TTL电平不兼容,所以需要使用电平转换芯片才能与TTL电路连接;

通信速度较低;

易产生共模干扰。抗噪声干扰性弱;

传输距离短;

RS485:

软件层面与串口通信一样。

能在远距离条件下以及电子噪声大的环境下有效传输信号,该标准允许连接多个收发器,具有多站能力。

信号:

RS485采用差分信号进行数据传输,两线之间电压差为+2V~+6V表示逻辑1,两线之间的电压差为-2V ~-6V表示逻辑0;使用差分信号能有效地减少噪声信号的干扰,延长通信距离,RS485的通信距离可以达到1500m;接口电路电平比232降低了,所以不易损坏接口电路芯片,且与TTL电平兼容,可方便地与TTL电路连接。485通信通常使用双绞线。

接口

采用两线制,这种接线方式为总线式拓扑结构,在同一条总线上可以同时存在多个结点,因为采用的是两线制,数据的发送和接受都要使用这对差分信号线,发送和接受不能同时进行,所以只能采用半双工的方式进行工作,编程时也需要加以处理。使用RS485一般还需要在处理器的外部添加电路将TTL信号转换为差分信号。

RS485优势:

接口信号电平值比较低,不易损坏接口电路的芯片,且与TTL电平兼容,可方便地与TTL电路连接。

通信速度快;

抗噪声干扰性强;

传输距离较远;

可实现多接地那组网;

SPI:

是一个同步的数据总线,也就是说它是用单独的数据线和一个单独的时钟信号来保证发送端和接收端的完美同步。

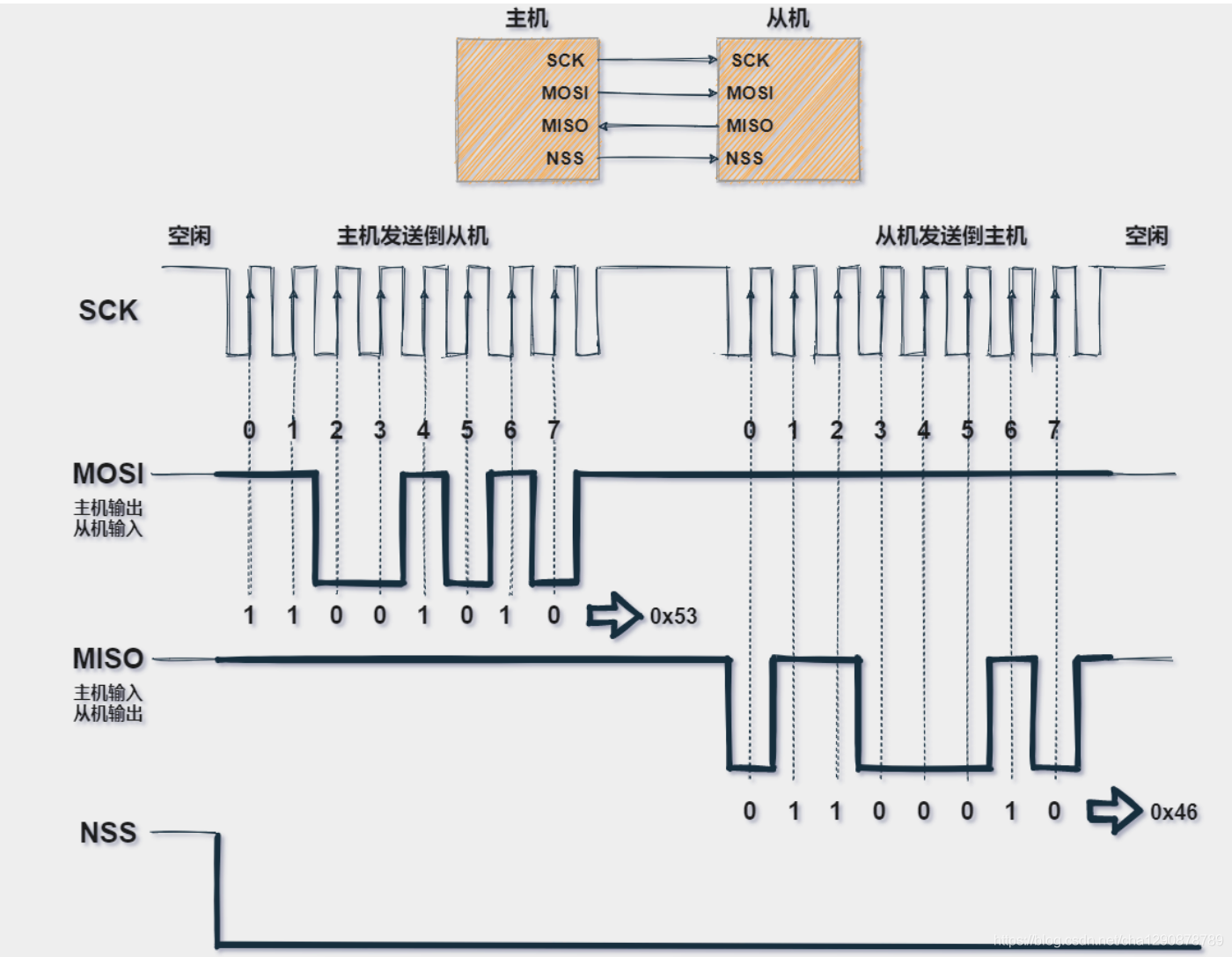

产生时钟的一侧称为主机,另一侧称为从机。总是只有一个主机(一般来说可以是微控制器/MCU),但是可以有多个从机。

数据的采集时机可能是时钟信号的上升沿(从低到高)或下降沿(从高到低)。

整体的传输大概可以分为以下几个过程:

1 主机先将NSS信号拉低,这样保证开始接收数据;

2 当接收端检测到时钟的边沿信号时,它将立即读取数据线上的信号,这样就得到了一位数据(1bit);

3 由于时钟是随数据一起发送的,因此指定数据的传输速度并不重要,尽管设备将具有可以运行的最高速度。

主机发送到从机时:主机产生相应的时钟信号,然后数据一位一位地将从MOSI信号线上进行发送到从机;

主机接收从机数据:如果从机需要将数据发送回主机,则主机将继续生成预定数量的时钟信号,并且从机会将数据通过MISO信号线发送;

无应答,速度快;

4根线:SCLK、MOSI/SDO(主机输出从机输入)、MISO/SDI(主机输入从机输出)、CS/SS

SPI总线包括4条逻辑线,定义如下:

MISO:Master input slave output 主机输入,从机输出(数据来自从机);

MOSI:Master output slave input 主机输出,从机输入(数据来自主机);

SCLK :Serial Clock 串行时钟信号,由主机产生发送给从机;

SS:Slave Select 片选信号,由主机发送,以控制与哪个从机通信,通常是低电平有效信号。

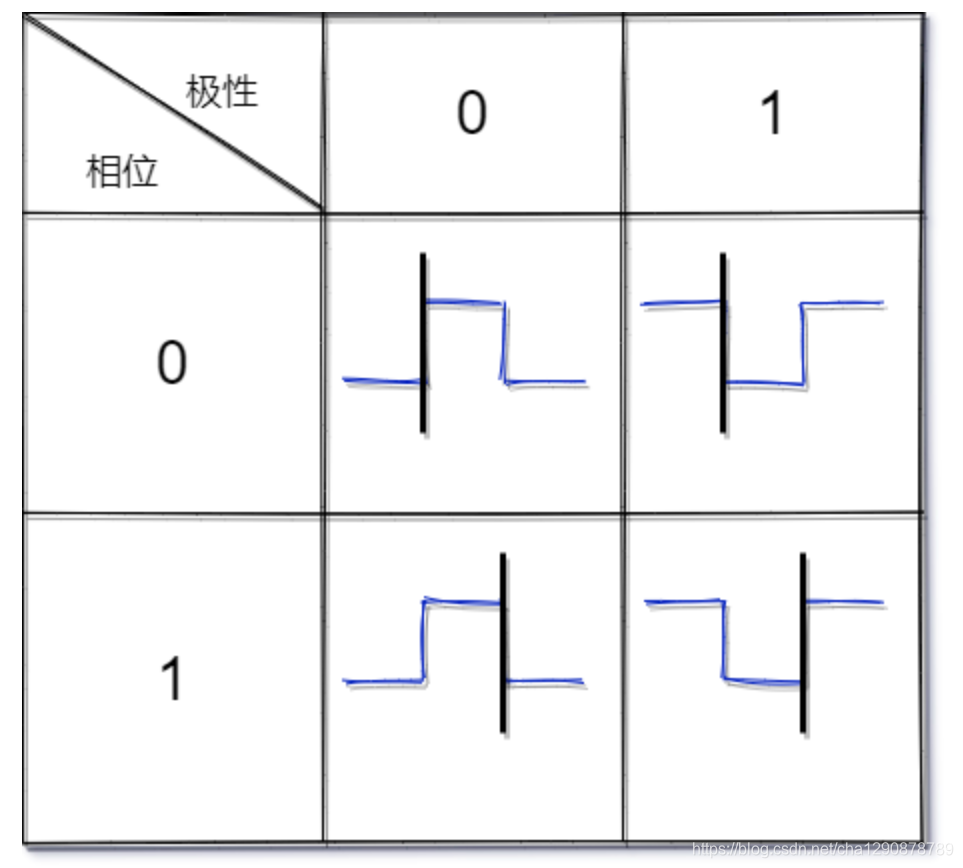

4中通信模式:

CPOL:时钟极性;

CPHA:时钟相位;

该图片拷贝自某博主博客,但是忘记是哪位博主。

SPI是“全双工”(具有单独的发送和接收线路)因此可以在同一时间发送和接收数据,另外SPI的接收硬件可以是一个简单的移位寄存器。

时钟极性 CKP/Clock Polarity

除了配置串行时钟速率(频率)外,SPI主设备还需要配置时钟极性。

根据硬件制造商的命名规则不同,时钟极性通常写为CKP或CPOL。时钟极性和相位共同决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据;

CKP可以配置为1或0。这意味着您可以根据需要将时钟的默认状态(IDLE)设置为高或低。极性反转可以通过简单的逻辑逆变器实现。

CKP = 0:时钟空闲IDLE为低电平 0;

CKP = 1:时钟空闲IDLE为高电平1;

时钟相位 CKE /Clock Phase (Edge)

除配置串行时钟速率和极性外,SPI主设备还应配置时钟相位(或边沿)。根据硬件制造商的不同,时钟相位通常写为CKE或CPHA;

顾名思义,时钟相位/边沿,也就是采集数据时是在时钟信号的具体相位或者边沿;

CKE = 0:在时钟信号SCK的第一个跳变沿采样;

CKE = 1:在时钟信号SCK的第二个跳变沿采样;

该图片同样拷贝自之前那位博主博客。

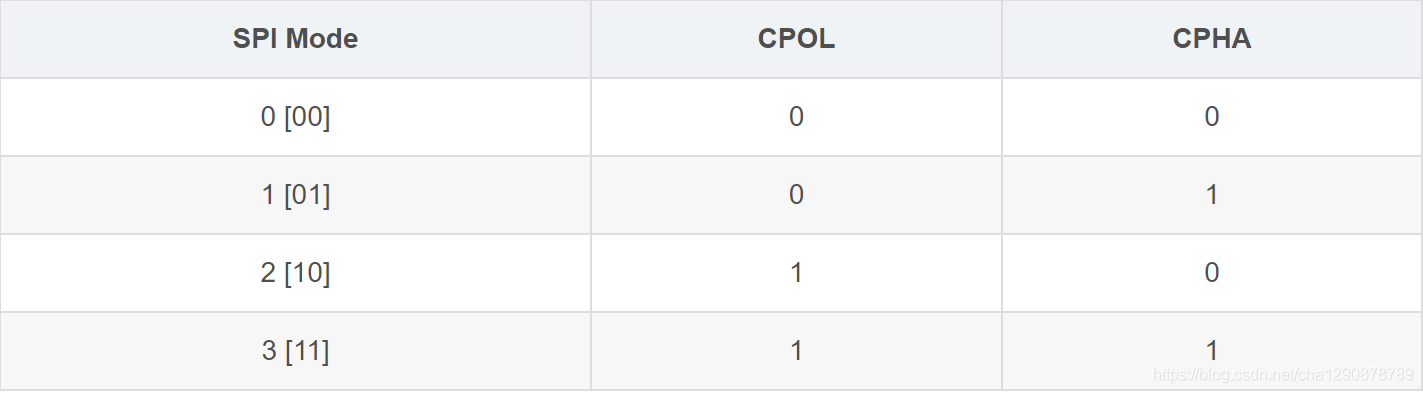

模式编号

SPI的时钟极性和相位的配置通常称为 SPI模式,所有可能的模式都遵循以下约定;具体如下表所示;

本文详细介绍了UART、RS232和RS485三种串行通信协议的原理、优缺点。UART是基本的串口通信协议,电气特性不统一,抗干扰能力弱,通信距离短。RS232通过高电压差分信号提高了抗干扰能力,但速度慢,接口不兼容TTL。RS485采用差分信号,适合长距离、多节点通信,但仍是半双工。SPI则是一种全双工同步总线,支持多从机,具有高速传输和四种通信模式的特点。

本文详细介绍了UART、RS232和RS485三种串行通信协议的原理、优缺点。UART是基本的串口通信协议,电气特性不统一,抗干扰能力弱,通信距离短。RS232通过高电压差分信号提高了抗干扰能力,但速度慢,接口不兼容TTL。RS485采用差分信号,适合长距离、多节点通信,但仍是半双工。SPI则是一种全双工同步总线,支持多从机,具有高速传输和四种通信模式的特点。

704

704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?