目录

1. CAN(Controller Area Network 控制器 域 网络)

2. UART(Universal Asychronous Receiver Transmitter)

1. CAN(Controller Area Network 控制器 域 网络)

1.1 CAN简介

异步半双工串行通信协议

1.1.1 总线制

(1)CAN由一对差分对(两条线)CANH和CANL组成

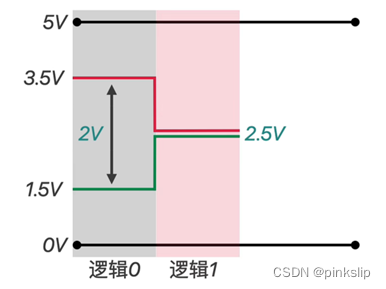

(2)CANH电压比CANL高视为逻辑0(显性电平),否则为逻辑1(隐形电平)

显性电平与阴性电平

(3)多个设备可以连接到同一条CAN上

(4)总线设备通过ID号区分

(5)ID号长度为11位(标准长度)或29位(拓展长度)

1.1.2 CAN2.0b标准

(1)最大速率1Mbps

(2)一组数据称作一帧,分为数据帧和远程帧(不常用),远程帧不传输数据

(用来告诉设备,马上发送数据)

(3)数据帧最多传输8个字节的数据

(4)每一帧都有CRC校验

1.1.3 CAN FD 标准

(1)最大速率可达8Mbps

(2)数据帧最多可传输64字节数据

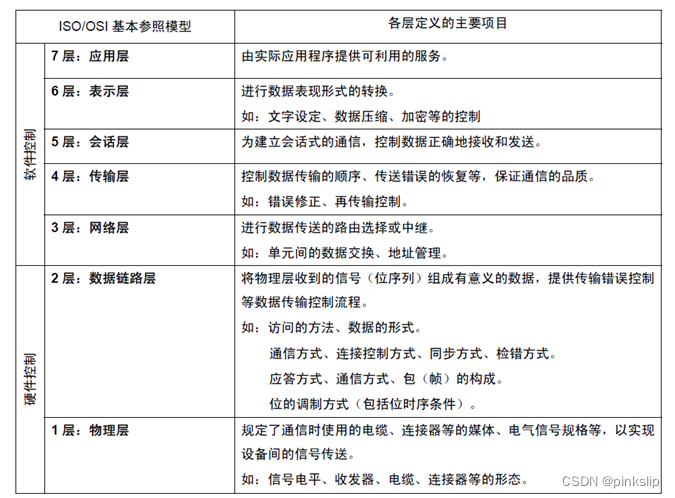

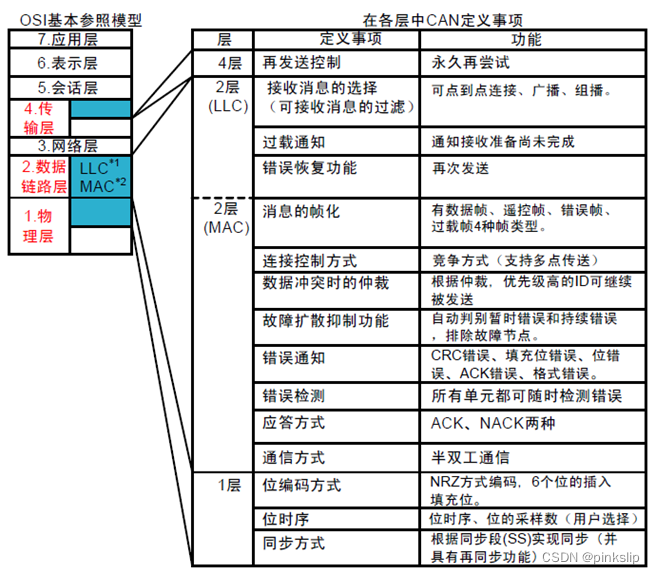

1.1.4 CAN的层(传输层、数据链路层、物理层)

ISO/OSI基本参照模型

ISO/OSI基本参照模型和CAN协议

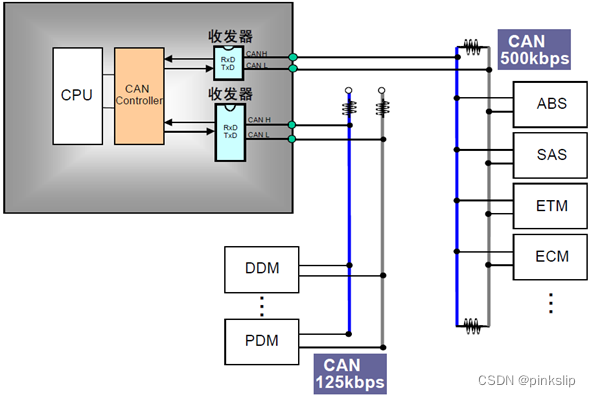

CAN RX/CAN TX需要经过CAN收发器(Transceiver)才能被转换为对应的差分电平(CAN H/CAN L)。

一般CAN差分信号的电压为0~5V,也可以0~3.3V(不建议,兼容性差)

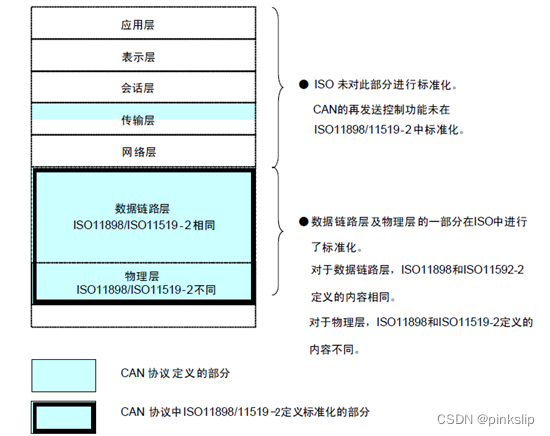

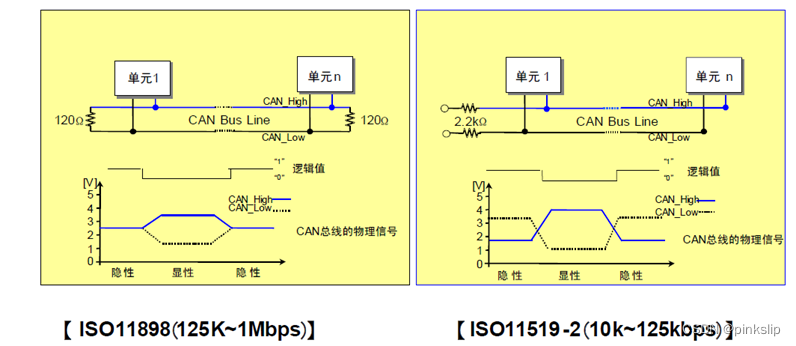

1.1.5 ISO 标准化的CAN 协议

(1)ISO11898

ISO11898 是通信速度为125kbps-1Mbps 的CAN 高速通信标准。

(2)ISO11519

ISO11898 是通信速度为125kbps-1Mbps 的CAN 高速通信标准。

ISO标准化的CAN协议

ISO11898 与ISO11519-2 的物理层的规格不同,每种规格需要有专门的驱动IC与之相对应。

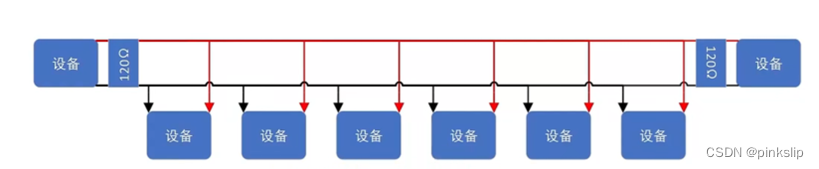

1.2 CAN的总线结构

CAN有两个120Ω终端电阻,位于CAN布线两端

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

786

786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?