背景:细分领域的半导体龙头企业,BSP驱动开发。

目的:1.总结开发经验,构建我的嵌入式体系架构。2.总结工程项目经验,探讨清楚工作的本质。

序:我在公司的工作分为两个部分:BSP驱动开发和对接客户的FAE工作。而BSP驱动开发又主要分成两个部分:1.第三方库的代码移植以及调试工作。2.Norflash模块驱动管理。于此同时,FAE的任务是服务客户,与客户对齐复现项目的问题点。

Norflash模块驱动管理

首先norflash是一个常用的储存器,它的主要作用是:XIP功能和储存数据。它能直接成为CPU的代码执行介质,也就是说是SRAM的后备役。 实际工程使用中,我一共接到了三种不同的需求:

1.给主核芯片外挂一个新型号的Norflash

2.Norflash在实际使用中,跑的代码挂掉,需DEBUG

3.芯片的J-LINK烧录所需的flashloader烧录算法

外挂新的flash

这是我初入职场时接到的第一个正式项目,说实话一开始还是非常懵逼的。如何把一个新的储存器接入到公司的芯片?经过漫长的经验总结,无非以下几个步骤:

第一,调试FLASH的代码必然是运行在SRAM的,在公司代码框架中找到对应跑SRAM的代码(target)

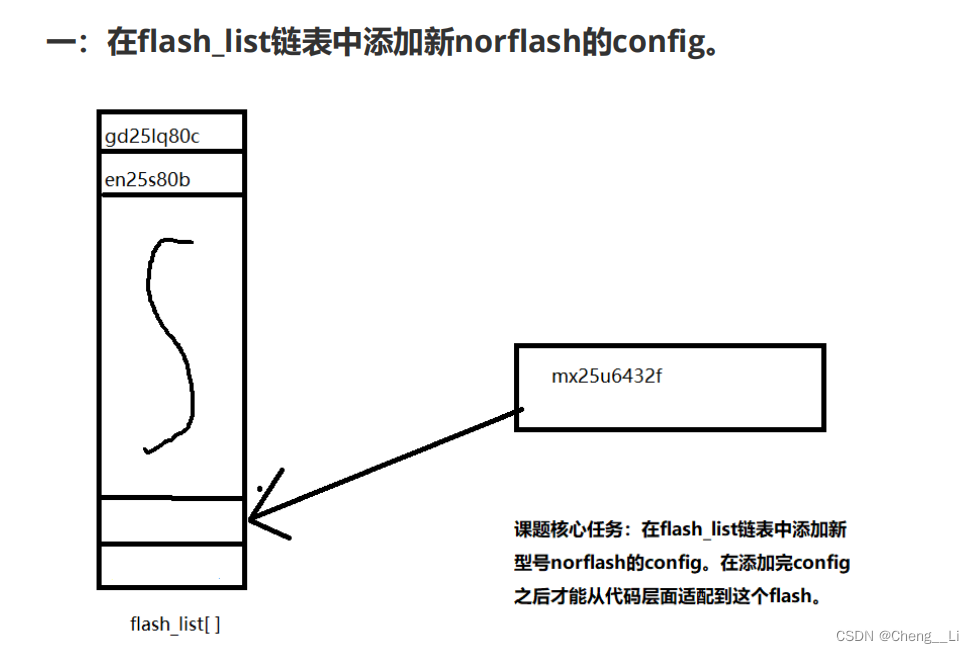

第二:Norflash型号极多,这些不同型号的Norflash参数,我们将其设置成一个节点,并把这些节点挂在一个链表上面。

第三:怎么才能锁定你所需要型号的Norflash参数呢?答案是硬件ID,通过SPI接口循环发送9F命令,Norflash返回相应的ID号,主控芯片获取该ID号之后,遍历链表找到相应的Norflash各种参数,以进行后续操作。

第四:使用Norflash有许多参数要参考其原厂的datasheet。比如:开启DTR模式设定的dummy值;开启四线读模式设定的wrap相关的值;

第五:跑过测试程序。注意这里的测试框架已经构建好了,本质是对整一块Norflash进行读写擦除。

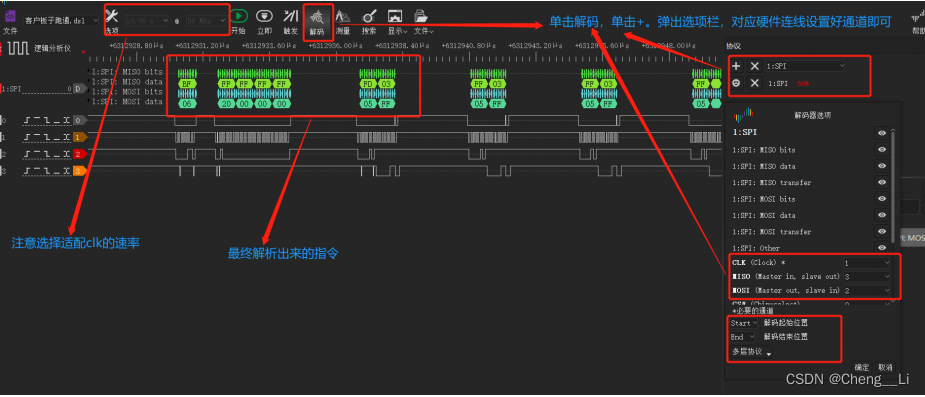

第六:DEBUG。实际过程中肯定不会这么顺利地就完成以上四个步骤。所以逻辑分析仪显得尤为重要,这里我们需要找硬件同事把Norflash芯片引脚飞线出来,然后抓取波形解码。(示波器也可以)通过对波形的解码去分析判断程序是否正常运行。

DEBUG

Norflash存储芯片在嵌入式系统属于非常重要的单元,所以debug的过程往往只是参数的修改,俗称调参侠。做得最多的事情就是通过逻辑分析仪抓出波形,然后查看指令是否正确,或者查看CLK时钟波形是否异常。

Flashloader

Flash Loader实际上是运行在芯片RAM的一个Flash操作代码。第一,通过J-LINK工具将Flash Loader这段代码下载到RAM。第二,Flash Loader将bin文件下载到FLASH上面。

通俗理解:可以把flashloader理解为能在RAM跑的一个最小系统。它不仅拥有norflash的驱动,同时最基本的cache、pmu电源系统,timer时钟系统也必须有。

这个项目本质是理解能在SRAM上运行的最小系统的代码,并且把这段代码抽出,移植上相应的norflash API接口,最后指定J-LINK烧录的Norflash地址。最后DEBUG而完成这段算法。

这份任务非常考验工程师对整个代码框架的理解,对小白来说属于超纲题,幸亏有资深的系统工程师帮忙,我才得以完成这个任务

第三方库代码移植

对于芯片公司而言,第三库即其他公司的功能集成是非常常见的一件事情。因为芯片公司往往只着力于本身芯片的功耗和算力性能,对上层建筑的诸如算法,协议栈等是简单粗暴地直接移植。在实际工程使用中,我一共完成了两份移植项目:

1.NFC移植

2.支付宝SDK移植

两个移植的目标虽然不同,但是对于驱动工程师而言,本质上都是一样的。无论NFC的协议栈,或是支付宝Alipay_SDK,都必须提供相应的实现库,同时提供给上层调用的API接口。移植步骤总结如下:

1.把相应库文件编译入主控芯片的代码库。(这里需要学会使用makefile管理一个带多个子目录的文件夹,学会添加头文件路径等)

2.根据要求,适配I2C或SPI等驱动,最后实现硬件模块间通信。

3.根据厂商提供的测试框架,完善上层API接口

4.DEBUG。

结:这两个任务看似难,其实简单得一批,因为我们作为买方,卖方会提供大量的支持协助你完成。

FAE协同联调

我所在的分公司主要职能是面对客户,也就是俗称FAE。这块工作其实是相当无聊的,做得最多的东西便是:1.确认清楚客户的问题和需求。2.在公司平台上复现客户问题。3.能自己解决的就解决,不能的就上报给北京研发。

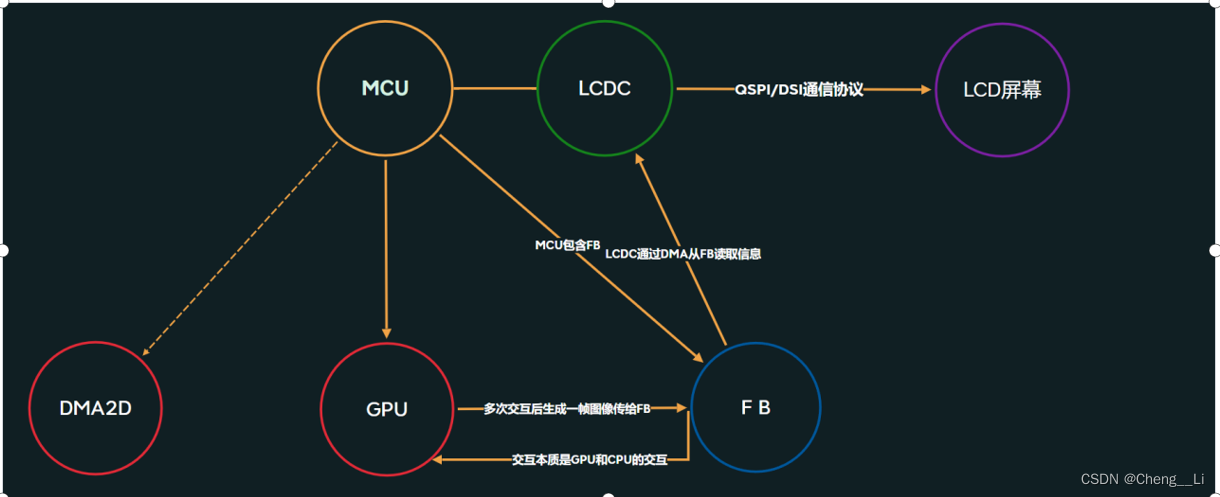

最典型的一次是VIVO出差,调试GPU驱动相关内容。对于个人提升最大的是对整个显示流程的理解。因为其涉及到多个硬件或者逻辑概念之间的交互。把多个逻辑概念之间的关系梳理清楚,是驱动工程师最重要的技能,也是避免成为只会调用API接口的调参侠的进阶之路。

以下为整个流程的框架图:

1.MCU从内存中获取多边形信息并分类整理后,传送给GPU进行处理,两者进行多次交互后,GPU最终生成了完整的图像信息。这些图像信息将被存储在FB(即显存中)

2.LCDC通过DMA通道从FB(显存)中获取图像信息,最后通过MIPI DSI协议传输信息到LCD屏幕中显示。

结:FAE工作对细节的要求不高,遇到任何涉及到细节的问题,都会上报给核心研发去处理,能学到的东西就是对笼统的系统框架的认知。本质上来说,就是很难精通。

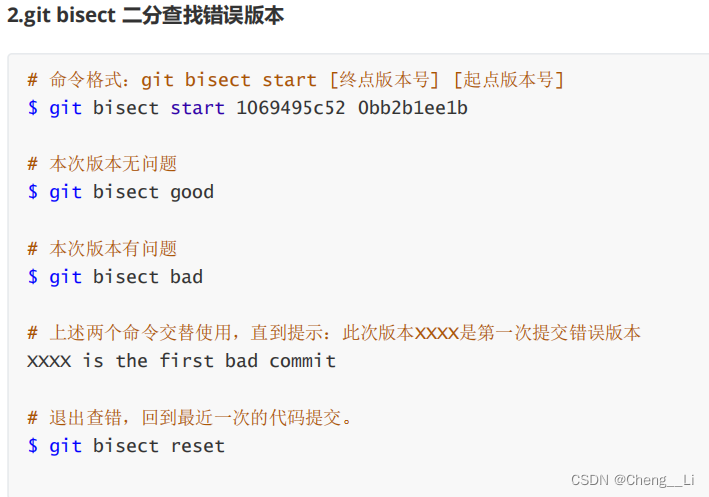

GIT工具

工具在工作中是非常重要的,因为大部分时候,我们都是操作黑箱的工具使用员,我们可以不理会底层的实现细节是什么,但是我们必须非常熟练地使用这些工具。而熟练程度往往与工程师的资深程度相挂钩。

拉取代码:git clone

更新代码:git pull

提交代码三板斧:git add "" ; git commit -m "" ; git push origin <local>:<remote>

查看修改:git diff

查看状态:git status

查看当前分支:git branch

查看修改记录:git log

查看远程仓库分支:git remote -w

回退代码:git reset

合入某个提交到本地验证:git cherry-pick <commit id>

保存修改:git stash save "" ;git stash list; git stash apply <>

生成patch:git diff > XX.patch

应用patch:git apply XX.patch

虽然我并不清楚GIT的底层算法是什么,但是我对这些工具的运用算是炉火纯青了。

总体感受

对于一个新人小白而言,这样的锻炼是全方位的。尽管FAE在技术层面的天花板相对较低,但是FAE+研发这种培养模式对于一个初出茅庐的新人来说,是非常宝贵的经验。

所以最终总结出来的我所认知到的嵌入式系统框架:

一个主核MCU,内置SRAM,FLASH,PSRAM,EMMC等储存器系统存储相应的电源,时钟树,数据,文件系统等。同时MCU上面实现好I2C,SPI,UART,JTAG,MIPI-DSI,I2S等通信协议连接基本的外设。借助以上底层平台,再搭建效率更高的操作系统管理内存和外设,发挥出芯片本身的性能,以此平台实现基础的协议栈,算法,APP应用等。

于此同时,为了提高系统的性能,采用Xilinx开源的OpenAMP系统构建大小核异构系统,变成常用的单主核,多次核模式。主核提供基础的算力,同时将各种算法诸如心率,传感器等集中到一个次核,做各种加速处理。买来的协议栈如蓝牙,wifi也可以集中放到一个次核,做各种适应性处理。

这样一个嵌入式系统的底层软件就构筑完毕了,再在这个平台上面搭建相应的应用层如UI框架等,便能最终完成一个嵌入式产品。

2704

2704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?