1 NAND闪存基本概念

NAND SSD由几个主要组件组成:NAND闪存,SSD控制器,连接器,DRAM,PCB和无源器件,nand SSD的存储单元被封装以形成阵列的形式以优化硅面积占用。根据矩阵中单元的组织方式,可以区分 NAND 和 NOR 闪存,本文主要介绍NAND闪存。

在 NAND 串中,单元串联连接,以 32 或 64 个为一组,如下图所示。两个选择晶体管放置在串的边缘,以确保与源极线(通过

M

S

L

M_{SL}

MSL )和位线(通过

M

D

L

M_{DL}

MDL )的连接。每个 NAND 串与另一个串共享位线接触。控制门通过字线 (WLs) 连接。

逻辑页由属于同一wordline的单元组成。每条wordline的页数与存储单元的存储能力有关。根据存储级别的数量,闪存以不同的方式称为:SLC 存储器每个cell存储 1 bit,MLC 存储器每个cell存储 2 bit,TLC存储器每个cell存储 3 bit和 QLC 存储器每个cell存储 4 bit。偶数和奇数单元形成两个不同的页面。

共享同一组wordline的所有 NAND 串被一起擦除,从而形成一个 Flash 块。在上图中显示了两个块:使用总线表示,一个块由 WL 0<63:0> 组成,而另一个块包括 WL1<63:0>。

2 四种主流的闪存芯片

闪存存储设备是以闪存芯片为存储介质的新型存储设备,闪存的存储单元是 Cell,闪存存储器是由一串串 Cell 组成。如图 1.1 展示,一个 Cell 类似于带有一个控制门(Control Gate)与一个浮置栅极(Floating Gate)的 MOS 晶体管。闪存存储器就是通过改变 Cell 上的电压来表示状态。依据单个 Cell 上表示的比特数可以分为多种类型,目前主流的芯片有 Single Level Cell(简称 SLC)、Multiple Level Cell(简称MLC)、Trinary Level Cell(简称 TLC)与 Quad Level Cell(简称 QLC),其单个存储单元(cell)可以分别存储 1 至 4 个比特数据。

性能对比图如下图所示(3b/c NAND是TCL、4b/c NAND是QCL):

3 NAND SSD的逻辑组件

NAND 存储器包含以特定方式组织的信息。如下图所NAND 存储器存分为页和块。块是最小的可擦除单位。每个块包含多个页面,块内的页数通常是 16 的倍数(例如 64、128)。页是读写的最小可寻址单元。每页由主区和备用区组成。主要区域的范围可以从 4 到 8 kB 甚至 16 kB。备用区可用于 ECC和系统指针,每 4 kB 主区有几百个字节的备用区。如下图所示,假设一个spare area是128bit,main area是4KB,一个NAND存储器种块和页的组成如下图所示:

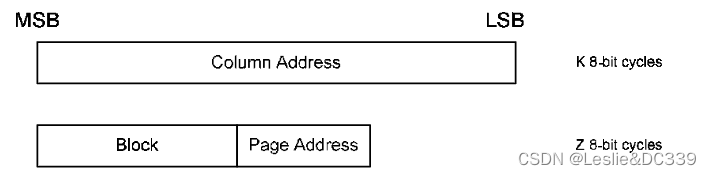

每次我们想要在 NAND 设备上执行操作时,我们都必须发出我们想要执行的地址。地址分为行地址和列地址。行地址标识被寻址的页,而列地址用于标识页内的字节。

- 行地址标识操作中涉及的块和页。页地址占据最低有效位。

- 列地址也是8位

7749

7749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?