目录

1. 概要

本文基于一个实际设计项目的综合作业进行整理总结,以期对将来的FPGA开发能够有所帮助。并作为今后进一步总结提高的基础,方便设计经验的累进式提高(incremental improvement)。

2. 综合结果摘要

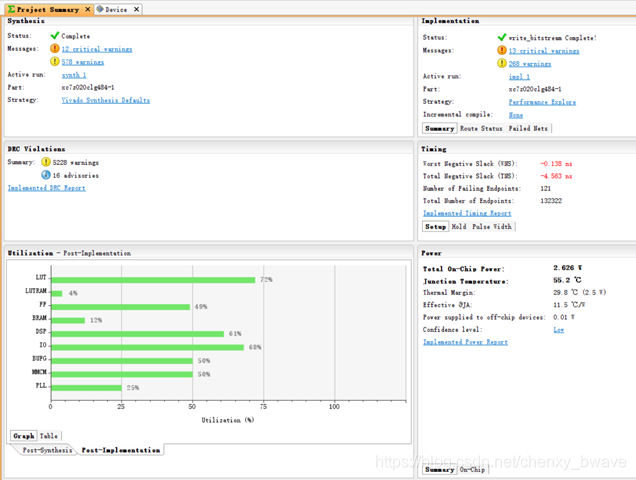

Vivado综合(注意,在本文中“综合”是指整个流程即SynthesisàImplementationàWrite bitstream,当用Synthesis这个词时则表示其中特定的Synthesis这个环节)结束后会出现以下一个汇总摘要就结果。如下图所示。

在每一个子窗口中都有相关的链接可以点进去进一步查看更详细的情况。

图 1 Project summary after the complete of the whole flow

3. Resource Utilization

硬件资源利用状况。

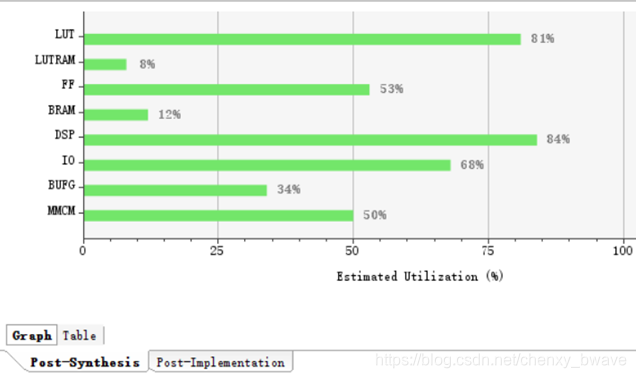

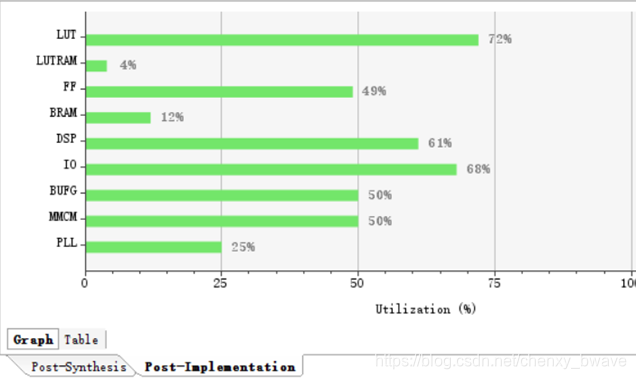

其中分两栏,一个是“Post-Synthesis”,另一个是“Post-Implementation”。分别点开这两栏可以看到两者的信息略有不同。

首先,“PLL”这一项在Post-Implementation中才报出来。这是因为PLL是采用Xilinx内置IP,不需要进行Synthesis。

从以下两图可以看出,大部分硬件资源(LUT、LUTRAM、FF、DSP)利用率从“Post-Synthesis”到“Post-Implementation”都有所下降。其余的如IO、MMCM(Mixed-Mode Clock Manager)则保持不变。还有BUFG则增加了。

LUT、LUTRAM、FF、DSP等资源利用率下降说明Vivado综合工具在Implementation还会对资源使用进行进一步的优化。在作者另一个设计的综合中,“Post-Synthesis”后DSP利用率跑到118%,但是“Post-Implementation”后就缩减到了90%。

图 2 Post-Synthesis utilization summary

图 3 Post-Implementation utilization summary

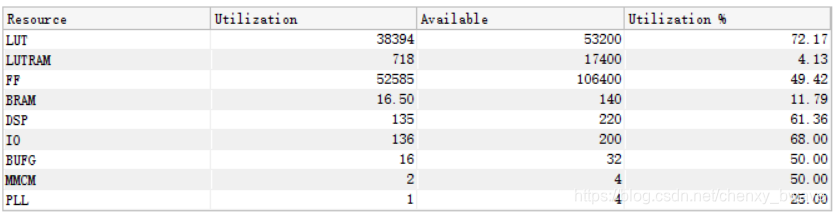

从以上图中可以看到Graph旁边还有一个Table tab,点开Table可以看到以表格形式呈现的资源利用率,如下图所示。Table的优点在于可以看到更加明确的数量关系。

图 4 Post-Implementation utilization summary in table form

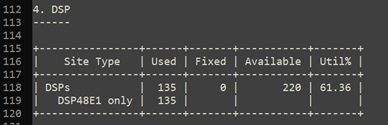

3.1 DSP利用率

在通信信号处理领域,由于通常要使用大量的乘法器,而在FPGA实现中乘法器是用内置的DSP模块来实现。所以通常通信信号处理的FPGA实现中,DSP资源利用率是一个非常重要的因子。

从以上信息来看,可以看出本综合中最终DSP的利用率为61%(135 out of 220),但是从这个summary中没有更具体的哪个模块使用了多少DSP的信息。这个信息应该到哪儿去找呢?就笔者所知,在“impl\system_top_utilization_placed.rpt”和“synth\system_top_utilization_placed.rpt”中也有资源使用量的信息,但是遗憾的是这两个文件中依然只是summary信息,并没有比以上几个图提供更多的信息。如下图所示。

图 5 DSP Utilization in “system_top_utilization_placed.rpt”

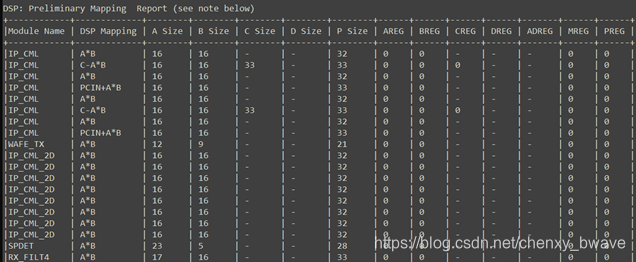

还有一个能提供更详细一些的信息的log是synth目录的runme.log。打开这个文件搜索“DSP Mapping”可以看到如下图所示的信息:

图 6 DSP Mapping information in synth\runme.log

从图中可以看出各个模块中所映射的DSP模块的相关信息。但是这个总结信息还是有一定的不足(没有反映完整的信息)。

![]()

如以上信息所述,这里只是综合阶段的一个初步映射,(如前文所述)在Implementation阶段有些DSP会改用其它逻辑资源实现。另外,有些模块如果有多个实例化对象的话,只会汇报其中一个实例化的DSP映射结果(这条信息其实有些含糊难解。。。),所以以上所列出的DSP的个数与summary中的结果其实并不一致。所有要想得到更为完整精确的DSP映射信息还需要进一步的分析手段。另外,还需要针对impl\runme.log进一步分析以确认在Implementation环节又哪些在synthesis环节映射的DSP模块最终被替换为别的逻辑资源了。

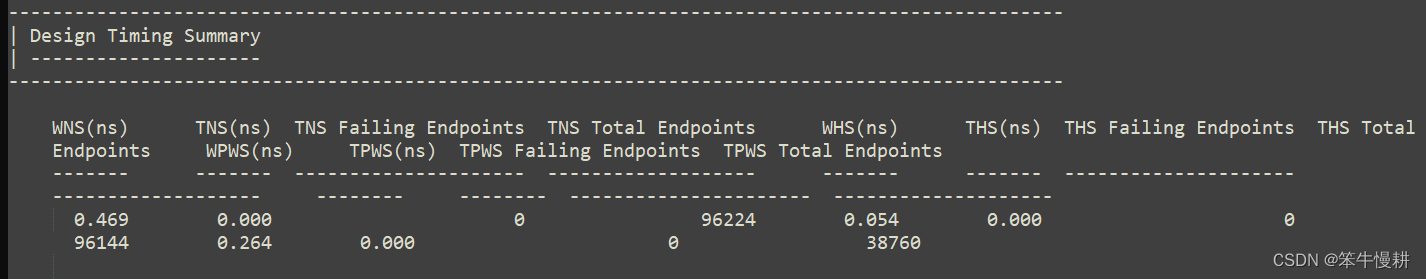

4. Timing

在上面的综合结果摘要图中有一个关于最终时序是否能过的信息,从图形界面也可以打开看到具体的时序信息。另一方面,也可以打开文本文件查看详细的综合timing方面的信息。综合时序信息保存在文件“***_timing_summary_routed.rpt”中,打开后可以看到一个summary部分:

这里没有出现复制就表明综合时序全部满足,如果有负数出现就需要确认具体出问题的路径是什么情况,并据此采取优化措施。

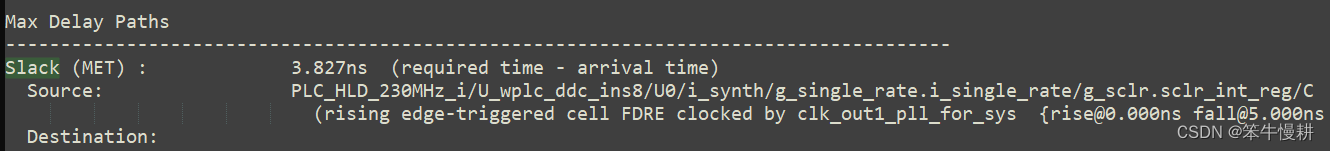

用关键slack搜索该文本可以得到关键路径的详细时序信息(具体报多少条路径的信息,以及是只报有问题的路径的信息还有也报满足时序的路径的信息取决于综合选项,这里暂时跳过),比如说可能会看到以下这样的信息:

这里Slack后面的() 里是MET(meet的过去分词)表示该条路径的timing约束得到满足,没有问题。如果是(Violated)的话,那么其后的值就应该是负数,表明该条路经的timing约束没有得到满足,需要采取对策。

(未完待续)

5685

5685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?