1. SoC时钟系统

什么是时钟?SoC为什么需要时钟?

(1)时钟是同步工作系统的同步节拍

(2)SoC内部有很多器件,譬如CPU、串口、DRAM控制器、GPIO等内部外设,这些东西要彼此协同工作,需要一个同步的时钟系统来指挥。这个就是我们SoC的时钟系统。

1.1 时钟一般如何获得

SoC的时钟获得一般有:

- 外部直接输入时钟信号,SoC有个引脚用来输入外部时钟信号,用的很少。

- 外部晶振+内部时钟发生器产生时钟,大部分低频单片机都是这么工作的。

- 外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频得到各种频率的时钟,210属于这种。

S5PV210属于第三种。为什么这么设计?

第一问:外什么不用外部高频晶振产生高频信号直接给CPU?

主要是因为芯片外部电路不适宜使用高频率,因为传导辐射比较难控制;高频率的晶振太贵了。

第二问:为什么要内部先高频然后再分频?

主要因为SoC内部有很多部件都需要时钟,而且各自需要的时钟频率不同,没法统一供应。因此设计思路是PLL后先得到一个最高的频率(1GHz、1.2GHz),然后各外设都有自己的分频器再来分频得到自己想要的频率。

1.2 时钟和系统性能的关系、超频、稳定性

- 一般SoC时钟频率都是可以人为编程控制的,频率的高低对系统性能有很大影响。

- S5PV210建议工作频率800MHz~1.2GHz,一般我们都设置到1GHz主频。如果你设置到1.2GHz就叫超频。超频的时候系统性能会提升,但是发热也会增大,因此会影响系统稳定性。

- 每个外设工作都需要一定频率的时钟,这些时钟都是由时钟系统提供的。时钟系统可以编程控制工作模式,因此我们程序员可以为每个外设指定时钟来源、时钟分频系统、从而制定这个外设的工作时钟。

- SoC中各种设备工作时,时钟频率越高其功耗越大,发热越大,越容易不稳定,需要外部的散热条件越苛刻。

- SoC内部有很多外设,这些外设不用的时候最好关掉(不关掉会一定程度浪费电),开关外设不是通过开关,而是通过时钟。也就是说我们给某个外设断掉时钟,这个外设就不工作了。

2. S5PV210的时钟系统简介

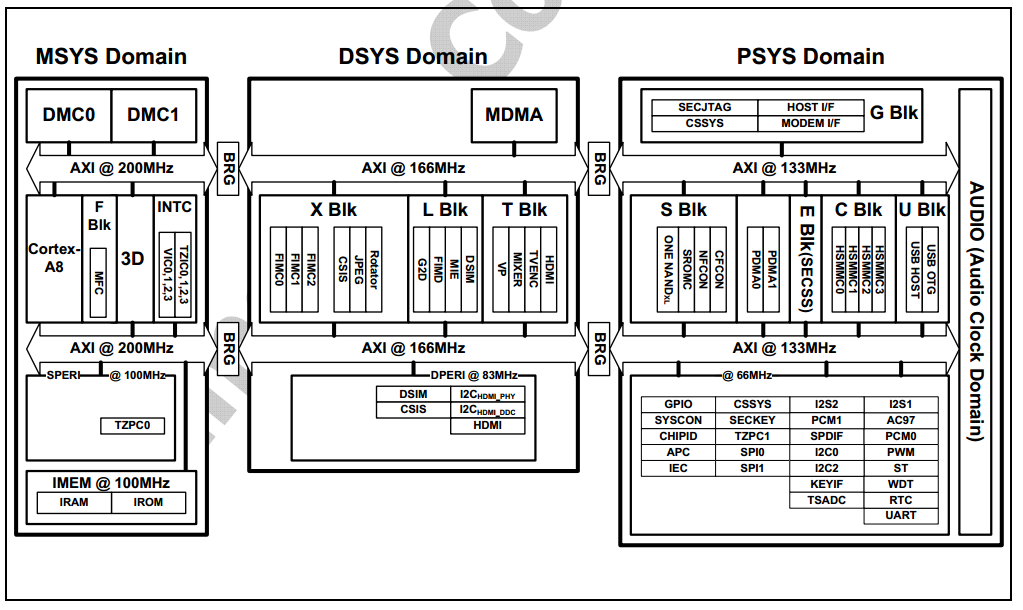

2.1 s5pv210的时钟域

- MSYS:(main system)主时钟域,包括CPU,DDR内存条,IROM和IRAM等

- DSYS:(display system)显示时钟域,就是一般的和视频有关的就在这个时钟域中,如HDMI,TVENC等

- PSYS:(peripheral system)外围时钟域,就是GPIO接口,I2C接口,UART接口等这些外围设备就在这个时钟域上。

注释:每个时钟域通过一条BRG(异步总线的桥梁)连接在一起。

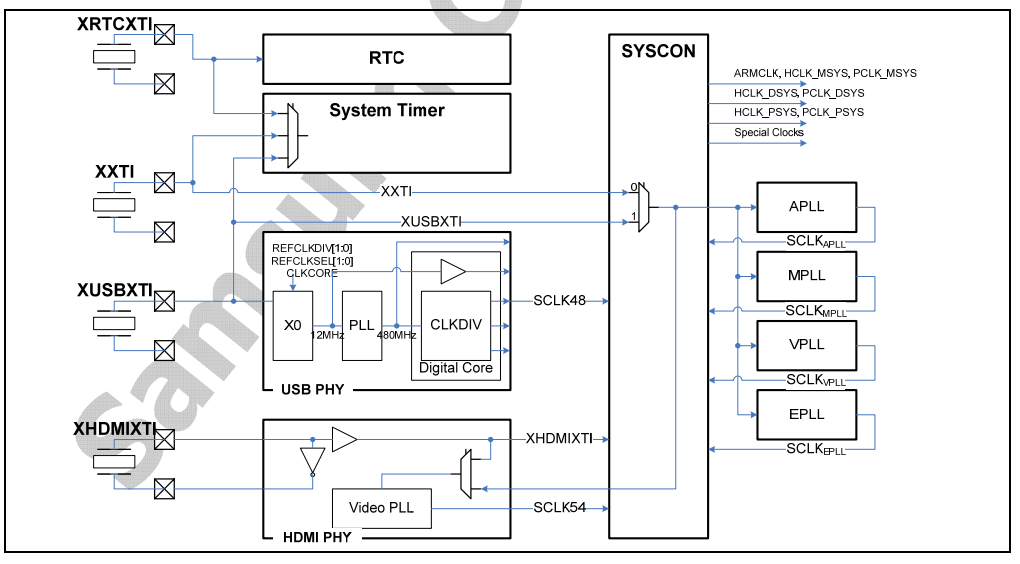

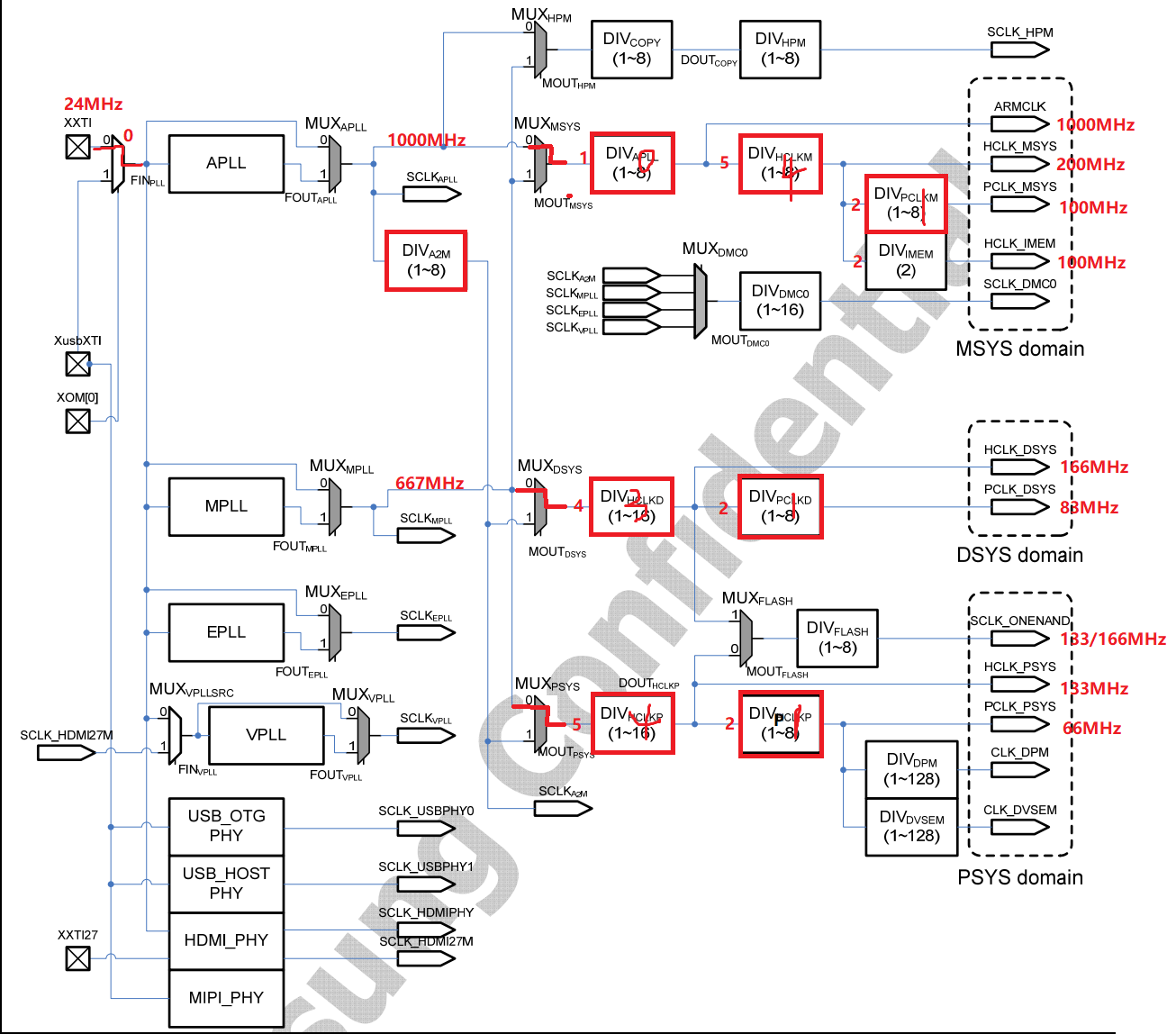

2.2 时钟来源:晶振+时钟发生器+PLL+分频电路

S5PV210外部有4个晶振接口,设计板子硬件时可以根据需要来决定在哪里接晶振。接了晶振之后上电相应的模块就能产生振荡,产生原始时钟。原始时钟再经过一系列的筛选开关进入相应的PLL电路生成倍频后的高频时钟。高频时钟再经过分频到达芯片内部各模块上。(有些模块,譬如串口内部还有进一步的分频器进行再次分频使用)

从上图可知:

s5pv210有4个晶振时钟:

- XRTCXTI:提供32.768KHz,RTC 使用;XRTCXTI and XRTCXTO pins

- XXTI:CMU and PLL使用这个时钟为APLL、MPLL、VPLL、EPLL提供时钟。推荐频率24MHz。XXTI and XXTO pins

- XUSBXTI:为APLL、MPLL、VPLL、EPLL、USB PHY提供时钟,推荐24MHz。XUSBXTI and XUSBXTO pins.

- XHDMIXTI :27MHz,VPLL、HDMI PHY为TV提供54MHz时钟。XHDMIXTI and XHDMIXTO pins

我们的210芯片,一般是从XXTI这个接口进入,这个接口连接外部晶振(规定是24MHz),然后进入内部时钟发生器(syscon),再分别进入4个PLL,分别产生4种不同的高频时钟,各个高频时钟再经过内部的分频器分频得到各种频率的时钟。

- APLL uses FINPLL (refer to Figure 3-1) as input to generate 30MHz ~ 1GHz.

- MPLL uses FINPLL as input to generate 50MHz ~ 2GHz.

- EPLL uses FINPLL as input to generate 10MHz ~ 600MHz.

- VPLL uses FINPLL or SCLK_HDMI27M as input to generate 10MHz ~ 600MHz. This PLL generates 54MHz video clock.

- USB OTG PHY uses XUSBXTI to generate 30MHz and 48MHz

- HDMI PHY uses XUSBXTI or XHDMIXTI to generate 54MHz

2.3 时钟关系

MSYS clock domain

- freq(ARMCLK) = freq(MOUT_MSYS) / n, where n = 1 ~ 8

- freq(HCLK_MSYS) = freq(ARMCLK) / n, where n = 1 ~ 8

- freq(PCLK_MSYS) = freq(HCLK_MSYS) / n, where n = 1 ~ 8

- freq(HCLK_IMEM) = freq(HCLK_MSYS) / 2

DSYS clock domain

- freq(HCLK_DSYS) = freq(MOUT_DSYS) / n, where n = 1 ~ 16

- freq(PCLK_DSYS) = freq(HCLK_DSYS) / n, where n = 1 ~ 8

PSYS clock domain

- freq(HCLK_PSYS) = freq(MOUT_PSYS) / n, where n = 1 ~ 16

- freq(PCLK_PSYS) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

- freq(SCLK_ONENAND) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

s5pv210推荐时钟设置:

- freq(ARMCLK) = 1000 MHz

- freq(HCLK_MSYS) = 200 MHz

- freq(HCLK_IMEM) = 100 MHz

- freq(PCLK_MSYS) = 100 MHz

- freq(HCLK_DSYS) = 166 MHz

- freq(PCLK_DSYS) = 83 MHz

- freq(HCLK_PSYS) = 133 MHz

- freq(PCLK_PSYS) = 66 MHz

- freq(SCLK_ONENAND) = 133 MHz, 166 MHz

HCLK_DSYS:DSYS时钟域的高频率线;

PCLK_DSYS:DSYS时钟域的低频率线;其他的依次类推

2.4 时钟配置过程

遵循的原则:

- 所有的防干扰mux必须有输入

- 当PLL断电时,不能使用输出

SFR配置步骤:

//1.打开PLL

(A,M,E,V)PLL_CON[31] = 1; // Power on a PLL (Refer to (A, M, E, V) PLL_CON SFR)

wait_lock_time; // Wait until the PLL is locked

(A, M, E, V)PLL_SEL = 1; // Select the PLL output clock instead of input reference clock, after PLL output clock is stabilized. (Refer to 0, 4, 8, 12th bit of CLK_SRC0 SFR)

当PLL打开之后,就不要关闭了。

设置PLL’s PMS的值

Set PMS values; // Set PDIV, MDIV, and SDIV values (Refer to (A, M, E, V) PLL_CON SFR)

设置系统时钟分频器值

CLK_DIV0 [31:0] = target value0;

设置特殊时钟的分频器值

CLK_DIV1 [31:0] = target value1;

CLK_DIV2 [31:0] = target value2;

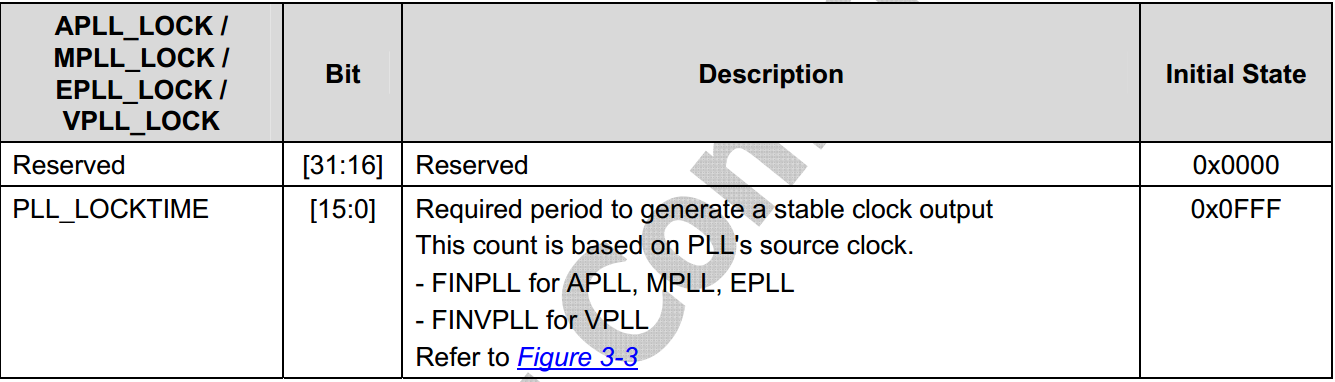

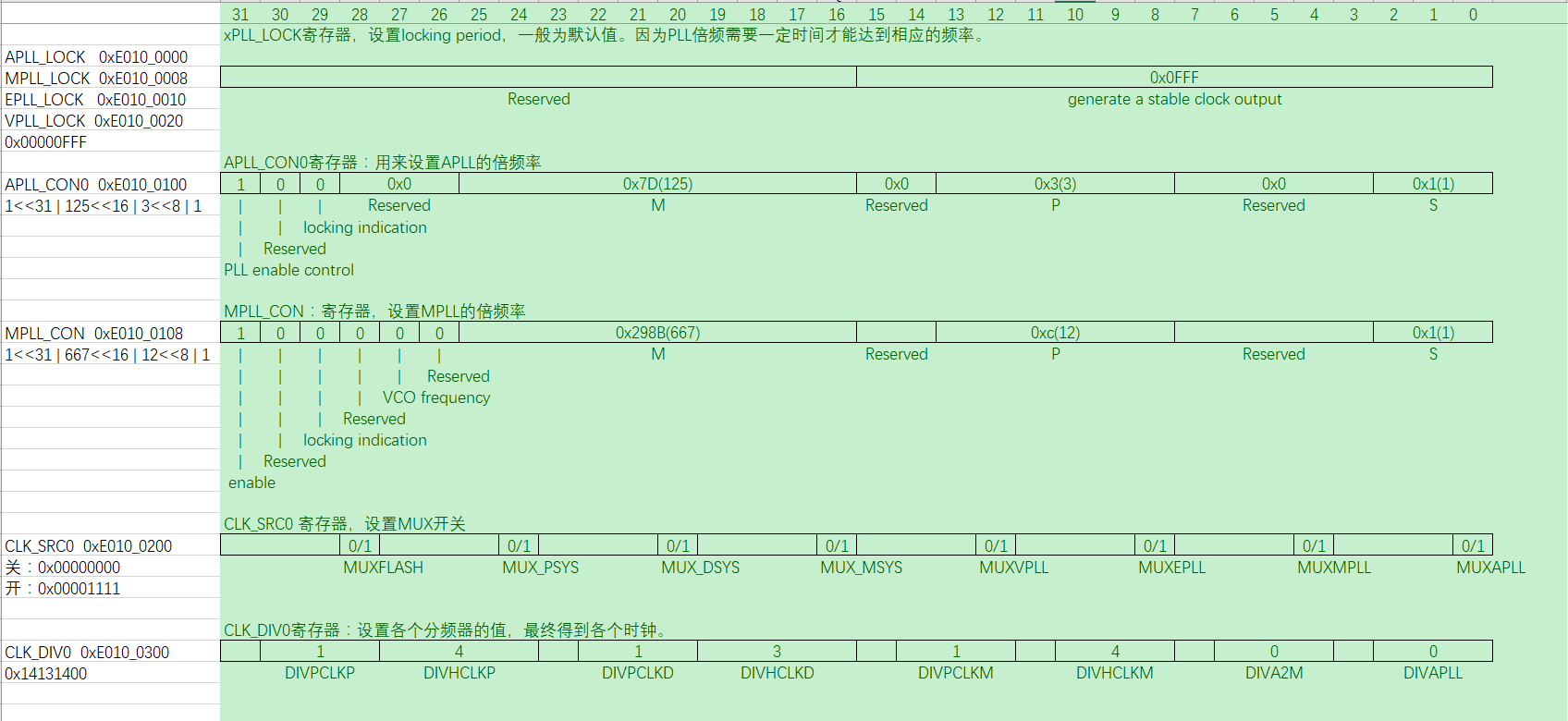

3. 相关寄存器

从2.4我们可以知道我们需要设置的寄存器:

1、xPLL_LOCK寄存器,设置locking period,一般为默认值。因为PLL倍频需要一定时间才能达到相应的频率。

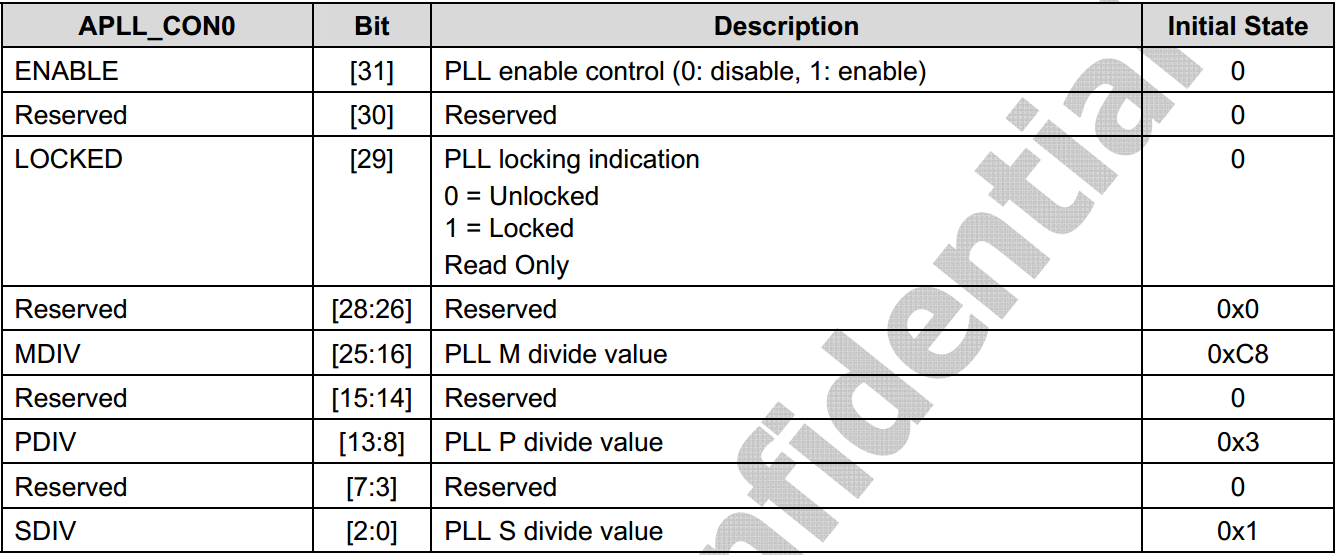

2、APLL_CON0寄存器:用来设置APLL的倍频率。

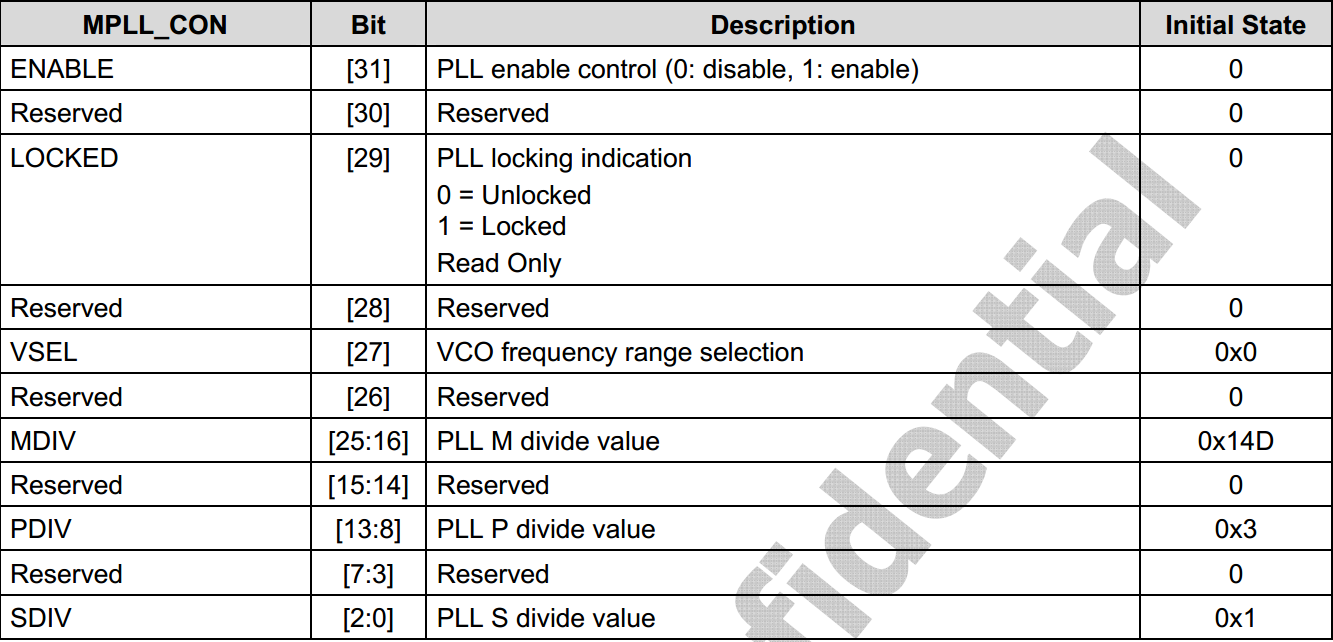

3、MPLL_CON寄存器,设置MPLL的倍频率

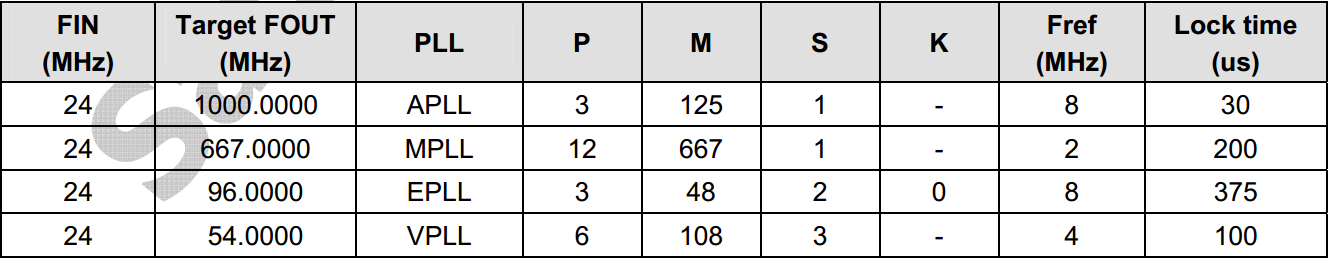

参考P、M、S值:

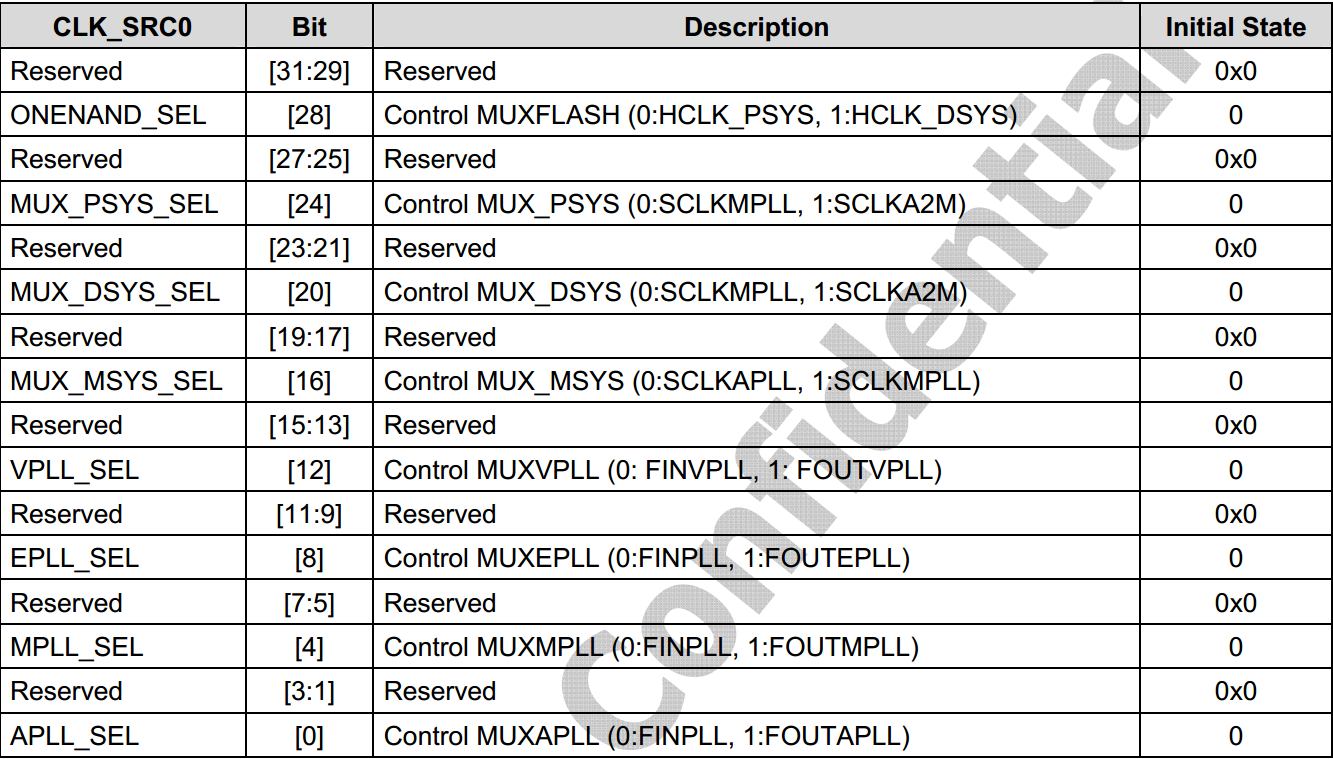

4、CLK_SRC0 寄存器,设置MUX开关 设置各时钟前首先要关闭4个PLL的MUX开关,设置好相应寄存器以后在把PLL的MUX开关打开。

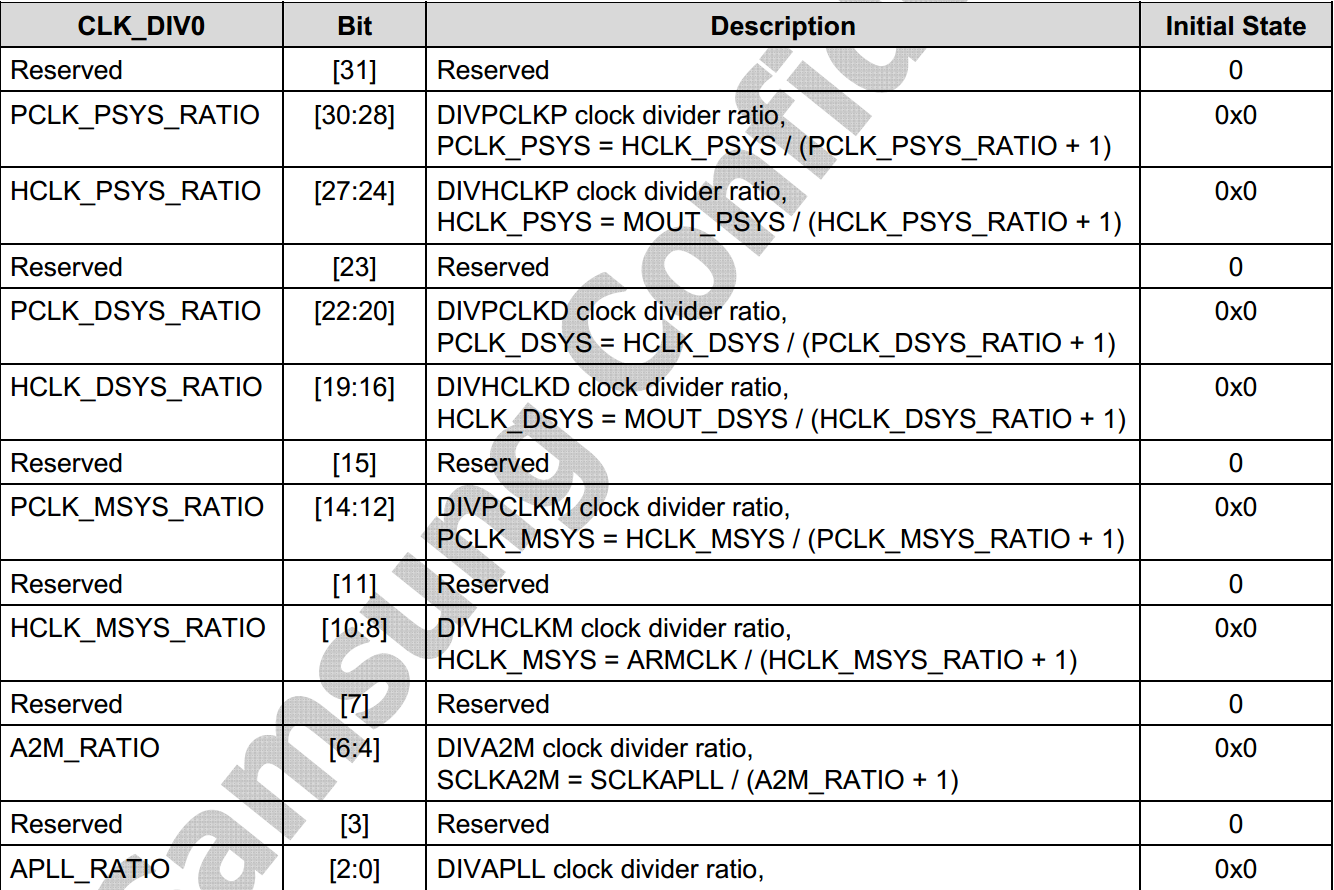

5.CLK_DIV0寄存器:设置各个分频器的值,最终得到各个时钟。

各寄存器配置值为:

4. 分频框图

根据推荐值来设置相应的MUX开关、PLL锁相环倍频、DIV分频器的值来得到相应的时钟。

这里,DIVIMEM值固定为2,不需要通过寄存器设置。

Divider for internal memory shown as DIVIMEM in Figure 3-3 does not have corresponding fields in clock divider control registers since the divider value is fixed to two.

详细代码参见GitHub: https://github.com/zhutianyang/Arm_embedded_learning/tree/master/6.clock_init

2971

2971

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?