快要毕业了,毕业之前再重新把这些实验从头到尾的练习一遍,先开始裸机的吧,这些都是以前搞过的东西,现在应该会比较快。。

开始吧!

时钟对于电子设备来说都是非常重要的,它是传输数据的一个基准,如果没有这个基准的话将导致系统的混乱。

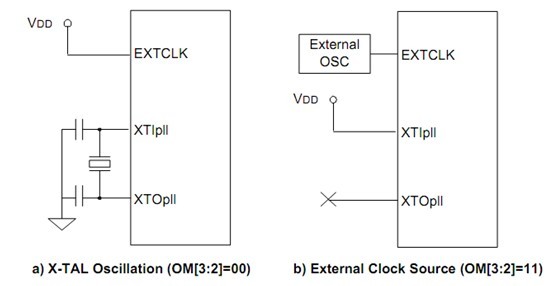

S3C2440的频率有两种输入方式:外部时钟源和内部晶振(如下图)

输入的频率一般是比较低的比如2440的就只有12M,而2440的主频可以达到460M,这就需要对输入频率通过PLL锁相环进行倍频

先来看下这个CLOCK的结果图:

从上面的结果图可以看出输入频率OSC首先经过MPLL倍频

整个系统时钟主要有几个组成:FCLK,HCLK,PCLK

FCLK:是个cpu提供时钟

HCLK:用于AHB总线,中断控制器,LCD控制器,内存控制器提供时钟

PCLK:用于APB总线,通常给IIC,WDT,IIS,ADC, UART, GPIO, RTC and SPI.等外设提供时钟

下面是整个时钟系统的几种工作方式:正常,空闲,慢,睡眠模式。

慢模式:也就是没有通过MPLL倍频,直接就由外部时钟源或者内部晶振来提供时钟,所以系统的功耗有时钟源来决定

设置系统时钟主要配置几个寄存器:

MPLLCON:设置P,S,M的值

CLKDIVN:设置FCLK,HCLK,PCLK的比例关系

MPLL和UPLL的计算公式不同:

Mpll = (2*m * Fin) / (p * 2s)

m = M (the value for divider M)+ 8, p = P (the value for divider P) + 2,s = SDIV

UPLL Control Register

Upll = (m * Fin) / (p * 2S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

另外需要特别注意的一点,如果直接采用上面的式子计算输出频率很可能出错,因为会发生溢出,故采用下面的式子:

FOUT = 2 * m * (Fin/100) / (p*2S)×100,

下面是核心代码:

//为了使FCLK=400Mhz,我们取m=92,p=1,s=1.也可以根据手册p255频率表中的数值, //但是没有400Mhz的组合。可以选接近的

rMPLLCON = 92<<12 | 1<<4 |1 ;

rCLKDIVN = 2<<1 | 1; //FCLK:HCLK:PCLK = 1:4:8

rCAMDIVN = 0<<9 ; //配置CLKDIVN[2:1]与改位有关,可参考手册说明

m = (rMPLLCON>>12) &0xff ;

p = (rMPLLCON>>4) & 0x3f;

s = rMPLLCON & 0x3;

FCLK = ((m+8) * 2 * (FIN/100)) / ( (p+2) * (1 << s))*100;

PCLK = FCLK >>3;

备注参考资料:

| CLKDIVN | 位 | 描述 | 初始值 |

| DIV_UPLL | [3] | UCLK选择寄存器(UCLK必须对USB提供48MHz) 0:UCLK=UPLL clock 1:UCLK=UPLL clock/2 | 0 |

| HDIVN | [2:1] | 00:HCLK = FCLK/1 01:HCLK = FCLK/2 10:HCLK = FCLK/4,当CAMIVN[9]=0 HCLK = FCLK/8,当CAMIVN[9]=1 11: HCLK = FCLK/3,当CAMIVN[8]=0 HCLK = FCLK/6,当CAMIVN[8]=1 | 0 |

| PDIVN | [0] | 0:PCLK是和HCLK/1相同时钟 1:PCLK是和HCLK/2相同时钟 | 0 |

| CAMDIVN | 位 | 描述 | 初始值 |

| … | … | … | … |

| HCLK4_HALF | [9] | HDIVN分频因子选择位(当CLKIVN[2:1]位为10b时有效) 0: HCLK=FCLK/4 1: HCLK=FCLK/8 | 0 |

| HCLK3_HALF | [8] | HDIVN分频因子选择位(当CLKIVN[2:1]位为11b时有效) 0: HCLK=FCLK/3 1: HCLK=FCLK/6 | 0 |

| … | … | … | … |

参考文献:出处:http://blog.csdn.net/charistain_huang

另外关于S3C2440的时钟的理解可参考: http://blog.csdn.net/mr_raptor/article/details/6555734

本文介绍了S3C2440微处理器的时钟系统,包括时钟的重要性和工作模式。外部时钟源或内部晶振通过PLL倍频提升频率,系统时钟主要分为FCLK、HCLK和PCLK。慢模式下,系统直接使用未经倍频的时钟。配置时钟涉及MPLLCON和CLKDIVN寄存器,以及MPLL和UPLL的计算公式。核心代码段展示了如何设置这些参数。参考了相关博客文章以深入理解S3C2440的时钟配置。

本文介绍了S3C2440微处理器的时钟系统,包括时钟的重要性和工作模式。外部时钟源或内部晶振通过PLL倍频提升频率,系统时钟主要分为FCLK、HCLK和PCLK。慢模式下,系统直接使用未经倍频的时钟。配置时钟涉及MPLLCON和CLKDIVN寄存器,以及MPLL和UPLL的计算公式。核心代码段展示了如何设置这些参数。参考了相关博客文章以深入理解S3C2440的时钟配置。

1865

1865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?