目标

PCI,即外围组件互联Peripheral Component Interconnect。

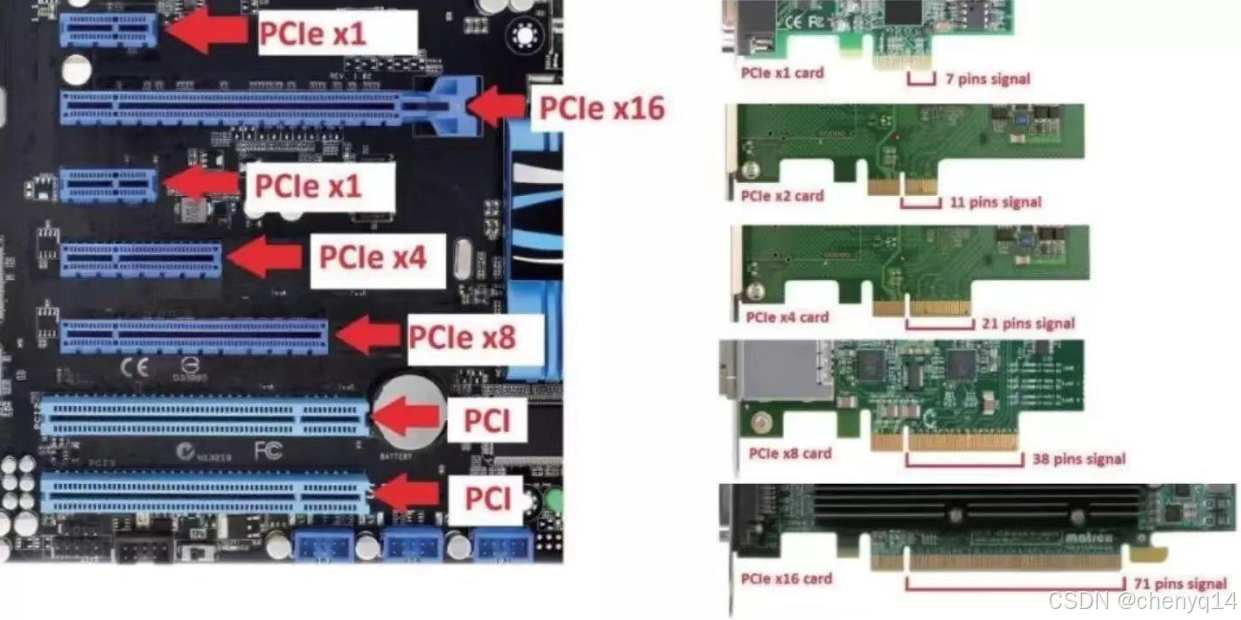

PCIe是PCI的升级,即PCI Express,其最高速度比PCI(133MB/s)有了极大提高(10GB/s)。

有x2,x4,x8,x12,x16,x32通道的7种规格。

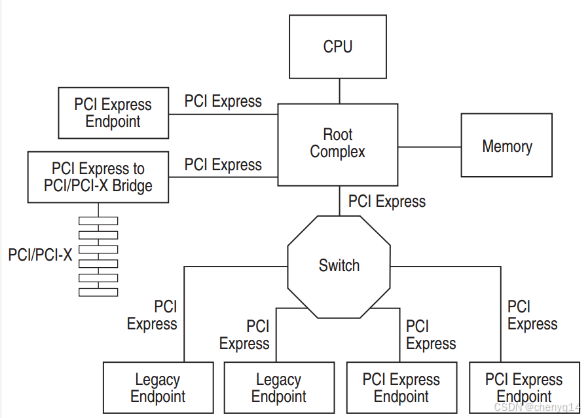

涉及PCIE的3种角色

- Root Complex,简称RC,根节点,接入CPU。

- Switch,简称SW,用于拓展PCIE接口,类似HUB作用。

- Endpoint,简称EP,终端设备

目的

现在有2块RK3588的设备,PCIE接口互相连接在一起,要求他们使用PCIE进行通讯,这意味着其中一块是RC,如果电脑一样,承担HOST角色;另外一块是EP,类似一种能接入电脑PCIE卡槽的外设。

RK3588芯片关于PCIe的介绍

RK3588共有5个PCIe的控制器,硬件IP是一样的,配置不一样,其中一个4Lane DM模式可以支持作为 EP使用,另外一个2Lane和3个1Lane控制器均只能作为RC使用。

RK3588有两种PCIe PHY,其中一种为pcie3.0PHY,含2个Port共4个Lane,另一种是pcie2.0的PHY有3 个,每个都是2.0 1Lane,跟SATA和USB combo使用。 pcie3.0 PHY的4Lane可以根据实际需求拆分使用,拆分后需要合理配置对应的控制器,所有配置在DTS 中完成,无需修改驱动。

使用限制:

- pcie30phy拆分后,pcie30x4控制器,工作于2Lane模式时只能固定配合pcie30phy的port0,工 作于1Lane模式时,只能固定配合pcie30phy的port0lane0;

2. pcie30phy拆分后,pcie30x2控制器,工作于2Lane模式时只能固定配合pcie30phy的port1,工 作于1Lane模式时,只能固定配合pcie30phy的port1lane0;

3. pcie30phy拆分为4个1Lane,pcie3phy的port0lane1只能固定配合pcie2x1l0控制器,pcie3phy 的port1lane1只能固定配合pcie2x1l1控制器;

4. pcie30x4控制器工作于EP模式,可以使用4Lane模式,或者2Lane模式使用pcie30phy的port0, pcie30phy的port1中2lane可以作为RC配合其他控制器使用。默认使用common clock作为 reference clock时,无法实现pcie30phy port0的lane0工作于EP模式,lane1工作于RC模式配合 其他控制器使用,因为Port0的两个lane是共用一个输入的reference clock,RC和EP同时使用 clock可能会有冲突。

5. RK3588 pcie30phy 如果只使用其中一个port,另一个port也需要供电,refclk等其他信号可接地

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4287

4287

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?