最近开始学习xilinx system generator,学习此工具的最终目标是利用它搭建一套用于模板匹配的归一化交叉互相关系统。

通过今天这个小实验,认识数据格式在FPGA中的重要性.

system generator中定义的定点数格式为FIX_16_8,意思是用16比特的数据表示一个数,其中所包含的8比特为小数位,FIX表示有符号数,也就是说FIX_16_8能够表示的数据范围为-128~128。如果超过这一范围,表示存在溢出,需要进行“wrap”或者“saturate”这样的操作保证数据的正确性。

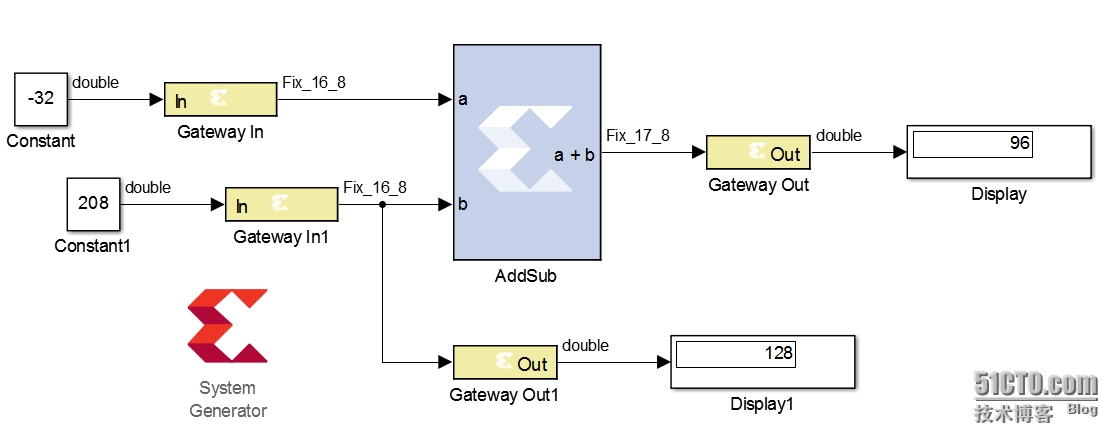

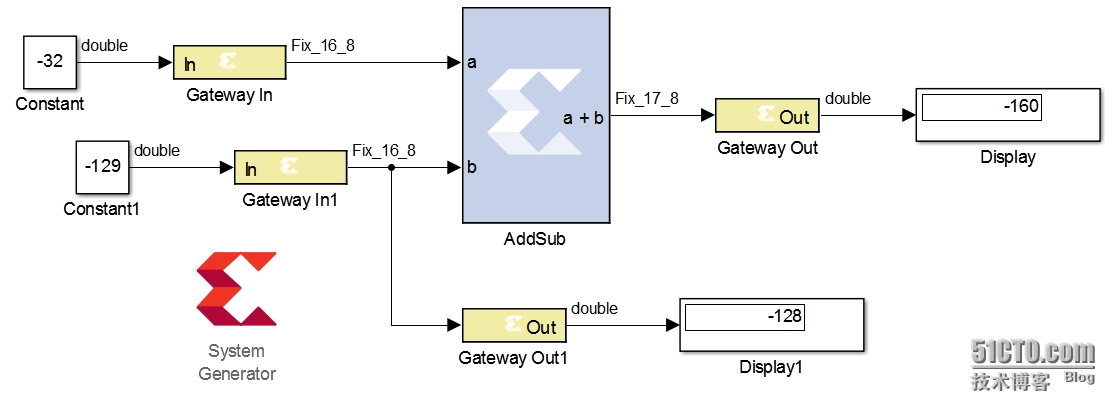

比如,图1中输入两个数:-32和208,数据格式为FIX_16_8,正确结果应该为176,但是该数据超出范围,因此,只显示96。这是因为208经过GATEWAY IN之后,变为128,因此,输出了96。同样的,如果输入-129,经过gateway in就会变成-128,如图2所示。

图1,the first project

图2

1768

1768

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?