问题描述

使用Xilinx System generator搭建了一个波形处理应用,在Equalization均衡处理中使用到乘法、加法和除法IP核,使用后编译出现时序违约数值偏大问题。

问题定位

打开"Implementation"中的"Report Clock Interaction",发现除了跨时钟域"Inter-clock paths"存在时序违约问题外,单个时钟域内部"Intra-clock paths"也存在时序违约问题。

双击相应path,可以看到违约的具体信息Summary,

可以定位到Sytem Generator产生的IP核内部存在组合逻辑时序无法满足的问题。

IP核内部Path

IP核内部该Path出现了乘加运算的组合逻辑时间太长问题,单个时钟周期可能无法得到正确的输出值。

问题解决

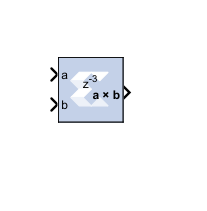

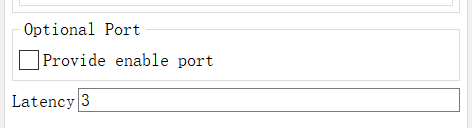

因为使用 System generator产生的IP核工作时钟高达250MHz,不宜将乘法运算的Latency改为0,默认的乘法运算Latency是3个clk:

修改后,重新编译导出并综合布线后,时序违约问题解决:

问题分析结论

本人是System Generator的初学者,虽然接触时间不长,但可以体会到使用该工具,在仿真效率和信号处理开发上带来的巨大提升,也需要该软件生态进一步扩展,实现更多成熟IP核的导入和支持第三方IP核的添加。

解决这个问题有几点体会和大家分享:

1.尽量使用默认的组件参数,避免不必要的问题。本人在初次使用时,为了时钟对齐,将许多组件的Latency均改为了0,导致编译时大量较长的组合逻辑造成时序违约;

2.出现时序违约时,善用Vivado中的Summary,可以便利定位问题;

3.时序违约不外乎两种,一种是我这种组合逻辑问题;一种是跨时钟域的问题,尽量通过FIFO跨时钟域,如果跨时钟域并不影响我们的逻辑,也可以set false path进行忽略。

1523

1523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?