-

(一)设计的功能描述(含所有实现的指令描述及模块的功能)

一、 指令描述 -

R-型指令

(1) add

指令名:加法指令

功能描述:rd ← rs + rt; PC ← NPC (PC + 4)。 32 位整数加法,源操作数分别在 rs, rt 两个通用寄存器中,结果放在 rd 寄存器。由于本设计无溢出检测,因此该指令功能同 addu。

(2) addu

指令名: 无符号数加法指令

功能描述:rd ← rs + rt; PC ← NPC (PC + 4)。 32 位无符号整数加法,源操作数分别在 rs, rt 两个通用寄存器中,结果放在 rd 寄存器。

(3) sub

指令名:减法指令

功能描述:rd ← rs - rt; PC ← NPC (PC + 4)。 32 位整数减法,源操作数分别在 rs, rt 两个通用寄存器中,结果放在 rd 寄存器。

(4) subu

指令名:无符号减法指令

功能描述:rd ← rs - rt; PC ← NPC (PC + 4)。 32 位无符号整数减法,源操作数分别在 rs, rt 两个通用寄存器中,结果放在 rd 寄存器。

(5) and

指令名: 逻辑与

功能描述:rd ← rs and rt; PC ← NPC (PC + 4)。 32 位数按位逻辑与,源操作数分别在 rs, rt 中,结果放在 rd 寄存器。

(6) or

指令名: 逻辑或

功能描述:rd ← rs or rt; PC ← NPC (PC + 4)。 32 位数按位逻辑或,源操作数分别在 rs, rt 中,结果放在 rd 寄存器。

(7) xor

指令名: 逻辑异或

功能描述:rd ← rs xor rt; PC ← NPC (PC + 4)。 32 位数按位逻辑异或,源操作数分别在 rs, rt 中,结果放在 rd 寄存器。

(8) nor

指令名: 逻辑或非

功能描述:rd ← rs nor rt; PC ← NPC (PC + 4)。 32 位数按位逻辑或非,源操作数分别在 rs, rt 中,结果放在 rd 寄存器。

(9) slt

指令名: 小于则设置指令

功能描述: if ((rs)<(rt)) then (rd)←1; else (rd)←0; PC ← NPC (PC + 4)。如果 rs 的值小于 rt 值,则设置 rd 为 1,否则 rd 为 0。

(10) sltu

指令名: 无符号小于则设置指令

功能描述: if ((rs)<(rt)) then (rd)←1; else (rd)←0; PC ← NPC (PC + 4)。无符号数小于判断,如果 rs 的值小于 rt 值,则设置 rd 为 1,否则 rd 为 0。

(11) sll

指令名: 逻辑左移

功能描述: (rd)←(rt)<<shamt; PC ← NPC (PC + 4)。逻辑左移,将 rt 寄存器中的 32 位数逻辑左移后赋给 rd,低位用 0 填充,移位的位数是 shamt。

(12) srl

指令名: 逻辑右移

功能描述: (rd)←(rt)>>shamt; PC ← NPC (PC + 4)。逻辑右移,将 rt 寄存器中的 32 位数逻辑右移后赋给 rd,移位的位数是 shamt。

(13) sra

指令名: 算术右移

功能描述: (rd)←(rt)>>>shamt; PC ← NPC (PC + 4)。算术右移,将 rt 寄存器中的 32 位数算术右移后赋给 rd,移位的位数是 shamt。算术右移时,符号位不仅要参与移位,还要保留。

(14) sllv

指令名: 按寄存器值逻辑左移指令

功能描述: (rd)←(rt)<<(rs); PC ← NPC (PC + 4)。按寄存器值逻辑左移指令,将 rt 寄存器中的 32 位数逻辑左移后赋给 rd,低位用 0 填充,移位的位数在 rs 寄存器中。

(15) srlv

指令名: 按寄存器值逻辑右移指令

功能描述: (rd)←(rt)>>(rs); PC ← NPC (PC + 4)。按寄存器值逻辑右移指令,将 rt 寄存器中的 32 位数逻辑右移后赋给 rd,移位的位数在 rs 寄存器中。

(16) srav

指令名: 按寄存器值算术右移指令

功能描述: (rd)←(rt)>>>(rs); PC ← NPC (PC + 4)。按寄存器值算术右移指令,将 rt 寄存器中的 32 位数算术右移后赋给 rd,移位的位数在 rs 寄存器中。算术右移 时,符号位不仅要参与移位,还要保留。

(17) jr

指令名: 按寄存器内容转移指令

功能描述:(PC)←(rs); PC ← NPC (PC + 4)。将 rs 寄存器的内容当地址,赋给 PC,从而完成转移,通常可做过程返回语句。

I-型指令

(18) addi

指令名:有符号立即数加法指令

功能描述:(rt)←(rs) + (Sign-Extend)immediate; PC ← NPC (PC + 4)。首先将 16 位有符号立即数扩展到 32 位,然后加上 rs 中的数,结果给 rt 寄存器。

(19) addiu

指令名:无符号立即数加法指令

功能描述:(rt)←(rs) + (Sign-Extend)immediate; PC ← NPC (PC + 4)。首先将 16 位有符号立即数扩展到 32 位,然后加上 rs 中的数,结果给 rt 寄存器。本设计未实现内部异常处理,此指令与 addi 相同。

(20) andi

指令名:立即数逻辑与指令

功能描述:(rt)←(rs) AND (Zero-Extend)immediate; PC ← NPC (PC + 4)。首先将 16 位立即数零扩展到 32 位,然后同 rs 中的数按位逻辑与,结果给 rt 寄存器。

(21) ori

指令名:立即数逻辑或指令

功能描述:(rt)←(rs) ORI (Zero-Extend)immediate; PC ← NPC (PC + 4)。首先将 16 位立即数零扩展到 32 位,然后同 rs 中的数按位逻辑或,结果给 rt 寄存器。

(22) xori

指令名:立即数逻辑异或指令

功能描述:(rt)←(rs) XORI (Zero-Extend)immediate; PC ← NPC (PC + 4)。首先将 16 位立即数零扩展到 32 位,然后同 rs 中的数按位逻辑异或,结果给 rt 寄存器。

(23) sltiu

指令名:小于无符号立即数则设置指令

功能描述:if ((rs)<(sign_extend)immediate) then (rt)←1; else (rt)←0; PC ← NPC (PC + 4)。如果 rs 的值小于立即数 immediate 值(进行的是符号扩展),则设置 rt 为 1,否则 rt 为 0。

(24) lui

指令名:立即数赋值指令

功能描述:(rt)←immediate<<16 & 0FFFF0000H 即(rt)←immediate×65536; PC ← NPC (PC + 4)。首先 16 位立即数赋给 rt 寄存器的高 16 位,低 16 位用 0 填充。也就是将 16 位立即数乘以 65536 后赋值给 rt 寄存器。

(25) lw

指令名:存储器读(字操作)

功能描述:(rt)←Memory[(rs)+(sign_extend)offset]; PC ← NPC (PC + 4)。以 rs 寄存器的内容为基地址,offset 通过符号扩展后形成 32 位的偏移,将基地址加上偏移形成一个 32 位的地址,以此地址从 RAM 中读出一个字(4 字节)赋给 rt 寄存器。本系统中只使用了低 16 位地址,汇编中,offset 可以是变量名。

(26) sw

指令名:存储器写(字操作)

功能描述:Memory[(rs)+(sign_extend)offset]←(rt); PC ← NPC (PC + 4)。以 rs 寄存器的内容为基地址,offset 通过符号扩展后形成 32 位的偏移,将基地址 加上偏移形成一个 32 位的地址,将 rt 寄存器的内容写入到 RAM 中该地址开始的一个字(4 字节)单元。本系统中只使用了低 16 位,汇编中,offset 可以是变量名。

(27) beq

指令名:相等则转移指令

功能描述:if ((rt)=(rs)) then (PC)←(PC)+4+( (Sign-Extend) offset<<2); else PC ← NPC (PC + 4)。如果 rt 和 rs 的值相等,则转移到新的地址。新地址是当前指令的下一条指令地址 (PC+4)加上一个 32 位偏移量。该 32 位偏移量是将 16 位 offset 符号扩展到 32 位,然后左移 2 位(即乘 4)后取低 32 位得到。实际系统中只用了低 16 位地址线。

(28) bne

指令名:不相等则转移指令

功能描述:if ((rt)≠(rs)) then (PC)←(PC)+4+( (Sign-Extend) offset<<2); else PC ← NPC (PC + 4)。如果 rt 和 rs 的值不等,则转移到新的地址。新地址是当前指令的下一条指令地址 (PC+4)加上一个 32 位偏移量。该 32 位偏移量是将 16 位 offset 符号扩展到 32 位,然后左移 2 位(即乘 4)后取低 32 位得到。实际系统中只用了低 16 位地址线。

(29) bgtz

指令名:大于0转移指令

功能描述:if ((rs)>0) then (PC)←(PC)+4+( (Sign-Extend) offset<<2); else PC ← NPC (PC + 4)。如果 rs 的值大于0 则跳转到指定分支。

J-型指令

(30) j

指令名:无条件转移指令

功能描述:(PC)←( (Zero-Extend) address<<2)。无条件转移到新的地址。新地址是 26 位 address 零扩展到 32 位,然后左移 2 位(即 乘 4)后取低 32 位得到。实际系统中只用了低 16 位地址线。

(31) jal

指令名:过程调用指令

功能描述:($31)←(PC)+4; (PC)←( (Zero-Extend)address<<2)。先将下条指令的地址((PC)+4)保存在$31($ra)作为过程的返回地址,然后无条件转移到新的地址。新地址是 26 位 address 零扩展到 32 位,然后左移 2 位(即乘 4) 后取低 32 位得到。实际系统中只用了低 16 位地址线。

二、 模块功能

(1) 顶层模块

模块名:minisys.v

模块功能:整合各模块,用连线连接各个模块,使系统正常工作;设置debug信号。

(2) 时钟模块

模块名:cpuclk.v

模块功能:将100M的系统时钟分频得到23MHz的时钟信号。

(3) 控制模块

模块名:control32.v

功能描述:根据时钟信号、复位信号、所读的指令来控制状态的跳转;根据当前状态、读出指令、返回信号给出控制信号,控制各个部件有序完成系统功能。

(4) 取指模块:

模块名:ifetch32.v

模块功能:根据复位信号复位PC;在时钟信号的作用下,按照给定的控制信号设置PC,并按照PC值从指令存储器中读出指令,将指令存储在IR中。

译码模块

模块名:idecode32.v

模块功能:根据复位信号复位寄存器组;按照读出的指令从寄存器组中读出rs,rt对应寄存器的数据,根据控制信号对指令中的立即数进行扩展,并在时钟的作用下写入数据寄存器;根据控制信号,在时钟的作用下将数据写入寄存器组的指定寄存器中。

(5) 执行模块

模块名:execute32.v

模块功能:根据控制信号,将指定的数据送入ALU,进行算术运算、逻辑运算与移位操作,输出所需要的数据,并在时钟的作用下写入数据寄存器中;根据运算结果获取返回信号,作为控制信号的产生依据。

(6) 数据存储模块

模块名:dememory32.v

模块功能:在时钟的作用下,根据控制信号写入数据,将读出的数据写入数据寄存器中。

(7) 宏定义模块

模块名:para.v

模块功能:存储设计中使用的宏定义。

(二)设计的主要特色

- 采用多周期设计,有利于提高时钟频率。

- 模块划分清楚,结构清晰,具有高内聚、低耦合的特性。如,在执行模块中直接利用返回信号生成写寄存器值,避免其他复杂逻辑

- 部件重用率高,充分考虑硬件特性。如在SUB指令的部件基础上生成BEQ,BNE,BGTZ的返回信号sign与zero,同时产生SLT,SLTU,SLTIU指令的输出信号,避免使用verilog自带的>,<等逻辑运算符,节省硬件资源;利用SLL指令的部件,实现LUI的计算过程;

- 在执行模块ALU的设计中,采用了ABC三个输入的实现方法,保留输入C,用作SLL,SRL,SRA,LUI指令的移位位数的输入,避免了对扩展器的占用;

- 在执行模块的设计中,使用“双符号位”,A,B输入的数据扩展为33位,以此解决溢出问题,主要用于SLTU指令。

- 控制模块信号完整,尝试了多种办法。

- 完成了附加指令要求。

注:涉及执行模块部分将在后文图示中进一步说明。

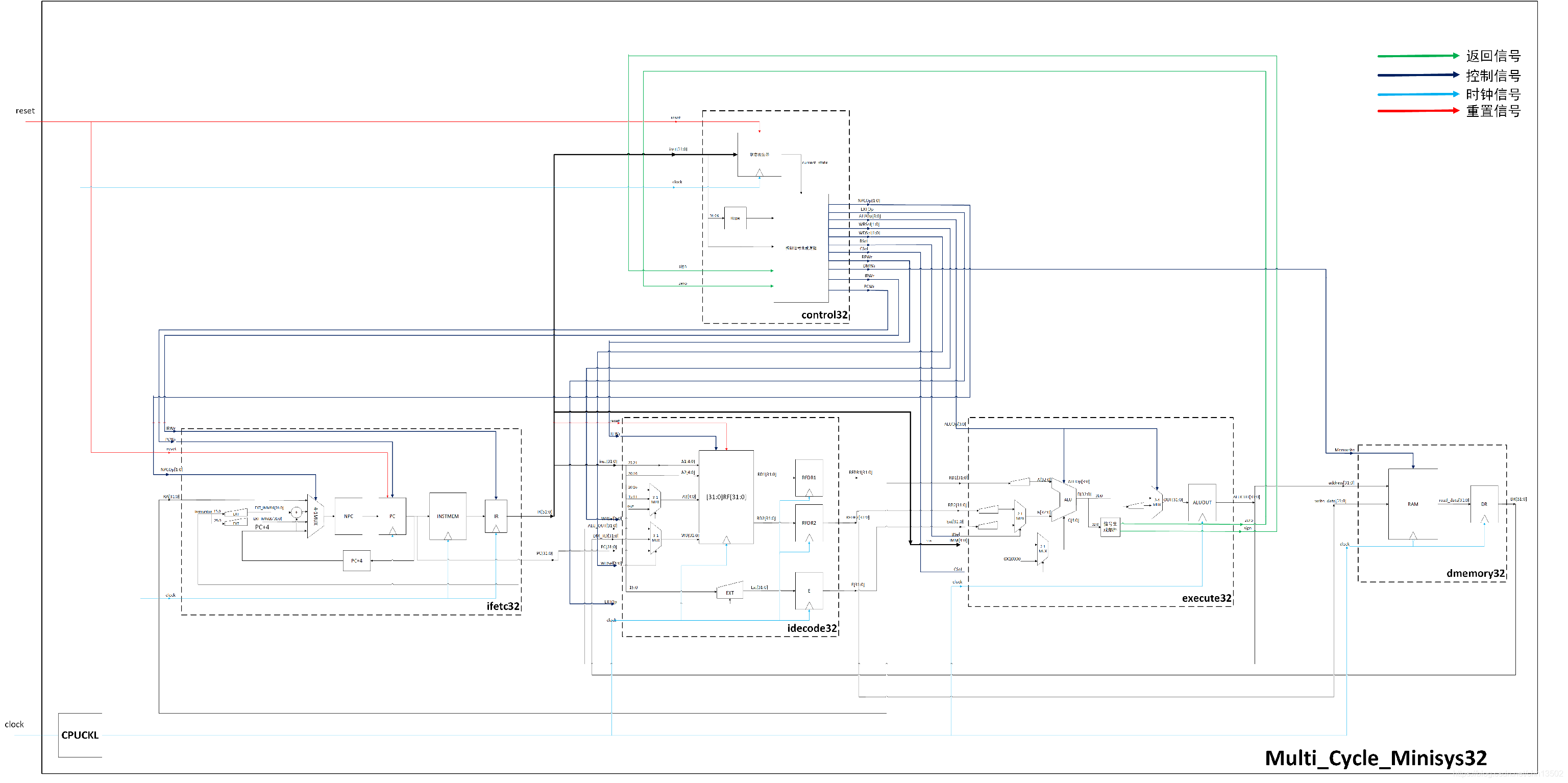

(三)设计的体系结构

(包括体系结构框图和对结构图的简要解释)

简要介绍:该体系结构框图由各个子模块拼合连线后得到,共有五类线路:外部时钟信号(clock,用蓝色表示),外部复位信号(reset,用红色表示),控制信号(用深蓝色表示),返回信号(用绿色表示),数据信号(其他未作特别标注的黑线)。

从图中可以看出,整个系统分为时钟模块,取指模块,译码模块,执行模块,数据存储模块,控制模块。总的来说,系统的主要数据流向如下:

从取指模块ifetch32开始,取值,并将地址和指令输出到PC,IR;IR送入控制模块和译码模块;

控制信号在收到IR的指令后,在对应的状态下发出一系列控制信号,指导其余各个子模块进行工作;

IR送入译码模块后,译码模块从寄存器中取出rs,rd对应寄存器的数据,对指令中的立即数进行扩展,并送入RFDR1,RFDR2,E中;

这些数据随后进入到执行模块,进行算术运算、逻辑运算、移位操作,并输出到ALUOUT,同时产生提供给控制模块的返回信号;

大部分指令会将ALUOUT的值按控制信号回写到译码模块的寄存器组的指定寄存器中;而对于LW,SW指令,则会将ALUOUT的值作为地址,用以读、写数据寄存器,在写存储器时,可以将从寄存器组中读出的数据写入存储器中的指定单元;在读寄存器后,还会将读出的数据送入DR,并最终写回寄存器组的指定寄存器。

对于跳转指令,则有其他特殊的数据流,如,从寄存器组中取得NPC的值,将PC的值写入寄存器组等。

体系结构框图(见下页):

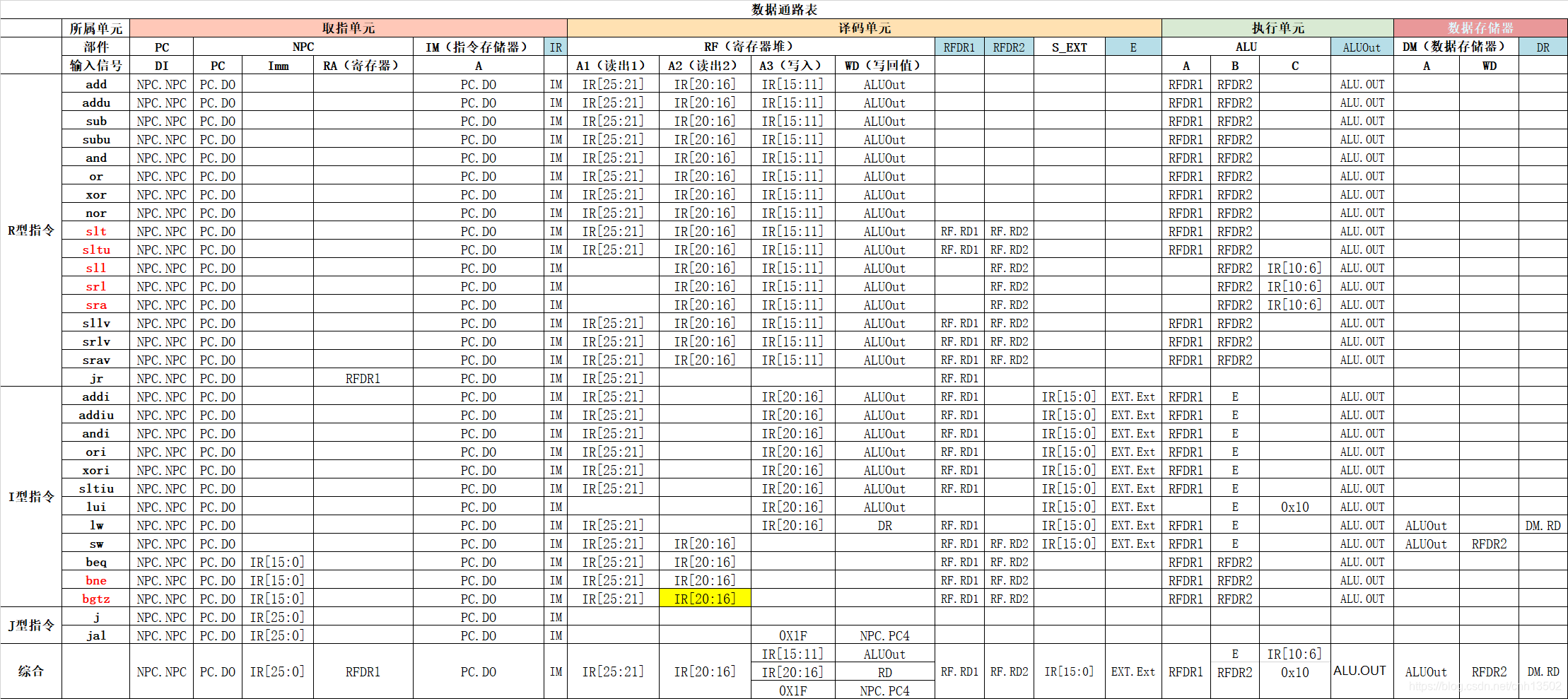

(四)数据通路设计

(包含数据通路主要部件说明及数据通路表)

数据通路主要部件说明:

(1) NPC(Next_PC)

功能描述:根据NPCOp,计算更新的PC值

(2) PC(指令计数器)

功能描述:在时钟沿到来时,用NPC的值更新PC

(3) IM(指令存储器)

功能描述:将PC输入的地址对应的指令输出

(4) IR(指令寄存器)

功能描述:在时钟沿到来时,用从IM取出的指令更新

(5) RF(寄存器组)

功能描述:本系统的寄存器组,可以读出指令中指定rs,rt对应的寄存器的数据,也能在时钟沿到来时将WDSel指定数据源(RD,PC,ALUOUT之一)的数据写入WRSel指定的寄存器(rt,rd,$31之一)中

(6) EXT(扩展单元)

功能描述:将输入的16位立即数按照EXTOp信号进行零扩展或符号扩展

(注:在设计的其他地方也同样使用到了扩展单元(见图示),且扩展的位数和方式各有不同,这里不再赘述。)

(7) RFDR1,RFDR2(寄存器组数据寄存器)

功能描述:在时钟沿到来时,将从RF中取出的数据保存

(8) E(扩展寄存器)

功能描述:在时钟沿到来时,将EXT扩展得到的数据保存

(9) A,B,C(ALU输入)

功能描述:按照BSel,从RFRD2,E中选择一个作为B的输入;按照CSel,从IMM和常数d16选择一个作为C的输入。最终,操作数A,B,C扩展后将作为ALU输入

(10) ALU(数逻运算单元)

功能描述:将A,B,C输入的操作数按照ALUOp信号进行相应的算术运算、逻辑运算或移位操作,输出为D。

(11) 信号生成部件

功能描述:利用“按位与”,以及输出D的符号位生成返回信号zero和sign

(12) ALUOUT(执行部件输出寄存器)

功能描述:将按照ALUOp,利用输出D和返回信号sign,zero得到最终的输出值,在时钟沿到来时进行更新。

(13) RAM(数据存储器)

功能描述:按照ALUOUT给出的地址,将从RF读出的数据在时钟沿到来时写入存储器;或从存储器中读出对应地址的数据。

(14) DR(数据寄存器)

功能描述:在时钟沿到来时,将从RAM中读出的数据写入DR。

数据通路表

本文详细介绍了RISC-V指令集的多个指令,包括加法、减法、逻辑运算、移位、比较、分支和跳转等。设计中涵盖了I型、R型和J型指令,实现了数据的读取、存储、运算和控制流程。模块化设计确保了系统的高效性和可扩展性,同时注重硬件资源的利用率和时钟频率的优化。

本文详细介绍了RISC-V指令集的多个指令,包括加法、减法、逻辑运算、移位、比较、分支和跳转等。设计中涵盖了I型、R型和J型指令,实现了数据的读取、存储、运算和控制流程。模块化设计确保了系统的高效性和可扩展性,同时注重硬件资源的利用率和时钟频率的优化。

2139

2139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?