三、软件设计

3.1 开发环境相关

3.2 base project构建

3.2.1 systick定时器

3.2.2 多个stack

3.2.3 TCM与SRAM

3.2.4 链接脚本与启动模式

3.2.5 SRAM首选和ATCM次选

3.2.6 串口5和DMA

3.2.7 bus master

3.2.8 segger rtt

3.2.9 总结

3.2.9.1 单工程

3.2.9.2 load+app

3.3 日志系统

3.4 中间层构建

3.4.1 了解e2s和fsp

3.4.2 fsp工程目录结构简介

四、从0开始卷出一个新项目之瑞萨RZN2L软件基础工程构建

3.2 base project构建

-

目标:构建一个通用的、排除各种“小毛刺”的、TCM SRAM可同时使用的、可用于产品开发级的base project。以备后续移植日志系统、中间层、公司平台产品。这里只是分享经营,抛砖引玉。

3.2.1 systick定时器

本节之后,通过移植coremark来分析和理解RZN2L(R52)不同于cortex M3的一些要点,最终的目的是创建一个通用的base project,这样我们的一个适用于产品级的RZN2L平台就创建出来了。

移植cormark关键点:

-

时钟:只有cortex M才有systick timer

-

迭代次数:#define ITERATIONS 20000

-

编译器和优化等级:COMPILER_VERSION,COMPILER_FLAGS

-

printf重定向一样

-

coremark结果只用于理解芯片和对比ATCM SRAM

//void SysTick_Handler(void)

//{

// cnt++;

//}

/*

* g_timer0CB

* rzn2l core R52 havenot systick, so init g_timer0 cnt

*/

extern volatile clock_t cnt;

void g_timer0CB(timer_callback_args_t *p_args)

{

if (TIMER_EVENT_CYCLE_END == p_args->event)

{

cnt++;

}

}

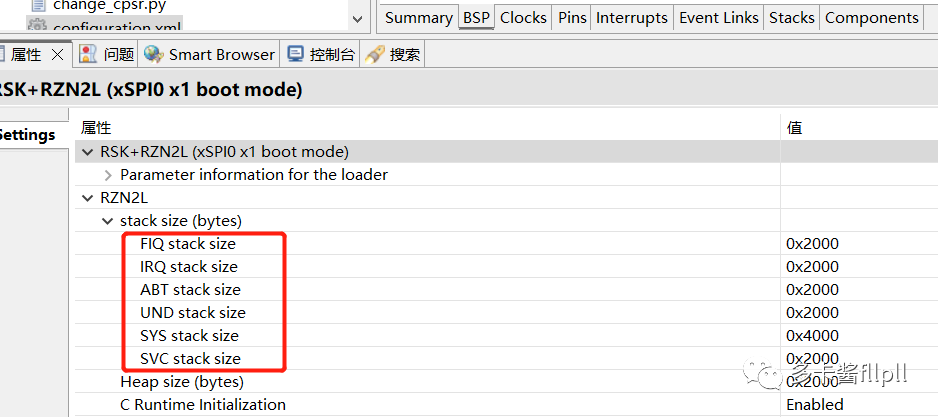

3.2.2 多个stack

-

coremark结果失败,但未提示stack溢出

-

[16:09:06.088]收←◆2K performance run parameters for coremark.

[0]ERROR! list crc 0x7271 - should be 0xe714

[0]ERROR! matrix crc 0x7fc1 - should be 0x1fd7

[0]ERROR! state crc 0x44f1 - should be 0x8e3a

CoreMark Size : 666

Total ticks : 30024

Total time (secs): 30.024000

Iterations/Sec : 666.133760

Iterations : 20000

Compiler version : GCC10.3.1 20210824 (release)

Compiler flags : Please put compiler flags here (e.g. -o3)

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0x7271

[0]crcmatrix : 0x7fc1

[0]crcstate : 0x44f1

[0]crcfinal : 0xf1c1

Errors detected

[12:37:01.637]收←◆hello word!

date:Oct 17 2023

time:12:36:15

file:../src/hal_entry.c

func:hal_entry,line:126

hello world!

PI=3.141593

start coremain!!!

[12:37:16.656]收←◆2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 15006

Total time (secs): 15.006000

Iterations/Sec : 1332.800213

Iterations : 20000

Compiler version : GCC10.3.1 20210824 (release)

Compiler flags : Please put compiler flags here (e.g. -o3)

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x382f

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 1332.800213 / GCC10.3.1 20210824 (release) Please put compiler flags here (e.g. -o3) / STACK

FSP_PRIV_CLOCK_CPU0=400000000

running!!!

3.2.3 TCM与SRAM

-

目标对比TCM与SRAM执行速度

-

coremark结果处理编译器、优化等级外,主要受text data,次要stack heap

-

所以需要修改ld

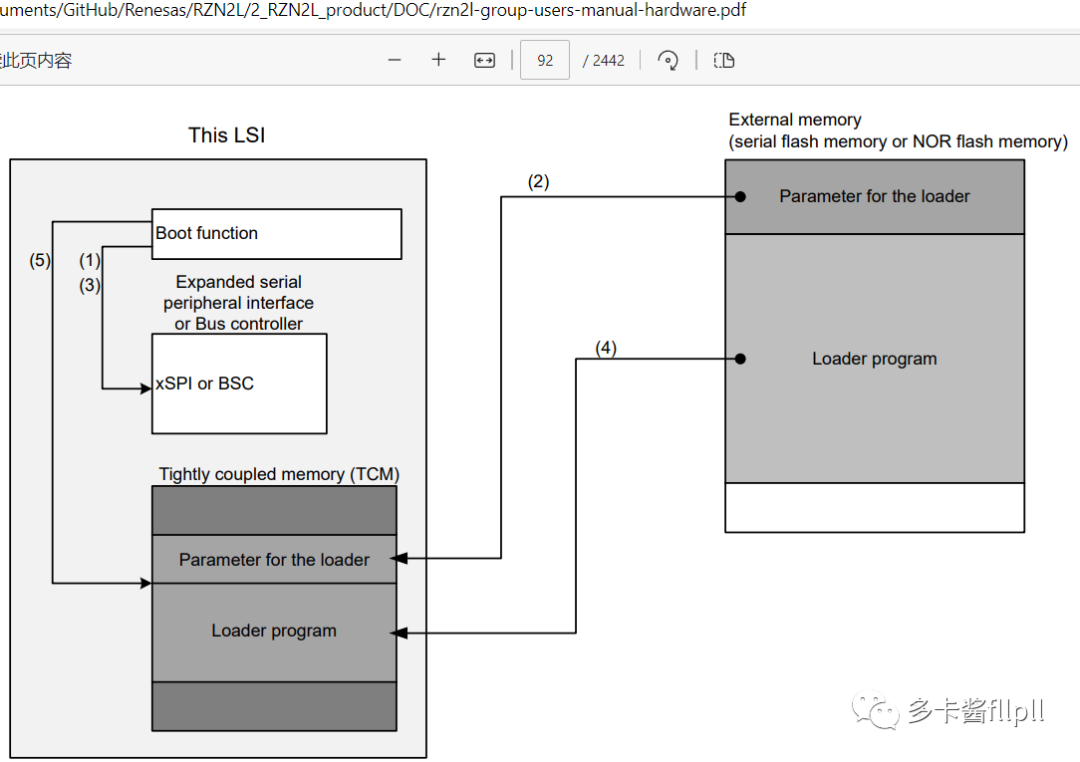

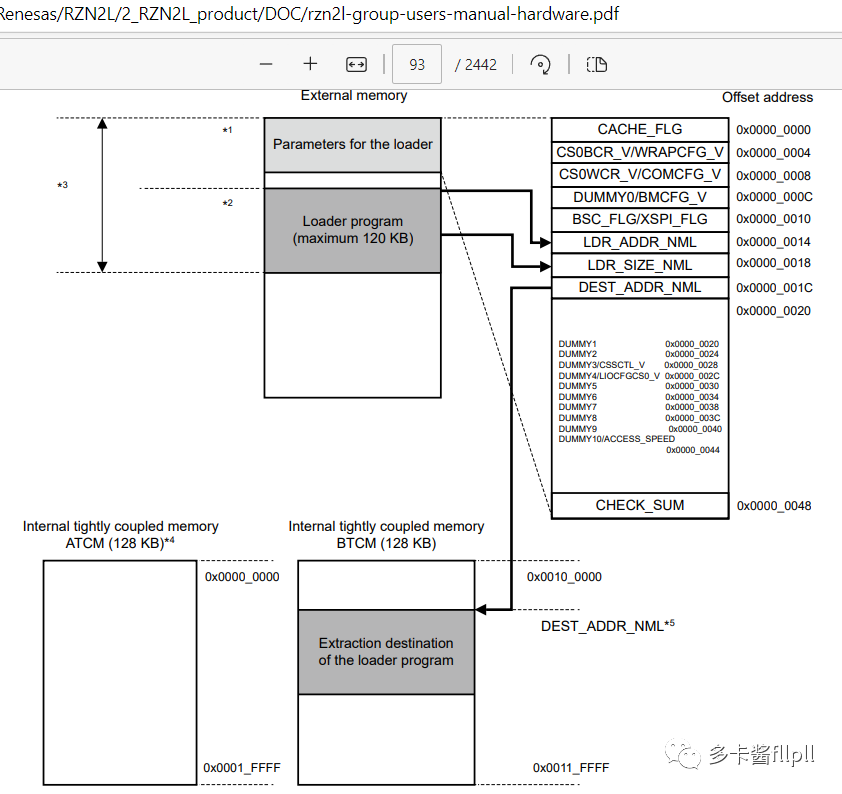

3.2.4 链接脚本与启动模式

-

参考例程修改ld ATCM->sram mirror

-

./script/fsp_xspi0_boot.ld fsp_ram_execution.ld自动更新

-

xspi0 boot流程

-

startup.c复制初始化内存数据

-

-

hello word!

date:Oct 17 2023

time:12:38:17

file:../src/hal_entry.c

func:hal_entry,line:126

hello world!

PI=3.141593

start coremain!!!

[12:39:30.771]收←◆2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 34391

Total time (secs): 34.391000

Iterations/Sec : 581.547498

Iterations : 20000

Compiler version : GCC10.3.1 20210824 (release)

Compiler flags : Please put compiler flags here (e.g. -o3)

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x382f

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 581.547498 / GCC10.3.1 20210824 (release) Please put compiler flags here (e.g. -o3) / STACK

FSP_PRIV_CLOCK_CPU0=400000000

running!!!

3.2.5 SRAM首选和ATCM次选

-

修改ld文件和startup.c文件

.atcm_text : AT (_matcm_text)

{

_atcm_text_start = .;

./src/coremark/*.o(.text*)

_atcm_text_end = .;

} > ATCM

.atcm_data : AT (_matcm_data)

{

_atcm_data_start = .;

__atcm_data_start = .;

./src/coremark/*.o(.data*)

__atcm_data_end = .;

__atcm_bss_start = .;

./src/coremark/*.o(.bss*)

./src/coremark/*.o(COMMON)

__atcm_bss_end = . ;

_atcm_data_end = .;

} > ATCM

#if FSP_XSPI0_BOOT_SRAM_ATCM//fsp_xspi0_boot_SRAM_ATCM.ld

" ldr r0, =_matcm_text \n"

" ldr r1, =_atcm_text_start \n"

" ldr r2, =_atcm_text_end \n"

" cmp r2, r1 \n"

" beq copy_ATCM_APP_TEXT_end \n"

"copy_to_ATCM_APP_TEXT: \n"

" ldrb r3, [r0], #0 \n"

" strb r3, [r1], #0 \n"

" add r0, r0, #1 \n"

" add r1, r1, #1 \n"

" cmp r2, r1 \n"

" bne copy_to_ATCM_APP_TEXT \n"

"copy_ATCM_APP_TEXT_end: \n"

" dsb \n" /* Ensuring data-changing */

" ldr r0, =_matcm_data \n"

" ldr r1, =_atcm_data_start \n"

" ldr r2, =_atcm_data_end \n"

" cmp r2, r1 \n"

" beq copy_ATCM_APP_DATA_end \n"

"copy_to_ATCM_APP_DATA: \n"

" ldrb r3, [r0], #0 \n"

" strb r3, [r1], #0 \n"

" add r0, r0, #1 \n"

" add r1, r1, #1 \n"

" cmp r2, r1 \n"

" bne copy_to_ATCM_APP_DATA \n"

"copy_ATCM_APP_DATA_end: \n"

" dsb \n" /* Ensuring data-changing */

#endif

hello word!

date:Oct 17 2023

time:12:40:42

file:../src/hal_entry.c

func:hal_entry,line:126

hello world!

PI=3.141593

start coremain!!!

[12:41:37.160]收←◆2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 14924

Total time (secs): 14.924000

Iterations/Sec : 1340.123291

Iterations : 20000

Compiler version : GCC10.3.1 20210824 (release)

Compiler flags : Please put compiler flags here (e.g. -o3)

Memory location : STACK

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0x382f

Correct operation validated. See README.md for run and reporting rules.

CoreMark 1.0 : 1340.123291 / GCC10.3.1 20210824 (release) Please put compiler flags here (e.g. -o3) / STACK

FSP_PRIV_CLOCK_CPU0=400000000

running!!!

3.2.6 串口5和DMA

-

串口5不支持dma功能

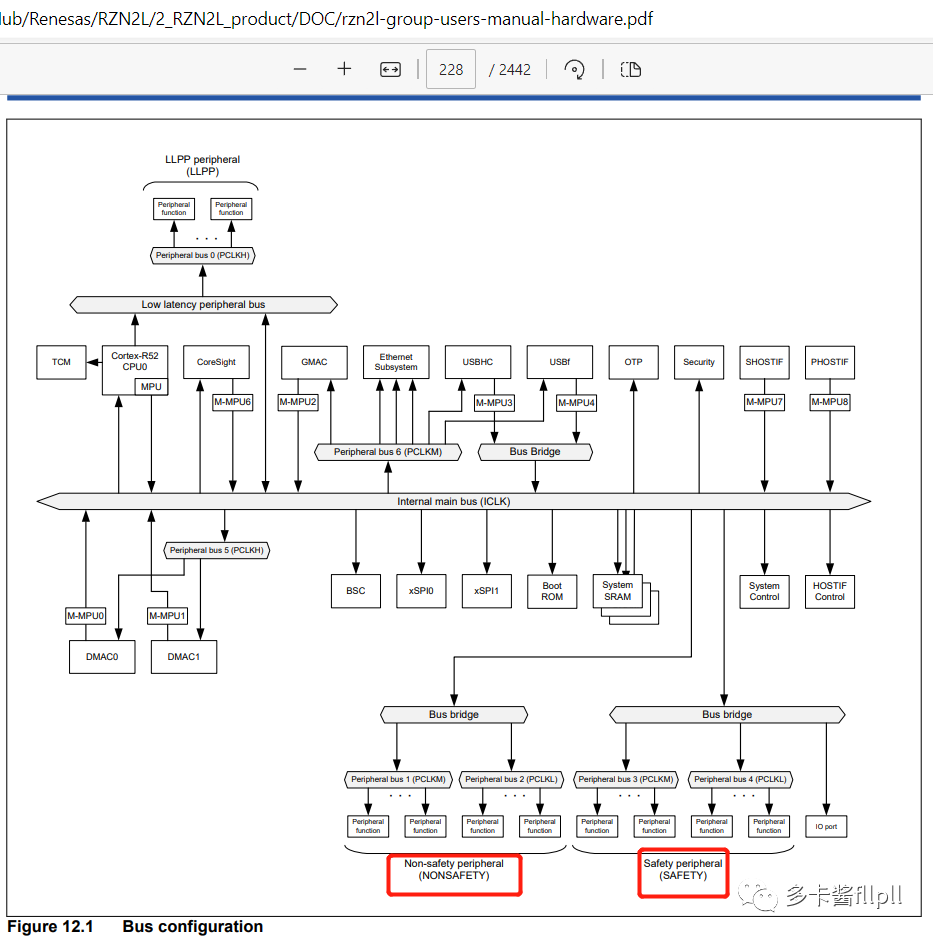

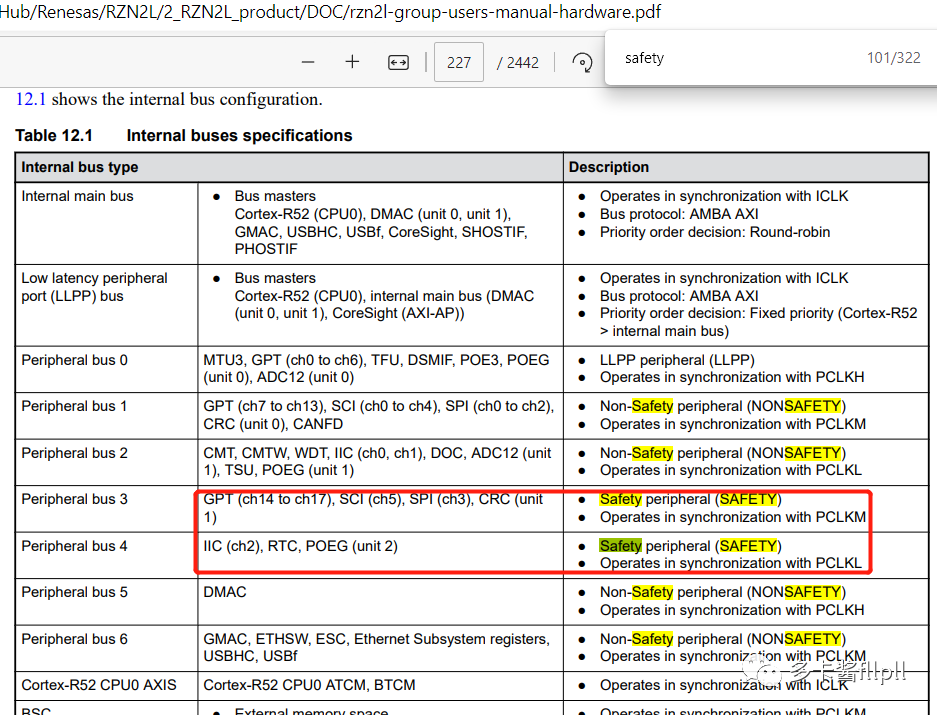

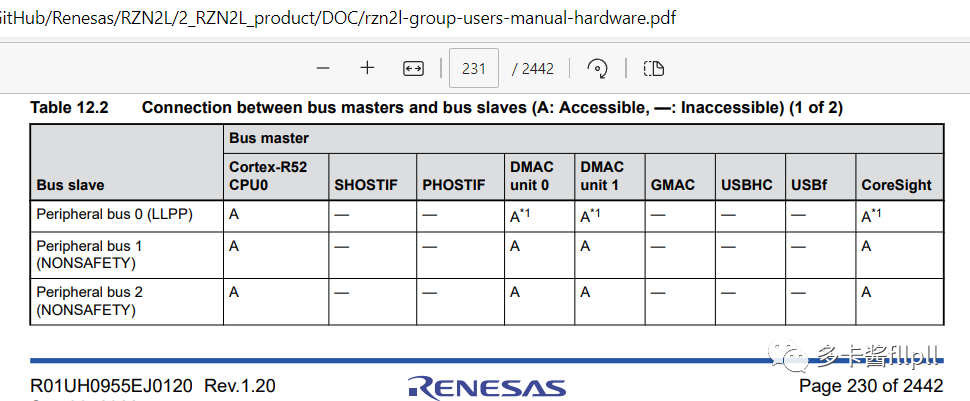

3.2.7 bus master

/* region 0 (ATCM) */

#define EL1_MPU_REGION00_BASE_L (0x0000 & 0xFFC0) + OUTER_SHAREABLE + EL1RW_EL0RW + EXECUTE_ENABLE

#define EL1_MPU_REGION00_BASE_H (0x0000 & 0xFFFF)

#define EL1_MPU_REGION00_LIMIT_L (0xFFFF & 0xFFC0) + ATTRINDEX3 + REGION_ENABLE

#define EL1_MPU_REGION00_LIMIT_H (0x0001 & 0xFFFF)

/* region 1 (BTCM) */

#define EL1_MPU_REGION01_BASE_L (0x0000 & 0xFFC0) + OUTER_SHAREABLE + EL1RW_EL0RW + EXECUTE_ENABLE

#define EL1_MPU_REGION01_BASE_H (0x0010 & 0xFFFF)

#define EL1_MPU_REGION01_LIMIT_L (0xFFFF & 0xFFC0) + ATTRINDEX3 + REGION_ENABLE

#define EL1_MPU_REGION01_LIMIT_H (0x0011 & 0xFFFF)

/* region 2 (System RAM) */

#define EL1_MPU_REGION02_BASE_L (0x0000 & 0xFFC0) + NON_SHAREABLE + EL1RW_EL0RW + EXECUTE_ENABLE

#define EL1_MPU_REGION02_BASE_H (0x1000 & 0xFFFF)

#define EL1_MPU_REGION02_LIMIT_L (0xFFFF & 0xFFC0) + ATTRINDEX1 + REGION_ENABLE

#define EL1_MPU_REGION02_LIMIT_H (0x1017 & 0xFFFF)

/* region 3 (System RAM mirror) */

#define EL1_MPU_REGION03_BASE_L (0x0000 & 0xFFC0) + OUTER_SHAREABLE + EL1RW_EL0RW + EXECUTE_ENABLE

#define EL1_MPU_REGION03_BASE_H (0x3000 & 0xFFFF)

#define EL1_MPU_REGION03_LIMIT_L (0xFFFF & 0xFFC0) + ATTRINDEX3 + REGION_ENABLE

#define EL1_MPU_REGION03_LIMIT_H (0x3017 & 0xFFFF)

3.2.8 segger rtt

-

INIT()失败,不支持rtt?

#define INIT() { \

volatile SEGGER_RTT_CB* pRTTCBInit; \

pRTTCBInit = (volatile SEGGER_RTT_CB*)((char*)&_SEGGER_RTT + SEGGER_RTT_UNCACHED_OFF); \

do { \

if (pRTTCBInit->acID[0] == '\0') { \

_DoInit(); \

} \

} while (0); \

}

3.2.9 总结

3.2.9.1 单工程

-

在starup.c中引导norflash到sram和atcm,参考coremark工程

3.2.9.2 load+app

r01an6737jj0110-rzn2l-separating-loader-and-application

-

在loader中引导,在app中初始化

-

修改app ld sram->sram mirror

-

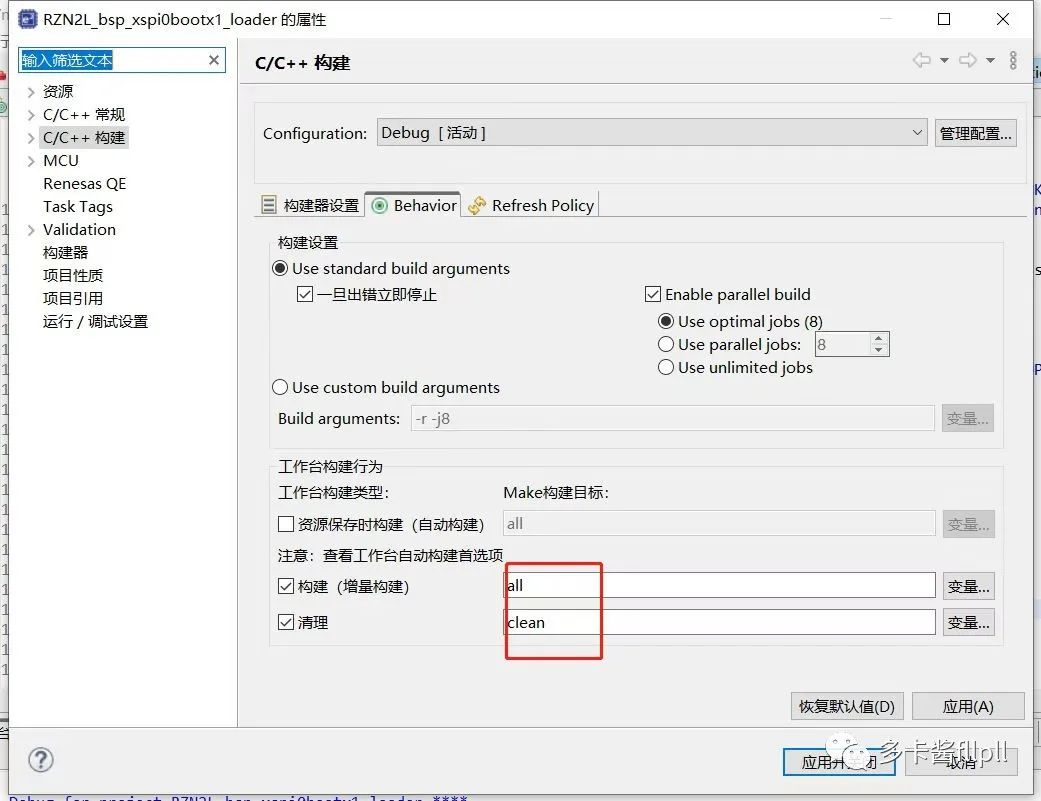

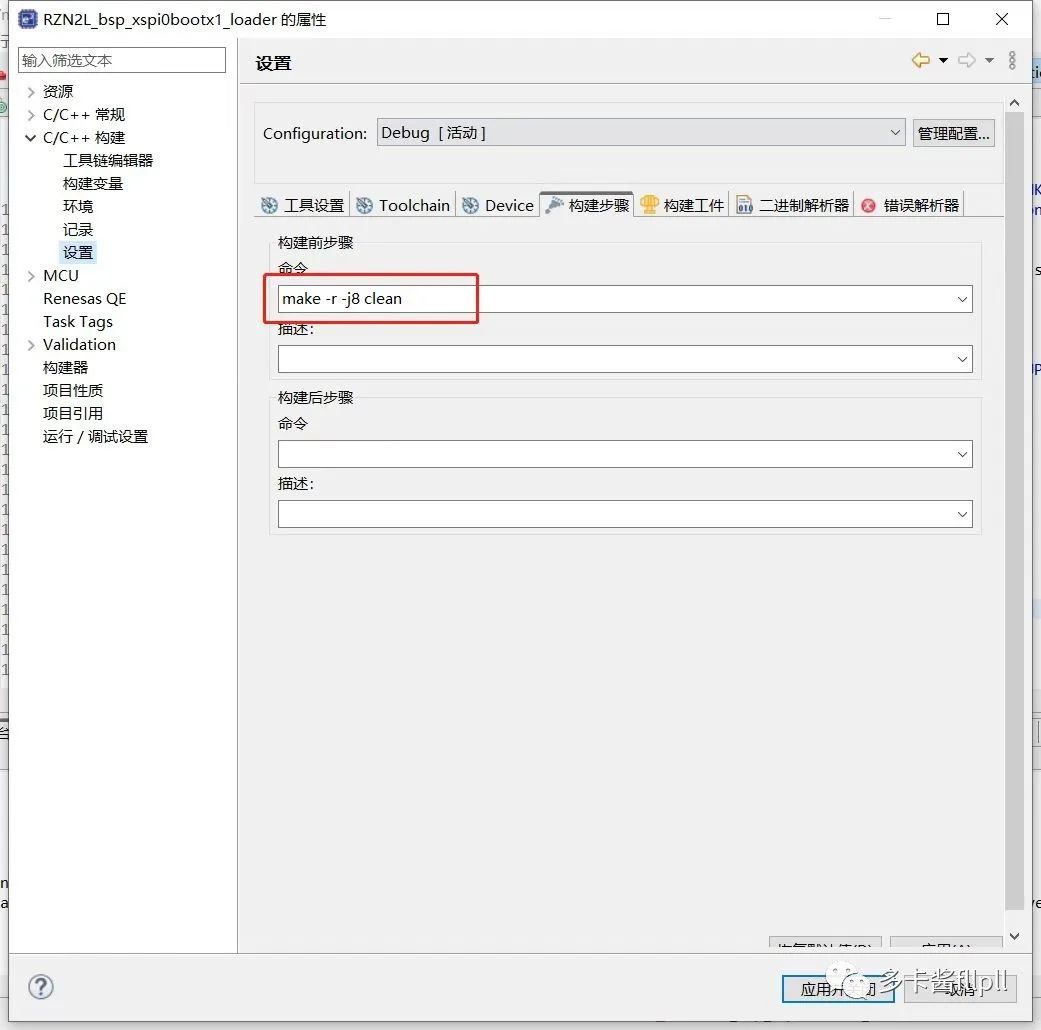

编译前手动clean loader或修改配置自动clean

-

-

3.3 日志系统

-

请参考从0卷出一个新项目之RA6M5系列。其中的支持同步异步打印,支持printf、littlefs、rtt等,并且其中的bug在fsp4.6.0已经修复了,可以参考移植。

3.4 中间层构建

3.4.1 了解e2s和fsp

-

因为fsp(Flexible Software Package)实质是大系列(RA RZN等)整合软件包+代码生成工具。

-

精通编译器当然也可以不用e2s,甚至IDE,但个人感觉fsp是绕不开的。

-

https://github.com/renesas/rzn-fsp:

-

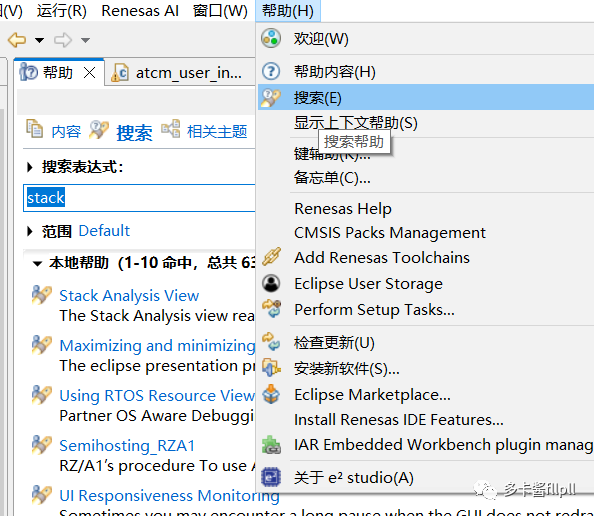

e2s的帮助功能

Flexible Software Package (FSP) for Renesas RZ/N series.

FSP is the next generation Arm® MCU software package from Renesas, that enables secure devices and IoT connectivity through production ready peripheral drivers, FreeRTOS, and portable middleware stacks. FSP includes best-in-class HAL drivers with high performance and low memory footprint. Middleware stacks with FreeRTOS integration are included to ease implementation of complex modules like communication and security. The e² studio provides support with intuitive configurators and intelligent code generation to make programming and debugging easier and faster.

FSP uses an open software ecosystem and provides flexibility in using your preferred RTOS, legacy code, and third-party ecosystem solutions.

Related Links

FSP Releases : https://github.com/renesas/rzn-fsp/releases

FSP Documentation : https://renesas.github.io/rzn-fsp

RZ/N2L Product Information : https://www.renesas.com/rzn2l

e² studio : https://www.renesas.com/e2studio

Support : https://www.renesas.com/support

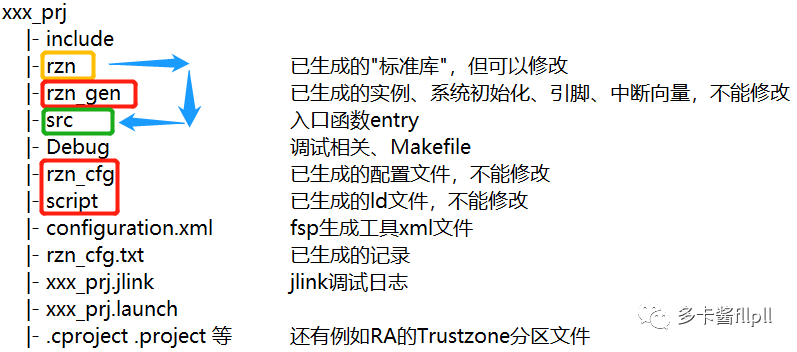

3.4.2 fsp工程目录结构简介

1137

1137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?