先进芯片封装初级2

一、晶圆制造与加工

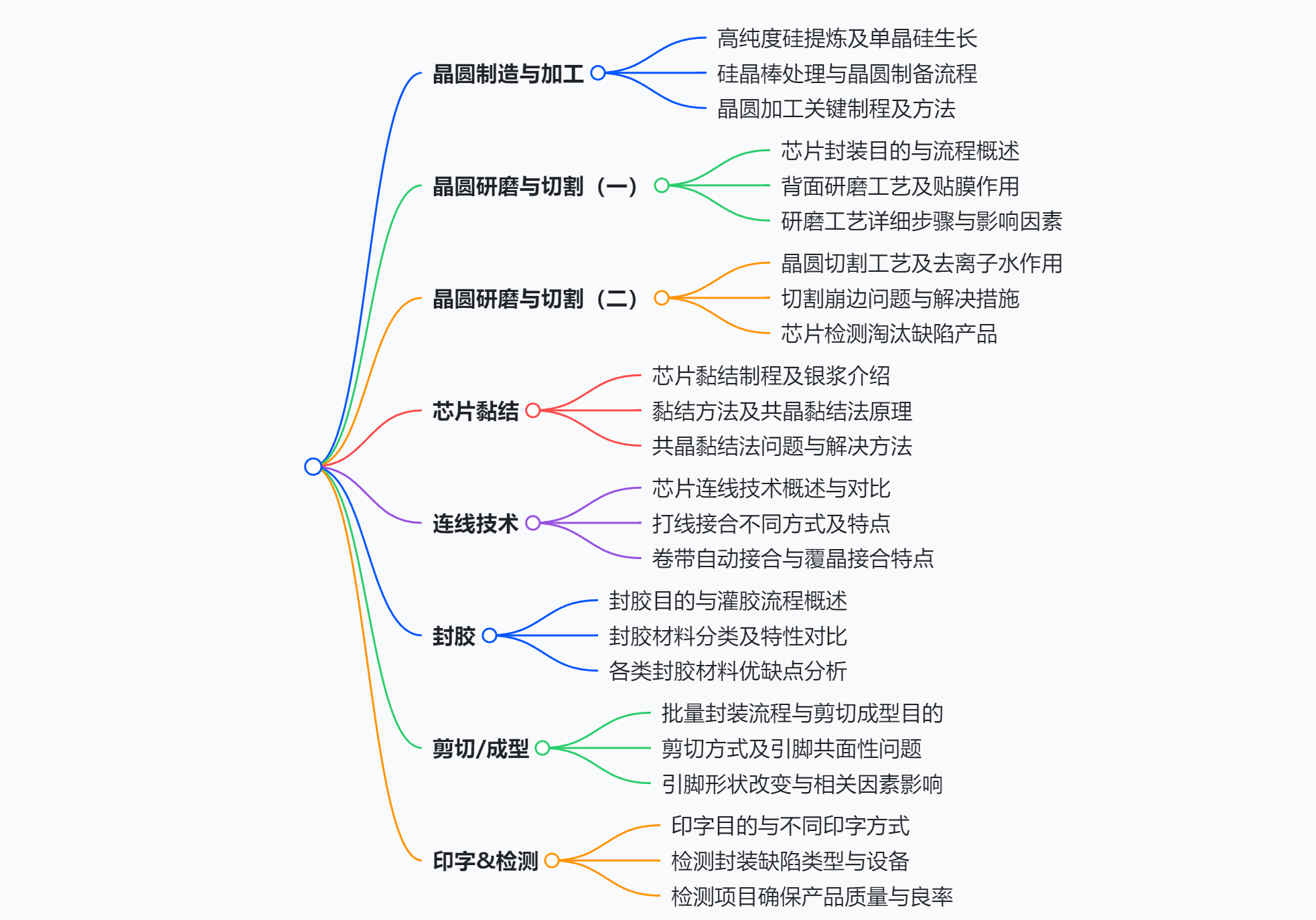

目录

(一)硅晶圆制造

-

原料与纯度提升

-

从沙子(主要成分二氧化硅)开始,通过一连串化学反应提炼成纯度为 99.999999999% 以上的硅,多晶硅中的原子排列杂乱,再制成单晶硅,单晶硅中的原子整齐朝同一方向排列,整块材料只有一个晶粒。

-

-

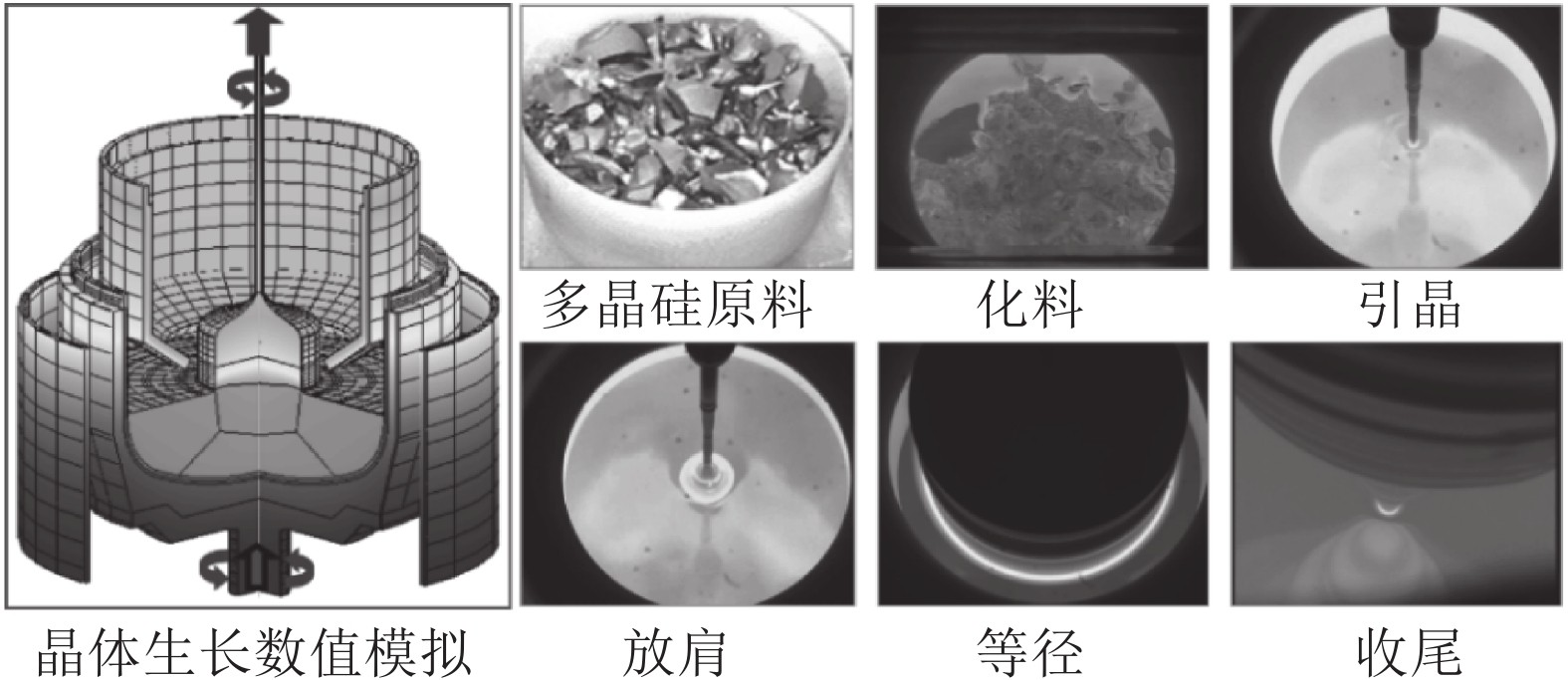

单晶硅生长

-

单晶硅生长采用提拉法(CZ 法),将晶种浸入硅熔液中,以一定速度旋转并缓慢向上提拉,晶种的旋转速度和拉升速度影响硅晶棒的粗细,拉升速度越慢,硅晶棒越粗,能做出更大的晶圆。冷却后的硅晶棒呈银色,像重金属口味的超巨型油条。

-

-

硅晶棒处理

-

外型处理:对硅晶棒进行切割、研磨、抛光等操作,以获得所需的晶圆尺寸和表面平整度。

-

切片:使用切割线将硅晶棒切割成薄片,得到晶片。切割时线轴高速转动带动线切开晶棒。

-

圆边处理:为避免晶圆边角被碰碎,将其磨成圆弧。

-

表面处理:包括晶圆研光(Wafer Lapping)去除损伤表面硅、晶圆蚀刻用化学蚀刻液更彻底去除损伤表面、晶圆退火消除应力、晶圆抛光使晶圆表面光亮。抛光时上面的转盘加压盖在晶圆上并加入研磨液,研磨液中的坚硬小颗粒将晶圆磨亮。

-

(二)晶圆加工

-

“铺” 字诀

-

在晶圆上铺设一层层薄膜,薄膜可以是二氧化硅、氧化硅等绝缘体,也可以是金属(如多晶硅、氮化物等)。可通过热氧化法(将晶圆放入烤炉通入氧气形成二氧化硅膜)、化学气相沉积法(CVD,几种气体反应产生固体沉积物形成多种膜)、物理气相沉积法(PVD,包括蒸镀和溅镀,溅镀用氩离子轰炸靶材使原子溅射到晶圆上形成薄膜)。

-

-

“刻” 字诀(微影制程)

-

光阻涂布:把光阻(分为正光阻和负光阻,会因紫外线照射发生化学变化)滴在晶圆中央,晶圆高速旋转利用离心力使光阻均匀分散到表面。

-

曝光:透过光罩和透镜让部分光阻被紫外线照射发生化学变化,光罩上的图案通过光的选择性透过在晶圆上形成缩小版图案。

-

显影:用显影剂浸泡或冲洗晶圆,使被光照到的光阻被溶解,光罩图案出现在晶圆上。

-

蚀刻:把晶圆泡到腐蚀液里或用离子轰炸,光阻保护下方薄膜,未被光阻覆盖的薄膜被蚀刻掉。

-

光阻剥除:去除晶圆上剩余的光阻。

-

-

“掺” 字诀

-

纯净硅不导电,掺入特定杂质(如硼、磷等)的硅能导电,可制作晶体管等电子元件。通过离子植入(用电场加速特定离子射入晶圆)和退火(加热晶圆使硅原子和杂质排列整齐、均匀分布)实现。

-

二、晶圆研磨与切割(一)

(一)芯片封装流程与研磨切割目的

-

封装流程概述

-

芯片封装是将晶圆切割分离成一颗颗晶粒,外接信号线传递电路讯号,并用 IC 封胶包裹保护 IC 元件。大致流程包括晶片研磨、晶片切割、晶粒黏结、打线通讯、封胶等。

-

-

研磨切割目的

-

半导体芯片越薄,可堆叠更多芯片,集成度越高,但集成度高可能影响产品性能。决定晶圆厚度的研磨方法对降低成本和保证产品质量至关重要。研磨切割可实现尺寸和封装标准化,便于取置芯片,保护芯片免受物理损害和环境影响,提供机械支撑,进行散热和温度管理,以及实现引脚连接和电气连接。

-

(二)背面研磨工艺

-

贴膜保护

-

进行背面研磨时,硅化合物会扩散,晶圆可能因外力破裂或翘曲,所以需在晶圆背面贴上紫外线(UV)蓝膜保护。研磨后用紫外线照射可降低胶带黏着性,便于剥离。

-

-

研磨步骤

-

包括粗磨、精磨和化学机械抛光等工艺,使用研磨轮和抛光垫,配合浆料或去离子水进行研磨和抛光,以达到所需的晶圆厚度和表面平整度。研磨过程中晶圆受到下压的力,不同工艺适用于不同厚度的晶圆。

-

三、晶圆研磨与切割(二)

(一)晶圆切割工艺

-

切割过程及冲洗

-

晶圆切割通过研磨进行,会产生大量细小粉尘,必须不断用去离子水(DI 水)冲洗,以免污染晶粒。切割时使用切割机(金刚石层)沿着划线切割,在 UV 胶带背面照射紫外线可降低黏着性,便于将芯片从胶带上取下。

-

(二)切割崩边问题

-

产生机理

-

晶圆由脆性材料(如硅、砷化镓等)制成,弹性极限和强度接近,脆性高、断裂韧性低,在切割过程中容易发生崩边现象。

-

-

解决方案

-

可通过优化工艺条件(如改变磨轮单个磨粒的最大切削深度公式中的变量,包括划片刀平均颗粒尺寸、主轴转速、工件进给速度和切削深度等)、优化划片刀(如选择合适的金刚砂颗粒度、结合剂强度和密度)、进行预切割、优化冷却水等方式降低切割过程中的内应力,减少晶圆崩裂损失。

-

(三)芯片检测

-

切割后在显微镜下对芯片进行外观检测,淘汰有缺陷、损伤、污染的芯片。

四、芯片黏结

(一)芯片黏结制程与银浆

-

制程步骤

-

将 IC 芯片固定于封装基板或导线架中芯片座上,利用环氧树脂(银浆)黏结。银浆一般含 60 - 70% 金属银微粒,有将芯片固定、散热、导电作用,按烧结温度分为高温、中温、低温银浆,不同类型银浆适用于不同应用场景(如高温银浆用于太阳能电池、压电陶瓷等,低温银浆用于薄膜开关及键盘线路)。

-

(二)黏结方法

-

共晶黏结法(焊接黏结法)

-

利用金 - 硅合金在 3wt% 硅、363°C 时的共晶反应特性进行黏结。将 IC 芯片置于镀有金或银膜的基板芯片座上,加热至约 425°C,通过金 - 硅交互扩散完成接合。共晶反应是二元合金系统中具有共晶成分的液体在共晶温度下同时凝固形成两固体相的过程(如 Pb - Sn 合金相图中有 L、α、β 相及相应单相区、双相区和三相共存线)。共晶黏结需在热氮气遮蔽环境中进行,防止硅氧化,同时要注意提升湿润性(如除去氧化表层、借助真空焊接环境降低焊料表面张力),避免孔洞产生导致接合强度与热传导性降低、应力分布不均等问题。焊接黏结法使用的焊料有金 - 矽、金 - 锡、金 - 锗等硬质合金与铅 - 锡、铅 - 银 - 铟等软质合金,也需在热氮气环境中进行,硬质焊料抗疲劳与抗潜变特性好但易产生热膨胀系数差异引致的应力破坏问题,软质焊料可改善此缺点但使用前需在芯片背面镀多层金属薄膜促进焊料润湿。

-

-

玻璃胶黏结法(仅适用于陶瓷封装)

-

用戳印、网印或点胶方法将含有银的玻璃胶涂于基板芯片座上,置妥 IC 芯片后加热除去胶中有机成份,使玻璃熔融接合。优点是可得到无孔洞、优良热稳定性、低残余应力与低湿气含量的接合,但黏结热处理过程中冷却温度须谨慎控制以防接合破裂,胶中有机成份须完全除去,否则影响封装结构稳定性与可靠度。

-

-

高分子胶黏结法(塑胶封装常用)

-

利用戳印、网印或点胶等方法将环氧树脂或聚亚酰胺等高分子胶涂布于导线架芯片座上,置妥 IC 芯片后加热完成黏结(可填入银提高热传导性),胶材可制成固体膜状热压接合。优点是低成本且能配合自动化生产制程,缺点是热稳定性较差且易导致有机成份泄漏影响封装可靠度。高分子材料与铜引脚热膨胀系数相近,常见塑胶封装引脚材质有铜、镍铜合金、镀锡铜和镀金铜等。

-

(三)黏结失败情况

-

包括裂缝划痕、断裂、污染、错位、缺失、堆叠等。

五、连线技术

(一)连线技术概述与对比

-

技术类型及功能

-

IC 芯片需与封装基板或导线架完成电路联接才能实现电子讯号传递,主要连线技术有打线接合(Wire Bonding)、卷带自动接合(Automated Bonding,TAB)、覆晶接合(Flip Chip,FC)。不同技术在面积比例、重量比、厚度比、I/O 数、矩阵及环列接点间距等方面存在差异。

-

(二)打线接合

-

接合方式与材料

-

在完成芯片黏结后,将细金属线或金属带依序打在芯片与导线架或封装基板的接垫上形成电路联接。打线用材料一般是线径 15 - 50 微米的金属线材,常见有金(Au)、铜(Cu)、铝(Al)、银(Ag)等,不同材料适用于不同接合方式(如超音波接合常见导线材为铝 - 镁 - 硅、铝 - 铜等合金,热压接合与热超音波接合标准导线材为 99.99% 纯度的金线)。

-

-

接合方式分类

-

超音波接合(U/S):以接合楔头引导金属线加压于接垫上,输入 20 - 60 千赫兹、振幅 20 - 200mm 的超音波,借音波震动与加压产生冷焊效应完成接合。优点是接触温度低、接点尺寸较小且回绕轮廓低,适用于接垫间距小的电路联线,但导线回绕方向必须平行于两接点连线方向,对大面积芯片电路联结不便,且在楔形接合过程中需随时调整芯片与封装结构方向,会降低接合速度。

-

热压接合(T/C):金线穿过高温耐火材料制成的毛细管状接合工具,金属线末端烧灼成球(是金属线直径的 2.5 - 3.0 倍),接合时金球受压变形增加接合面积、减低界面粗糙度影响、穿破氧化层等妨碍接合因素。热压接合通常采用接合工具与基板接垫同时加温方式进行。

-

热超音波接合(T/S):先让金属线末端成球,再以超声波进行导线材金属球与接垫金属接合,接合工具不加热,基板维持在 150 - 250 摄氏度温度,可抑制接合界面的介金属化合物成长及减少基板高温劣化机会。

-

(三)卷带自动接合(TAB)

-

制程与结构特点

-

由美国通用电气公司开发,包括树脂材料、晶片制作、铜箔、制程胶卷、凸块制作、线路制作、切割、上片、线路连结、封装成型、电性检查、电路板制成等步骤。卷带结构有单层、双层、三层之分,各有优缺点(如单层卷带价格低、能应用于高温结合,但不能进行电性测试且容易变形;双层卷带有高分子膜支撑强度较好、允许复杂电路图形设计与制程中电性测试,但引脚剥离强度较低、容易弯曲变形且价格昂贵;三层卷带机械性能与引脚平整度优良、允许复杂电路设计与电性测试,但制程复杂、成本高且不适合高温接合制程)。

-

(四)覆晶接合(FC)

-

接合原理与流程

-

精髓在于控制接点高度(又称 C4 接合),属于平列式接合。先在 IC 芯片接垫上长成焊接凸块,通过 Reflow 热处理配合焊锡熔融时的表面张力效应,将芯片翻转置放到封装基板上并完成对位后,使凸块成球状完成芯片与基板的接合,芯片底部使用电气与绝缘胶填充。

-

-

与打线接合对比

-

覆晶接合芯片上的金属焊球或金属凸块与基板的金属焊盘对齐连接,打线接合是芯片上的金属线通过焊接与基板金属焊盘连接。覆晶接合具有更短信号传输路径、较低电阻电感、更好热管理和散热性能、较高连接密度、更小封装尺寸、更稳定可靠耐久的连接等优点,常用于高性能应用(如高速通信、微处理器、FPGA 和高密度封装等领域);打线接合连接路径较长,一般适用于较低频率和非高速应用,在封装成本和可靠性方面有成熟优势,常见于传统和低成本封装应用(如消费类电子产品、汽车电子和传感器等)。

-

六、封胶

(一)封胶目的与灌胶流程

-

目的作用

-

将 IC 晶片与外界隔绝,避免内部金线以及晶片被破坏,防止腐蚀,避免信号破坏,同时为芯片提供能够手持之形体。

-

-

灌胶流程

-

焊线完成的导线架或基板置放于框架上预热,然后放于压模机内的封装膜上,模机压下封闭上下模穴,将半融化的树脂挤入模具中,待树脂充填完成并硬化后,开模取出整排相连的成品。

-

(二)封胶材料分类及特性

-

材料分类

-

封胶材料主要有陶瓷、金属、塑胶三类,不同材料依其热传递及电性特性,通过改变化学组成调整性质,配合不同制程技术,用于不同功能需求的 IC 元件封装。

-

-

各类材料特性

-

陶瓷封装:优点是耐湿性好,不易产生微裂现象;热冲击和温度循环实验后无损伤,机械强度高;热膨胀系数小,热导率高;绝缘性和气密性好,芯片和电路不受周围环境影响,避光性好,能满足高密封和光学相关产品要求。缺点是脆性较高,易受应力破坏;制程温度高、成本高,仅见于高可靠度需求的 IC 封装中。

-

金属封装:采用金属作为壳体或底座,在分立式元件与高功率元件封装中应用广泛,尤其在高可靠度需求的军用电子封装元件中。优点是具有优良的水分子阻绝能力、热传导特性、电遮蔽性。缺点是化学稳定性差,不耐酸碱性,金属离子易析出。

-

塑胶封装:一般以热固性材料为主(如环氧类、酪酸类、聚酷类和有机珪类)。优点是原料纯度高、粘度低、杂质少;低吸水率、耐热性能好、热导率较高;低应力、热膨胀系数匹配;易加工成型、原料浪费少、阻燃性能好;环保性能好、无毒无污染,能提供小型化封装、低成本、制程简单、适合自动化生产。缺点是散热性、耐热性、密封性与可靠度逊于陶瓷和金属封装(但随着材料和制程技术改善,可靠度大幅提升)。塑胶封装制程各步骤互相关联,设计时需整体考量对结构与可靠度的影响。

-

七、剪切 / 成型

(一)批量封装流程与剪切成型目的

-

封装流程

-

切割过的晶粒整齐排放,机器自动贴装到导线架上,进行联线键合,封胶固化后,将多余残胶去除(Deflash),经过电镀增加外引脚导电性及抗氧化性,然后进行剪切成型工作。

-

-

目的作用

-

剪切成型可按照需求改变引脚形状,去除多余部分,使芯片符合特定规格要求。同时加工式剪切可提高生产效率和降低制造成本,顺送式加工式剪切适用于中小规模生产和成批生产,灵活性和适应性强,可处理多种不同型号和尺寸芯片。

-

(二)引脚共面性问题

-

问题描述

-

引脚共面性问题表现为引脚不在同一平面上,可能出现海鸥形引脚或直播形引脚等非共面情况。引发因素包括工艺过程中的不恰当处理、塑封料在继续固化收缩、成形过程中产生的热收缩应力、塑封料和引线架材料之间的热膨胀系数失配等。

-

八、印字 & 检测

(一)印字目的与方式

-

目的意义

-

印字是为了给予 IC 元件适当的辨识,提供可追溯生产的记号。

-

-

印字方式

-

包括捺印式、转印式、镭射刻印等。

-

(二)检测封装缺陷与项目

-

检测缺陷类型

-

封装缺陷有引线变形、底座偏移、翘曲、芯片破裂、分层、粘接不良、空洞、不均匀封装、毛边、外来颗粒、不完全固化等。

-

-

检测项目内容

-

利用 X 射线实时成像检测设备对封装后的产品进行质量检查,检测项目包括外引脚的平整性、共面度、胶距、印字是否清晰、胶体外观是否有损伤,以及其他功能与产品可靠度检测,以确保产品质量与制程良率。

-

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?