W25Q128数据手册翻译(3)

- 8 指令

- 8.1 器件ID和指令集表

- 8.1.1 制造商和器件标识符

- 8.1.2 指令集表1(标准/双线/四线SPI指令)

- 8.1.3 指令集表2(标准/双线/四线SPI指令)

- 8.1.4 指令集表3(QPI指令)

- 8.2 指令描述

- 8.2.1 写使能(0x06)

- 8.2.2 易失性状态寄存器写使能(0x50)

- 8.2.3 写禁止(0x04)

- 8.2.4 读状态寄存器1(0x05),读状态寄存器2(0x35),读状态寄存器3(0x15)

- 8.2.5 写状态寄存器1(0x01),写状态寄存器2(0x31),写状态寄存器3(0x11)指令

- 8.2.6 读数据(0x03)

- 8.2.7 快速读(0x0B)

- 8.2.8 双线输出快速读(0x3B)

- 8.2.9 四线输出快速读(0x6B)

- 8.2.10 双IO快速读(0xBB)

- 8.2.11 四IO快速读(0xEB)

- 8.2.12 四IO字读取(0xE7)

- 8.2.13 四IO八字读取(0xE3)

- 8.2.14 设置回环突发(0x77)

- 8.2.15 页编程(0x02)

- 8.2.16 四输入页编程(0x32)

- 8.2.17 扇区擦除(0x20)

- 8.2.18 32KB块擦除(0x52)

- 8.2.19 64KB块擦除指令(0xD8)

- 8.2.20 整片擦除(0xC7/0x60)

- 8.2.21 擦除/编程挂起(0x75)

- 8.2.22 擦除/编程恢复(0x7A)

- 8.2.23 下电(0xB9)

- 8.2.24 释放下电/器件ID(0xAB)

- 8.2.25 读制造商/器件ID(0x90)

- 8.2.26 双IO读制造商/器件ID(0x92)

- 8.2.27 四IO读制造商/器件ID(0x94)

- 8.2.28 读唯一ID序列号(0x4B)

- 8.2.29 读JEDEC ID(0x9F)

- 8.2.30 读SFDP寄存器(0x5A)

- 8.2.31 擦除安全寄存器(0x44)

- 8.2.32 编程安全寄存器(0x42)

- 8.2.33 读安全寄存器(0x48)

- 8.2.34 设置读参数(0xC0)

- 8.2.35 回环突发读(0x0C)

- 8.2.36 进入QPI模式(0x38)

- 8.2.37 离开QPI模式(0xFF)

- 8.2.38 独立块/扇区锁定(0x36)

- 8.2.39 独立块/扇区解锁(0x39)

- 8.2.40 读块/扇区锁定状态(0x3D)

- 8.2.41 全局块/扇区锁定(0x7E)

- 8.2.42 全局块/扇区解锁(0x98)

- 8.2.43 允许复位(0x66)和复位器件(0x99)

- 9 AC特性

8 指令

W25Q128FV使用标准/双线/四线SPI的指令集,一共包含45条基本指令,这些指令都通过SPI进行控制(参见指令集表1-2)。指令在片选信号/CS的下降沿发出,通过DI信号线传输的第一个字节为指令码。DI信号线上的信号在时钟的上升沿采样,MSb先传输。

QPI指令集则包含32条基本指令,同样通过SPI信号线的这些信号进行控制(参见表3)。指令同样需要在片选信号/CS的下降沿之后发出。通过IO[3:0]传输的第一个字节是指令码。四个IO线上的信号在CLK的上升沿采样,MSb先发送。所有的QPI指令,地址,数据和无效字节都使用四个IO线同时传输,每个字节消耗2个时钟周期。

有些指令的长度短至单个字节,有些则包含多个字节,首个字节的指令码之后跟着地址字节,数据字节,或者无效字节(不关心),或者是这些的组合。/CS信号的上升沿完成指令。各个指令和时钟相关的时序图参考图5到图57。所有的读指令可以在任意的时钟位置后完成。但是,所有写,编程或者擦除指令必须在字节边界之后完成(/CS必须在一个完整的8位传输之后置高),否则指令将会被忽略。该特性保护器件,避免不经意的写入。此外,在存储器正在编程或者擦除时,或者当正在写入状态寄存器时,除了读状态寄存器之外的所有指令都会被忽略,直到编程或者擦除循环完成。

8.1 器件ID和指令集表

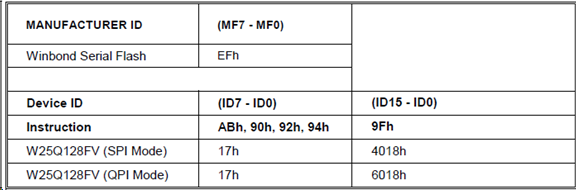

8.1.1 制造商和器件标识符

8.1.2 指令集表1(标准/双线/四线SPI指令)

8.1.3 指令集表2(标准/双线/四线SPI指令)

8.1.4 指令集表3(QPI指令)

8.2 指令描述

8.2.1 写使能(0x06)

写使能指令(图5)用来设置WEL位。在每次进行页编程,四页编程,扇区擦除,块擦除,整片擦除,写状态寄存器或者擦除/编程安全寄存器指令之前,必须先设置WEL位。写使能指令发出前先设置/CS为低电平,将指令码0x06在CLK的上升沿移入DI信号线,然后驱动/CS为高电平。

图5 SPI或者QPI模式下的写使能指令

8.2.2 易失性状态寄存器写使能(0x50)

易失性状态寄存器位已经在7.1小结进行了描述,这些非易失性状态寄存器位也可以按照易失性位写入。这提高了系统配置和存储器保护机制的灵活性,避免因频繁写入非易失性状态位从而降低这些位的寿命。当需要写易失性数据到状态寄存器的相关位时,必须在写状态寄存器指令(0x01)之前先发出易失性状态寄存器写使能(0x50)指令。该指令不会设置WEL位,因为仅用来控制写状态寄存器指令去写易失性状态位而已。

图6 SPI或者QPI模式下的易失性状态寄存器写使能指令

8.2.3 写禁止(0x04)

写禁止指令(图7)复位WEL位。该指令发出时先拉低/CS位,然后将指令码0x04移位入DI信号线,然后驱动/CS为高电平。注意WEL位在上电之后,或者在写状态寄存器指令、擦除/编程安全寄存器指令、页编程指令、四页编程指令、扇区擦除指令、块擦除指令、整片擦除指令和复位指令之后自动复位为0。

图7 SPI或者QPI模式下的写禁止指令

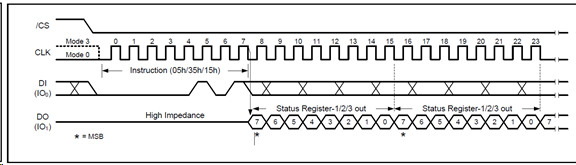

8.2.4 读状态寄存器1(0x05),读状态寄存器2(0x35),读状态寄存器3(0x15)

读状态寄存器指令允许每次读出一个8位的状态寄存器。该指令首先需要设置/CS为低电平,然后在CLK的上升沿向DI信号线输入0x05(状态寄存器1),或者0x35(状态寄存器2),或者0x15(状态寄存器3)。然后,相应的状态寄存器在每个CLK的下降沿出现在DO引脚上,MSb先输出,参考图8。查询7.1节以获取状态寄存器的描述。

读状态寄存器指令可以在任何时刻使用,即使编程、擦除或者写状态寄存器等操作正在进行。这使得可以通过查询BUSY位来判断前述这些指令是否完成了。状态寄存器可以连续读,参考图8。状态寄存器读取操作通过拉高/CS引脚来结束操作。

图8a SPI模式下读状态寄存器指令

图8b QPI模式下读状态寄存器指令

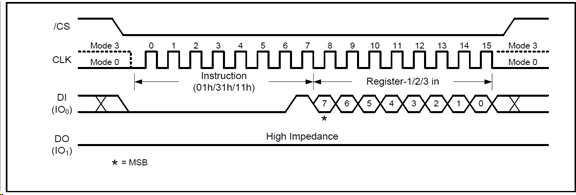

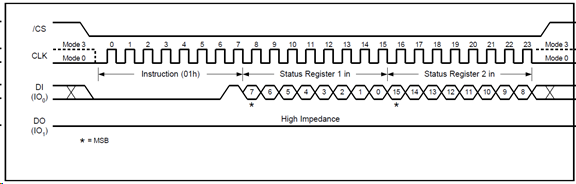

8.2.5 写状态寄存器1(0x01),写状态寄存器2(0x31),写状态寄存器3(0x11)指令

写状态寄存器指令允许一些状态寄存器位被写入。可写入的状态寄存器位包括:SPR0,SEC,TB,BP[2:0](这几个在状态寄存器1中),CMP,LB[3:1],QE,SRP1(这几个在状态寄存器2中),HOLD/RST,DRV1,DRV0,WPS和ADP(这几个在状态寄存器3中)。所有其他的状态寄存器位是只读的,本指令对这些位没有影响。LB[3:1]是非易失性的一次性编程位,一旦被设置为1,则无法再改为0。

在写非易失性状态位之前,需要先发出写使能指令(0x06)以使得器件可以接收写命令(也就是WEL必须等于1)。写使能指令完成之后,拉低/CS信号,发送0x01/0x31/0x11到器件来执行本指令。可参见图9a和图9b。

如果想以易失性方式写这些位,则此处描述的指令发出之前还需要先发出易失性状态寄存器写使能指令(0x50)(状态寄存器中的WEL仍然为0)。但是,SRP1位和LB[3:1]位在此种情况下也无法从1改成0,因为这些内容是一次性编程保护的。在掉电之后,或者软件/硬件复位之后,易失性状态寄存器位将会丢失,但非易失性写入的内容将会被保存,不会丢失。

如果进行非易失性状态寄存器写入(0x06指令跟上0x01/0x31/0x11指令),在/CS信号拉高从而结束指令后,该写入循环还需要持续一段时间t_W(参见AC特性)。当写状态寄存器循环正在进行时,仍然可以通过读状态寄存器指令来获取BUSY位。如果BUSY位为1表明该循环仍在进行,如果位0则表示该循环结束,可接受其他指令。在写状态寄存器循环结束后,注意WEL位将会清0。

在易失性状态寄存器写操作(0x50指令后跟上0x01/0x31/0x11指令),在/CS拉高之后,状态寄存器会在t_SHSL2(参见AC特性)时间内刷新为新的值。BUSY位在该时间之内也仍然是0。

写状态寄存器指令既可以在SPI模式下使用也可以在QPI模式下使用。但是在QPI模式下,QE位不能写入,因为QE=1是器件进入QPI模式和维持QPI操作的必要条件。

参考7.1节获取状态寄存器的描述。

图9a SPI模式下的写状态寄存器1/2/3

图9b QPI模式下的写状态寄存器1/2/3

图9b QPI模式下的写状态寄存器1/2/3

W25Q128FV还向前支持Winbond公司之前几代的串行Flash存储器,这些存储器的状态寄存器1/2可以用单个的写状态寄存器1(0x01)指令一次性写入。为了完成写状态寄存器1&2指令,/CS引脚必须在发出指令之后的16个周期后才能置高,参考图9c和图9d。如果/CS在指令码发出之后第八个周期置高,则写状态寄存器1(01)指令仅仅编程状态寄存器1,状态寄存器2不受影响(前代芯片则会清除CMP和QE位)。

图9c SPI模式下的写状态寄存器1/2指令

图9d QPI模式下的写状态寄存器1/2指令

8.2.6 读数据(0x03)

读数据指令允许从器件中顺序地读出一至多个字节。指令使用时先拉低/CS,然后将指令码0x03连同24位地址(A23~A0)通过DI引脚传输到器件中。指令码和地址位在CLK的上升沿采样。在地址被器件接收到之后,地址所寻址的数据将会在每个时钟的下降沿在DO引脚上给出,MSb先发送。在内部,地址会自动递增到下一个字节位置,从而实现连续的数据流。这意味着整片的存储器可以用单个读指令读出,只要时钟足够多。该指令通过驱动/CS为高电平来结束。

读数据指令序列参考图14.如果读数据指令发出时,器件正在执行擦除、编程或者写循环(BUSY=1),则读数据指令会被忽略,当前器件正在进行的操作不会受到影响。读数据指令允许的时钟速率从直流到最大fR(参考AC电气特性)。

读数据(0x03)指令仅在标准SPI模式下支持。

图14 读数据指令(仅标准SPI模式下支持)

8.2.7 快速读(0x0B)

快速读指令类似于读数据指令,区别在于该指令可以运行在最高FR频率(参考AC电气特性)。这通过在24位地址之后插入一组8个无效时钟周期(一个无效字节)来实现,参考图16。无效时钟使得器件内部的线路有额外的时间来建立初始地址。在无效时钟时,出现在DO引脚上的数据不关心。

图16a 快速读指令(SPI模式)

QPI模式下的快速读(0x0B)指令

快速读指令同样可应用在QPI模式下。当QPI模式使能,需要插入的无效时钟数,通过设置读参数(0xC0)指令来设置,这个参数可以根据对最大读取速度和最小数据延时之间的不同需求,在一个较宽的范围内选择。取决于读参数位P[5:4]的设置,无效周期数可以设置为2,4,6或者8。上电或者复位后需要插入的无效周期数缺省值是2。

图16b 快速读指令(QPI模式)

8.2.8 双线输出快速读(0x3B)

双线输出快速读(0x3B)指令类似于标准快速读(0x0B)指令,区别在于本指令使用双引脚输出:IO0和IO1。这使得数据传输速率相比于标准SPI器件可以提高1倍。本指令对于需要将代码从Flash拷贝到RAM之类的应用是理想的选择。

类似于快速读指令,双线输出快速读指令可以运行在最大可能速率FR(参考AC电气特性)上。无效时钟允许器件的内部电路有额外的时间来建立初始地址。在无效时钟周期时,输入数据不关心。但是,必须确保IO0引脚在第一个数据输出时钟的下降沿到来之前已经是高阻态。

图18 双线输出快速读指令(仅SPI模式下支持)

8.2.9 四线输出快速读(0x6B)

四线输出快速读(0x6B)指令类似于双线输出快速读(0x3B)指令,区别在于数据输出出现在四个数据引脚IO0,IO1,IO2,IO3上。在使用该指令之前,状态寄存器中的QE位必须设置为1。四线输出快速读指令使得器件可以提供相比于标准SPI多达4倍的数据速率。

四线输出快速读指令可以运行在最大可能速率FR(参考AC电气特性)上。该特点通过在地址发送完成到数据输出之间插入8个无效时钟周期来实现,参考图20。无效时钟允许器件内部电路有额外的时间来建立初始地址。无效时钟周期期间的输入数据,器件并不关心。但是,在首个数据输出时钟的下降沿之前,IO引脚必须已经是高阻态。

图20 四线输出快速读指令(仅SPI模式下支持)

8.2.10 双IO快速读(0xBB)

双IO快速读(0xBB)指令允许提高随机访问时的访问效率,这通过使用2个IO线,IO0和IO1来实现。这有些类似于双输出快速读(0x3B),但区别在于24位地址传输时,每个周期可以传输2位。这降低了指令开销,从而允许一些应用中的XIP需求。

双IO快速读连同“连续读模式”

双IO快速读指令可以更进一步地降低指令开销,这一点可以通过设置“连续读模式”位(M70)来实现,这些位在24位地址传输之后,参考图22a。高4位(M74)控制着下一次双IO快速读指令的长度,指示下次指令是否包含第一个字节的指令码。低4位(M3~0)不关心。但是,在第一个数据传输时钟的下降沿之前这些IO必须已经是高阻态。

如果“连续读模式”位M54=(1,0),则下一次双IO快速读指令(也就是本次/CS拉高然后再拉低)就不再需要1字节长度的指令码0xBB,参考图22b。这样就从指令序列中减少了八个时钟周期,从而在/CS拉低后,立即输入读取地址。反之如果M54不等于(1,0),则下一次指令仍旧需要首个字节的指令码,从而成为普通操作。建议下条指令时,在IO0上输入0xFFFF(16个周期),从而确保M4=1,然后器件进入正常的操作模式。

图22a 双IO快速读指令(首次指令,或者上次指令M5~4!=10,仅SPI模式下支持)

图22b 双IO快速读指令(上次指令M5~4=10,仅SPI模式下支持)

8.2.11 四IO快速读(0xEB)

四IO快速读(0xEB)类似于双IO快速读(0xBB)指令,区别在于本指令使用4条IO线,IO0、IO1、IO2和IO3来传输地址和数据,以及需在数据输出之前插入额外的4个无效周期。这降低了指令开销,从而允许更高速的随机访问或者XIP。在使用四IO快速读之前,QE位必须使能。

四IO快速读连同“连续读模式”

四IO快速读指令可以更进一步地降低指令开销,这一点可以通过设置“连续读模式”位(M70)来实现,这些位在24位地址传输之后,参考图24a。高4位(M74)控制着下一次四IO快速读指令的长度,指示下次指令是否包含第一个字节指令码。低4位(M3~0)不关心。但是,在第一个数据传输时钟的下降沿之前这些IO必须已经是高阻态。

如果“连续读模式”位M54=(1,0),则下一次四IO快速读指令(也就是本次/CS拉高然后再拉低)就不再需要1字节长度的指令码0xEB,参考图24b。这样就从指令序列中减少了八个时钟周期,从而在/CS拉低后,立即输入读取地址。反之如果M54不等于(1,0),则下一次指令仍旧需要首个字节的指令码,从而成为普通操作。建议下条指令时,在IO0上输入0xFF(8个周期),从而确保M4=1,然后器件进入正常的操作模式。

图24a 四IO快速读指令(首次指令,或者上次指令M5~4!=10,仅SPI模式下支持)

图24b 四IO快速读指令(上次指令M5~4=10,仅SPI模式下支持)

标准SPI模式下四IO快速读,连同“8/16/32/64字节回环”

在四IO快速读指令(0xEB)之前,还可以先发送“设置回环突发”(0x77)指令,从而使得本指令的读取访问,总是在一个页的指定区域之内循环。“设置回环突发”(0x77)指令可以打开或者关闭接下来的四IO快速读指令的回环读取功能。当该功能打开时,访问的数据会被限制在一个256字节页中的8/16/32/64字节段落内。读取操作从指令指定的地址开始,一旦内部自动累加的地址触及到8/16/32/64字节段落的边界,输出将会自动回到段落的起始位置,除非/CS信号拉高以终止访问。

该功能使得使用Cache的应用程序可以快速地取得关键地址,然后将cache使用固定长度的数据(8/16/32/64)填充,无需发出多次读指令。

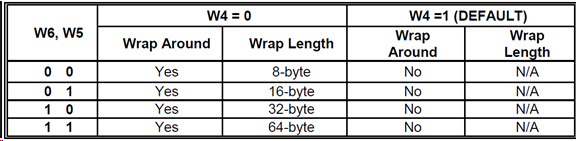

“设置回环突发”指令设置3位“回环位”,W6-4。W4位用来使能或者禁止回环访问功能,W6-5用来指定位于一个页中的回环长度。具体可参考8.2.24节。

QPI模式下的四IO快速读

四IO快速读在QPI模式下同样支持,见图19c。当QPI模式使能时,无效时钟周期数通过设置读参数(0xC0)指令来设置,具体设置多少,取决于应用对最高访问速度和最小的访问延时的考虑。通过读参数位P[5:4]的设置,这个无效时钟周期数可以是2,4,6,8。上电或者复位后该值缺省是2。在QPI模式下,“连续读模式”位M7-0仍然建议作为无效时钟周期。缺省设置下,“连续读模式”之后紧接着就是数据。

“连续读模式”特性在QPI模式下使用四IO快速读指令时仍然有效。请参考前页描述。

“回环”特性在QPI模式下使用四IO快速读指令时无效。如果一个读操作需要读取固定长度的数据并且可以回环读,则必须使用专用的“回环突发读”(0x0C)指令。参考8.2.45。

图24c 四IO快速读指令(首次读,或者上次读M5-4!=10,QPI模式下)

8.2.12 四IO字读取(0xE7)

四IO字读取(0xE7)指令类似于四IO快速读指令(0xEB),区别在于本指令发出的地址的最低位(A0)必须为0,并且在数据输出之前仅需要2个无效时钟周期。四IO模式在使用高速随机访问的代码XIP应用中可以较大地降低指令开销。使用本指令之前必须设置QE位。

四IO字读取连同“连续读模式”

在地址之后跟上“连续读模式”位M7-0,可以进一步降低四IO字读取的指令开销,见图26a。高位(M7-4)控制着下一条四IO快速读取指令的长度,通过指示是否包含首字节的指令码来表示。低位(M3-0)不关心。但是,在首个数据输出时钟的下降沿之前,IO引脚必须为高阻态。

如果“连续读模式”位M5-4=(1,0),则下一次的四IO快速读(也就是本次/CS置高再置低)不再需要0xE7的指令码,如图26b。这样,指令序列将会减少8个周期,/CS拉低后立刻传输地址。如果M5-4不等于(1,0),则下一次指令仍然需要首个指令码,也就是正常的操作。建议下次指令时在IO0上输入0xFF(8周期),从而确保M4=1,使得器件进入正常操作。

图26a 四IO字读取指令(首次读取或者前次读取M5-4!=10,仅SPI模式)

图26b 四IO字读取指令(上次读取时M5-4=10,仅SPI模式)

标准SPI模式下四IO字读取,连同“8/16/32/64字节回环”

在四IO字读取指令(0xE7)之前,还可以先发送“设置回环突发”(0x77)指令,从而使得本指令的读取访问,总是在一个页的指定区域之内循环。“设置回环突发”(0x77)指令可以打开或者关闭接下来的0xE7命令的回环读功能。当该功能打开时,访问的数据会被限制在一个256字节页中的8/16/32/64字节段落内。读取操作从指令指定的地址开始,一旦内部自动累加的地址触及到8/16/32/64字节段落的边界,输出将会自动回到段落的起始位置,除非/CS信号拉高以终止访问。

该功能使得使用Cache的应用程序可以快速地取得关键地址,然后将cache使用固定长度的数据(8/16/32/64)填充,无需发出多次读指令。

“设置回环突发”指令设置3位“回环位”,W6-4。W4位用来使能或者禁止回环访问功能,W6-5用来指定位于一个页中的回环长度。具体可参考8.2.24节。

8.2.13 四IO八字读取(0xE3)

四IO八字读(0xE3)指令类似于四IO快速读(0xEB)指令,区别在于传输地址的低四位(A0,A1,A2,A3)必须等于0。作为结果,此种传输不再需要无效时钟,从而在高速随机访问或者代码XIP应用场景中降低指令开销。在发出四IO八字读取指令之前,状态寄存器2中的QE位必须为1。

四IO八字读取连同“连续读模式”

四IO八字读取指令可以更进一步地降低指令开销,这通过设置地址位(A23-0)之后的“连续读模式”位(M7-0)来实现,参考图27a。高位(M7-4)通过控制下一次四IO八字读指令是否包含首个字节的指令码,从而控制下次指令的长度。低位(M3-0)不关心。但是,在首个传输数据位对应的时钟的下降沿到来之前,IO引脚必须为高阻态。

如果“连续读模式”位M5-4=(1,0),则下一次四IO快速读指令(也就是本次/CS拉高之后重新拉低的指令)就不再需要0xE3指令码,参考图27b。这样就从下一次指令序列中减少了8个周期,下一次指令不必发送指令码,直接发送地址信息。如果“连续读模式”为M5-4不等于(1,0),则下一次指令仍然需要首个字节的指令码,从而成为普通指令操作。建议在下次指令时在IO0上传输0xFF(8时钟周期),确保M4=1,从而使得器件进入正常操作模式。

图27a 四IO八字读指令(初始指令,或者上次指令M5-4!=10,仅SPI模式)

图27b 四IO八字读指令(上次指令M5-4=10,仅SPI模式)

8.2.14 设置回环突发(0x77)

在标准SPI模式下,设置回环突发(0x77)指令用来和指令“四IO快速读”与“四IO字读取”指令联合使用,从而实现对一个256字节的页内访问固定长度的8/16/32/64字节段落。合适的应用可以妥善利用此特性从而提高系统代码执行性能。

类似于四IO指令,设置回环突发指令通过驱动/CS引脚为低电平来开启,然后发送指令码0x77,之后跟上24个无效位,最后跟上8位的“回环位”,W7-0。该指令序列参考图28。回环位W7和低位的W3-0不使用。

一旦W6-4通过设置回环突发指令设置了,所有后续的“四IO快速读”和“四IO字读”指令将会根据W6-4的设置来访问某个页内的8/16/32/64字节固定长度段落。如果需要禁止这种功能从而返回正常的读操作,需要重新发送一次设置回环突发指令,将W4设置为1。W4位在上电后或者软件/硬件复位之后的缺省值是1。

在QPI模式下,则应使用“回环突发读(0x0C)”指令来执行具有“环回”功能的读取操作。回环长度通过W5-4来设置,其还可以通过“设置读参数(0xC0)”指令来重新配置。参考8.2.44和8.2.45。

图28 设置回环突发指令(仅SPI模式)

8.2.15 页编程(0x02)

页编程指令允许对一个事先已经擦除(0xFF)过的存储器区域进行数据编程,编程的大小可以从1字节到256字节。在器件可接收页编程指令之前,必须先给器件写使能指令(从而设置状态寄存器WEL=1)。该指令通过拉低/CS来启动,然后通过DI引脚发送页编程指令码(0x02)连同24位地址(A23-A0),以及至少1字节数据到器件。在数据传输的整个过程中/CS引脚必须为低电平。页编程指令序列参考图29。

如果整个的256字节页需要编程,则地址的低位(最低字节,8个最低位)应该设置为0。如果该最低字节非0,并且之后传输的数据数量超过了本页的剩余字节数,则地址会自动回到页的开始。在某些情况下,少于256字节(也就是页的一部分)需要被编程,但同时不能影响本页中其他的数据。这样做的一个方法是传输数据的时钟数不能超过本页剩余的字节数。如果超过256字节传输到器件,则地址一定会重新回到页的开始,而之前被保存的数据会被覆盖。

连同写和擦除指令,/CS引脚必须在时钟信号的8的倍数位后拉高。如果没有这么做,页编程指令不会执行。/CS拉高之后,内部自同步的页编程指令将会持续t_PP(参考AC特性)时间。在整个页编程过程中,读状态寄存器指令仍然有效,可以通过该指令来获取BUSY位。如果页编程指令仍在进行则BUSY为1;如果BUSY位为0,则器件已经完成了页编程指令,并且可以接受新的指令。页编程循环结束之后,状态寄存器中的WEL会重新清为0。如果页编程指令序列中的地址所指定的存储区通过块保护(CMP,SEC,TB,BP2,BP1,BP0)位或者独立块/扇区保护位进行了保护,则页编程指令不会执行。

图29a 页编程指令(SPI模式)

图29b 页编程指令(QPI模式)

8.2.16 四输入页编程(0x32)

四输入页编程允许使用4个IO引脚:IO0,IO1,IO2,IO3来对之前已经擦除过的存储器区域(0xFF)进行编程。四输入页编程对于进行PROM编程或者某些时钟速度<5MHz的慢速时钟的应用而言可以提高效率。如果系统的时钟速率比较高,则此种模式不会有多大收益,因为器件内部的页编程时间要远远大于将数据通过接口传输到器件内部的时间。

如果需要使用四输入页编程,QE位必须设置为1。在器件可以接受四输入页编程之前,还必须先给出写使能指令从而使得状态寄存器中的WEL=1。本指令通过拉低/CS发起,然后通过器件的IO输入指令码0x32,24位地址(A23-A0),以及至少1个数据字节。在整个过程中/CS引脚必须保持低电平。其他的四输入页编程的注意事项和标准页编程一致。四输入页编程指令可参见图30。

图30 四输入页编程指令(仅SPI模式)

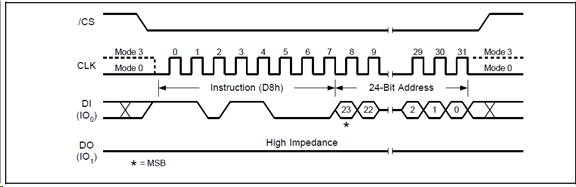

8.2.17 扇区擦除(0x20)

扇区擦除指令将存储器指定扇区(4KB大小)内的内容全部擦除为1(0xFF)。发出扇区擦除指令之前,必须先发出写使能指令,以将状态寄存器中的WEL位设置为1。该指令通过拉低/CS开始,然后向器件输入指令码0x20,后面跟随24位扇区地址(A23-A0)。扇区擦除指令序列参考图31a和31b。

/CS引脚必须在整数字节(8倍数时钟)之后拉高,以确保最后一个字节被锁定。如果没有这么做,则扇区擦除指令将不会执行。在/CS拉高之后,器件内部自同步的指令执行将会持续t_SE(参考AC特性)时间。扇区擦除循环正在进行时,读状态寄存器指令仍可用,此时应该用此指令获取状态寄存器中的BUSY位。如果扇区擦除仍在进行,则BUSY位会为1;如果扇区擦除已经结束并且器件可以接受新的指令,则BUSY位为0。如果地址所指定的存储区收到块保护位(CMP,SEC,TB,BP2,BP1,BP0)位的保护或者受到独立块/扇区锁定位的保护,则擦除指令不会执行。

图31a 扇区擦除指令(SPI模式)

图31b 扇区擦除指令(QPI模式)

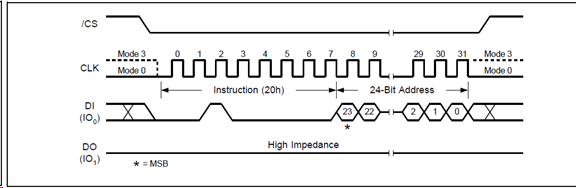

8.2.18 32KB块擦除(0x52)

块擦除指令用来将指定的32KB的数据块内的所有内容擦除为全1(0xFF)。应用此指令之前必须先执行写使能指令,以使得状态寄存器中的WEL位为1。块擦除指令通过将/CS引脚拉低来发起,然后通过DI引脚向器件输入指令码0x52,其后跟随24位块地址。块擦除指令序列可参考图32a和图32b。

/CS引脚必须在整字节(8位时钟的整数倍)之后被拉高,这样才能确保最后一个字节的内容被锁定。如果没有这么做,块擦除指令将不会被执行。在/CS驱动为高电平之后,器件内部的自同步的块擦除指令将会持续t_BE1(参见AC特性)时间。在块擦除的过程中,应该使用读状态寄存器指令以获得BUSY位的状态。如果BUSY为1说明块擦除仍在进行中;而块擦除循环结束,器件可以接收新的指令后,BUSY位被清0。块擦除指令携带的地址所寻址的空间如果被块保护(CMP,SEC,TB,BP2,BP1,BP0)位所保护,或者位独立块/扇区锁定位所保护,则块擦除指令将不会执行。

图32a 32KB块擦除指令(SPI模式)

图32b 32KB块擦除指令(QPI模式)

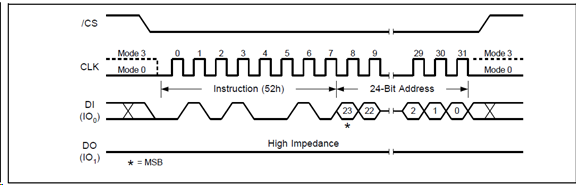

8.2.19 64KB块擦除指令(0xD8)

块擦除指令用来将指定的64KB的数据块内的所有内容擦除为全1(0xFF)。应用此指令之前必须先执行写使能指令,以使得状态寄存器中的WEL位为1。块擦除指令通过将/CS引脚拉低来发起,然后通过DI引脚向器件输入指令码0xD8,其后跟随24位块地址(A23-A0)。块擦除指令序列可参考图33a和图33b。

/CS引脚必须在整字节(8位时钟的整数倍)之后被拉高,这样才能确保最后一个字节的内容被锁定。如果没有这么做,块擦除指令将不会被执行。在/CS驱动为高电平之后,器件内部的自同步的块擦除指令将会持续t_BE1(参见AC特性)时间。在块擦除的过程中,应该使用读状态寄存器指令以获得BUSY位的状态。如果BUSY为1说明块擦除仍在进行中;而块擦除循环结束,器件可以接收新的指令后,BUSY位被清0。块擦除指令携带的地址所寻址的空间如果被块保护(CMP,SEC,TB,BP2,BP1,BP0)位所保护,或者位独立块/扇区锁定位所保护,则块擦除指令将不会执行。

图33a 64KB块擦除指令(SPI模式) 图33b 64KB块擦除指令(QPI模式)

图33b 64KB块擦除指令(QPI模式)

8.2.20 整片擦除(0xC7/0x60)

整片擦除指令可以将整个器件的所有存储阵列全部擦除为1(0xFF)。在此之前需要先给出写使能指令,从而使得状态寄存器中的WEL为1。块擦除指令通过将/CS引脚拉低来发起,然后通过DI引脚向器件输入指令码0xC7或0x60。整片擦除指令序列参见图34。

/CS引脚必须在整字节(8位时钟的整数倍)之后被拉高。如果没有这么做,整片擦除指令将不会被执行。在/CS驱动为高电平之后,器件内部的自同步的块擦除指令将会持续t_CE(参见AC特性)时间。在整片擦除的过程中,应该使用读状态寄存器指令以获得BUSY位的状态。如果BUSY为1说明整片擦除仍在进行中;而整片擦除循环结束,器件可以接收新的指令后,BUSY位被清0。如果存在任何被块保护(CMP,SEC,TB,BP2,BP1,BP0)位所保护,或者被独立块/扇区锁定位保护的存储空间,整片擦除指令将不会执行。

图34 整片擦除指令(左为SPI模式,右为QPI模式)

8.2.21 擦除/编程挂起(0x75)

擦除/编程挂起指令0x75,允许系统中断一个扇区或者块的擦除操作,或者中断一个页的编程操作,此后,系统可以从芯片中读取数据,或者对其他的扇区或者块进行编程/擦除。擦除/编程指令序列参见图35a和35b。

写状态寄存器指令(0x01)和擦除指令(0x20,0x52,0xD8,0xC7,0x60,0x44)在擦除挂起期间不能再使用。擦除挂起只能够应用于扇区擦除和块擦除操作。如果在整片擦除过程中,擦除挂起指令会被忽略。写状态寄存器指令(0x01,0x31,0x11)和编程指令(0x02,0x32,0x42)在编程挂起期间不能使用。编程挂起指令只能够在页编程或者四输入页编程操作中使用。

{擦除挂起后可以编程,编程挂起后可以擦除;擦除挂起后不能擦除,编程挂起后不能再编程}

擦除/编程挂起指令0x75仅在正进行扇区或者块擦除,或者正在进行页编程,并且状态寄存器的SUS=0且BUSY=1的情况下使用。如果SUS位为1,或者BUSY位为0,挂起指令将被忽略。挂起操作需要最大t_SUS(参见AC特性)时间来执行。在t_SUS时间之后,BUSY位将会从1清0,而SUS位则将会从0变为1。如果刚刚一次挂起操作被恢复,则要求在上次的恢复指令0x7A之后最短t_SUS时间之内,不能再次发出挂起指令0x75。

发生在挂起期间的意料之外的断电行为,将会复位器件,释放挂起状态。状态寄存器中的SUS位同样会被清为0。被挂起操作的页/扇区/块中的数据可能已经被破坏。因此建议用户从系统设计角度考虑引入一些技术手段,保护编程/擦除挂起期间的数据完整性。

图35a 擦除/编程挂起指令(SPI模式)

图35b 擦除/编程挂起指令(QPI模式)

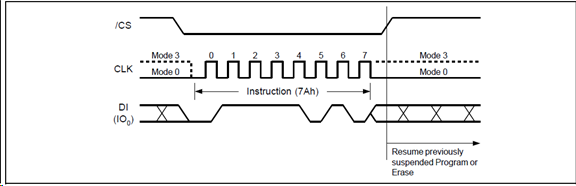

8.2.22 擦除/编程恢复(0x7A)

在使用擦除/编程挂起指令来挂起扇区/块擦除或者页编程操作后,必须使用擦除/编程恢复(0x7A)指令恢复操作。仅在状态寄存器中SUS位为1并且BUSY位为0的情况下,这种操作才会被接收。指令发出之后,SUS位会立刻从1变为0,而BUSY位会在200nS之内从0编程1,扇区/块擦除,或者页编程将会继续完成。如果SUS位为0,或者BUSY位为1,则恢复指令0x7A将会被器件忽略。擦除/编程恢复指令序列参见图36a和图36b。

如果之前的擦除/编程挂起操作被不期望的掉电行为中断掉,则本恢复指令会被忽略。另外在一次恢复指令发出之后的t_SUS时间之内,不能够再次给出擦除/编程挂起指令。

图36a 擦除/编程恢复指令(SPI模式)

图36b 擦除/编程恢复指令(QPI模式)

8.2.23 下电(0xB9)

虽然正常操作时的待机电流已经很低,但是仍然可以通过下电指令更进一步降低待机电流。极低的功率消耗使得下电指令特别适用于电池供电的应用(参见AC特性中的ICC1和ICC2)。该指令通过拉低/CS发起,然后向器件发送指令码0xB9,参见图37和38。

/CS引脚的拉高操作必须在第八个时钟位之后进行。如果没有这么做,下电指令不会被执行。在/CS拉高之后,将会在t_DP(参见AC特性)之后进入下电模式。在下电模式下,仅有释放下电/器件ID(0xAB)指令会被识别,该指令恢复器件为正常操作状态。所有其他指令都会被忽略。这些指令包括读状态寄存器指令,该指令在正常模式下的任何时刻都是有效的。在下电模式下,忽略除1条指令外的其他的所有指令,有利于最大程度地进行写保护。器件上电后的正常模式下,待机电流是ICC1。

图37a 深度下电指令(SPI模式)

图37b 深度下电指令(QPI模式)

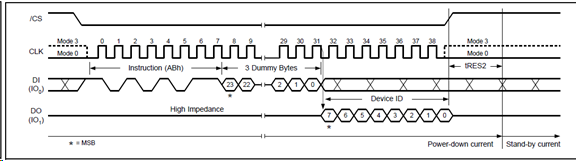

8.2.24 释放下电/器件ID(0xAB)

释放下电/器件ID指令是个多用途指令。其可以将器件从下电模式中释放,或者从器件中获取电气ID序号。

将器件从下电模式释放,指令首先将/CS拉低,然后向器件发送0xAB,再将/CS拉高,参见图38a和38b。从释放下电到器件恢复为正常操作模式从而可接收其他指令的时间是t_RES1(参见AC特性)。在t_RES1时间内必须保证/CS仍然为高电平。

如果本指令仅用来在非下电模式下获取器件ID,则需要先将/CS拉低,然后发出指令码0xAB,然后跟上3个无效字节。器件ID在CLK的下降沿出现,MSb先出。W25Q128FV的器件ID可参看制造商和器件ID表。器件ID可以连续读取。指令的结束通过驱动/CS为高电平来实现。

如果指令既用来释放下电,又用来获取器件ID,指令的过程和前述一致,参见图38c和38d,唯一的要求是/CS拉高之后的t_RES2(参见AC特性)时间内仍必须保持为高。如果器件当前正在进行擦除,编程,写循环等操作(也就是BUSY位为1),指令会被忽略,而不影响任何正在进行的操作循环。

图38a 释放下电指令(SPI模式)

图38b 释放下电指令(QPI模式)

图38c 释放下电/器件ID指令(SPI模式)

图38d 释放下电/器件ID指令(QPI模式)

8.2.25 读制造商/器件ID(0x90)

读制造商/器件ID指令是除释放下电/器件ID指令之外的另一条可以获取器件JEDEC分配的制造商ID和专用器件ID的指令。

制造商/器件ID指令类似于释放下电/器件ID指令。本指令先将/CS拉低,然后发送指令码0x90到器件,其后则为全0(0x000000)的24bit的地址(A23-A0)。之后,Winbond的制造商ID(0xEF)以及器件ID将会在接下来的CLK的下降沿输出,MSb先出,见图39。W25Q128FV器件ID的值可以参考制造商和器件ID表。指令的结束通过驱动/CS为高来完成。

图39 读制造商/器件ID指令(SPI模式)

8.2.26 双IO读制造商/器件ID(0x92)

双IO读制造商/器件ID指令是除读制造商/器件ID指令之外的另一种获得JEDEC分配的制造商ID和特定器件ID的指令,速度是后者的2倍。

双IO读制造商/器件ID指令类似于双IO快速读指令。该指令需要先将/CS引脚拉低,然后向器件发送指令码0x92,以及24位全0(0x000000)地址(A23-A0),但是该指令发送地址时每个CLK周期发送2bit。之后,制造商ID(0xEF)和器件ID将会在每个CLK时钟的下降沿输出2bit,MSb先输出,参见图40。W25Q128FV的器件ID值可以参见制造商和器件ID表。制造商和器件ID值可以连续循环读取,两者循环输出。该指令通过将/CS引脚拉高来完成。

图40 双IO读制造商/器件ID(仅SPI模式)

注意:

“连续读模式”控制位M(7-0)必须设置为0xFx,以适应双IO快速读指令。

8.2.27 四IO读制造商/器件ID(0x94)

四IO读制造商/器件ID指令是另一种获取JEDEC分配的制造商和特定器件ID的方法,其相比于单线,提供4X的速度。

四IO读制造商/器件ID指令类似于四IO快速读指令。指令通过拉低/CS引脚来启动,然后输入指令码0x94,其后跟上24位(A23-A0)全0地址(0x000000),以及4个周期的无效数据。Winbond公司的制造商ID(0xEF)以及器件ID将会在其后的每个CLK下降沿输出,MSb在前,参考图41。W25Q128FV的器件ID可参看制造商和器件ID表。制造商和器件ID可以连续读取,这个两个值交替出现。该指令的结束通过拉高/CS来完成。

图41 四IO读制造商/器件ID(仅SPI模式)

注意:

“连续读模式”位M(7-0)必须设置为Fxh,来兼容四IO快速读指令。

8.2.28 读唯一ID序列号(0x4B)

读唯一ID序列号指令用来获取每片W25Q128FV在出厂时就设置好的只读的64位唯一序列号。用户的软件算法可以利用此ID序列号来保护系统被抄袭。该指令通过拉低/CS引脚发起,然后通过发送0x4B指令,以及4个字节的无效时钟,在此之后,64位的ID序列号将在每个时钟的下降沿上出现,参见图42。

图42 读唯一ID序列号指令(仅SPI模式)

8.2.29 读JEDEC ID(0x9F)

出于通用性考虑,W25Q128FV提供了几条指令以从电气上确定器件的身份。读JEDEC ID指令兼容JEDEC在2003年采用的SPI兼容的串行FLASH标准。该指令通过拉低/CS引脚发起,然后向器件发送0x9F指令。JEDEC分配的Winbond的制造商ID(0xEF)以及2个器件ID字节,内存类型(ID15-ID8)和容量(ID7-ID0)会在之后的每个CLK下降沿从器件中发出,MSb在先,参看图43a和图43b。关于存储器类型和容量字段,可参考制造商和器件ID表。

图43a 读JEDEC ID指令(SPI模式)

图43b 读JEDEC ID指令(QPI模式)

8.2.30 读SFDP寄存器(0x5A)

W25Q128FV包含有256字节的串行FLASH可发现参数(SFDP)寄存器,包含了关于器件配置,有效指令集等信息。SFDP参数存储在一或者多个参数识别(PID)表。当前只有一个PID表被指定,但是将来可能有更多项目会加入。读SFDP寄存器指令兼容2010年为PC和其他应用设定的SFDP标准,以及2011年出版的JESD216标准。绝大多数2011年6月份之后(日期码1124及之后)上市的Winbond公司SPI Flash存储器都支持SFDP功能,可参考数据手册。

读SFDP指令通过拉低/CS引脚为低,然后通过DI引脚发出指令码0x5A,以及24位的地址(A23-A0)。其后需要8个无效时钟周期,然后SFDP寄存器的内容则会在第40个及之后的CLK下降沿上输出,MSb在先,参考图34。关于SFDP寄存器的值和表述,可参考Winbond应用说明中的SFDP定义表。

注意1:A23-A8=0,A7-A0用来确定256字节SFDP寄存器的读取的起始地址。

图34 读SFDP寄存器指令序列

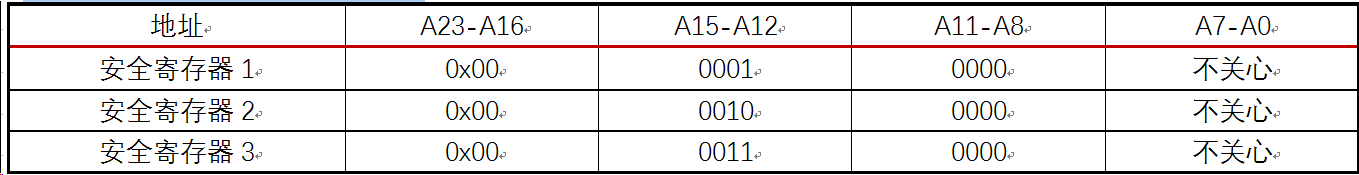

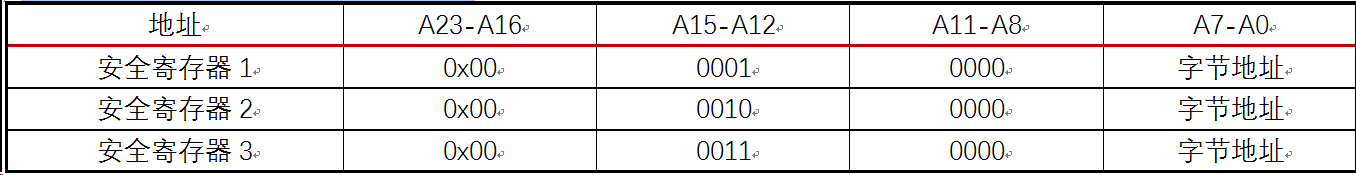

8.2.31 擦除安全寄存器(0x44)

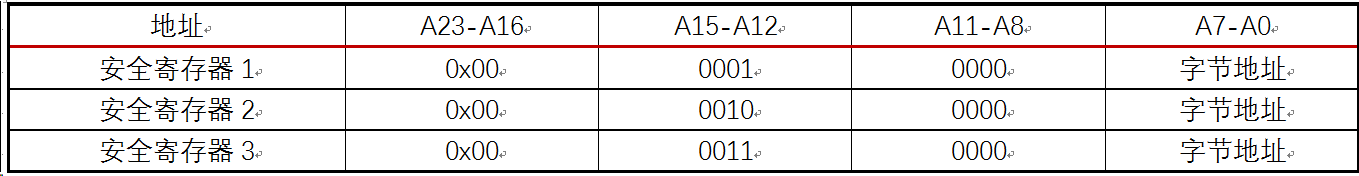

W25Q128FV提供3组256字节的安全寄存器,这些寄存器可以被独立地擦除和编程。这些寄存器可用于制造商在存储器阵列之外,保存安全或者其他重要的信息。

擦除安全寄存器指令,类似于扇区擦除指令。在器件可接受擦除安全寄存器指令之前,需要先给出写使能指令(设置状态寄存器的WEL为1)。本指令通过将/CS拉低,然后向器件发送指令码0x44,其后跟上24位地址(A23-A0),以擦除3组安全寄存器中的1组。 擦除安全寄存器指令序列参考图45。/CS引脚必须在在最后一个字节的第8位发送完成后拉高。如果没有这么做,指令不会被执行。在/CS拉高之后,内部自同步的擦除安全寄存器操作将会持续t_SE(参见AC特性)。如果擦除安全寄存器循环正在进行,读状态寄存器指令仍然可用,并且应该使用该指令以获取状态寄存器的BUSY位。如果擦除循环仍然在进行,则BUSY是1,如果循环结束,器件可接受其他指令,则该位为0。擦除安全寄存器指令循环结束后,状态寄存器中的WEL位将会清0。状态寄存器2中的安全寄存器锁定位(LB3-1)可以一次性编程以用来保护安全寄存器。一旦某锁定位设置为1,则相应的状态寄存器被永久地锁定,针对此状态寄存器的擦除安全寄存器指令将会被忽略(参考7.1.8章节获取详细描述)。

擦除安全寄存器指令序列参考图45。/CS引脚必须在在最后一个字节的第8位发送完成后拉高。如果没有这么做,指令不会被执行。在/CS拉高之后,内部自同步的擦除安全寄存器操作将会持续t_SE(参见AC特性)。如果擦除安全寄存器循环正在进行,读状态寄存器指令仍然可用,并且应该使用该指令以获取状态寄存器的BUSY位。如果擦除循环仍然在进行,则BUSY是1,如果循环结束,器件可接受其他指令,则该位为0。擦除安全寄存器指令循环结束后,状态寄存器中的WEL位将会清0。状态寄存器2中的安全寄存器锁定位(LB3-1)可以一次性编程以用来保护安全寄存器。一旦某锁定位设置为1,则相应的状态寄存器被永久地锁定,针对此状态寄存器的擦除安全寄存器指令将会被忽略(参考7.1.8章节获取详细描述)。

图45 擦除安全寄存器指令(仅SPI模式)

8.2.32 编程安全寄存器(0x42)

编程安全寄存器指令类似于页编程指令。该指令允许将之前擦除过的(内容0xFF)的安全寄存器区域中的1~256字节编程。在发出该指令之前,需要使用写使能指令将状态寄存器中的WEL设置为1。该指令通过将/CS引脚拉低来发起,然后通过DI引脚发送指令码0x42,24位地址(A23-A0),以及至少1字节数据到器件。/CS引脚必须在指令发送的整个过程中保持为低。 编程状态寄存器指令序列参见图46。可以使用状态寄存器2中安全寄存器锁定位(LB3-1)来一次性编程,以保护状态寄存器。如果一个锁定位为1,则相应的安全寄存器被永久锁定。针对这些寄存器的编程安全寄存器指令将会被忽略(参考图7.1.8,8.2.25以获取详细描述)。

编程状态寄存器指令序列参见图46。可以使用状态寄存器2中安全寄存器锁定位(LB3-1)来一次性编程,以保护状态寄存器。如果一个锁定位为1,则相应的安全寄存器被永久锁定。针对这些寄存器的编程安全寄存器指令将会被忽略(参考图7.1.8,8.2.25以获取详细描述)。

图46 编程安全寄存器指令(仅SPI模式)

8.2.33 读安全寄存器(0x48)

读安全寄存器指令类似于快速读指令,允许从3个安全寄存器中的1个中顺序地读取1个或者多个字节。该指令通过拉低/CS引脚来发起,通过DI引脚向器件发送指令码0x48,24位地址(A23-A0),以及8个无效时钟周期。指令码和地址位在CLK的上升沿锁定。地址接收到之后,地址寻址的位置对应的数据字节将会在CLK的下降沿发出,MSb在先。数据输出之后,字节地址会自动增加到下一个字节地址。一旦字节地址到达寄存器的最后一个字节(字节地址0xFF),字节地址将会复位为0x00,也就是安全寄存器中的第一个字节,然后继续递增。指令的完成通过驱动/CS为高电平来完成。读安全寄存器指令序列可参见图47。如果器件正在执行擦除,编程或者写循环正在执行(BUSY=1),则读安全寄存器指令将会被忽略,该指令不会影响任何当前的执行循环。读状态寄存器指令允许时钟速率从直流到FR(参见AC电气特性)。

图47 读安全寄存器指令(仅SPI模式)

8.2.34 设置读参数(0xC0)

在QPI模式下,为了在各种应用中,根据不同的最高读取速度和最小的数据延时需求,“设置读参数(0xC0)”指令可以用来配置指令“快速读(0x0B)”,“四IO快速读(0xEB)”,““回环突发读(0x0C)”中的无效时钟数,以及配置“回环突发读(0x0C)”中的“回环长度”字节数。

在标准SPI模式下,“设置读参数(0xC0)”指令不会被接受。在标准SPI/双线SPI/四线SPI模式下,各种快速读指令中的无效时钟数是固定的,可参考指令表1-2获取详细信息。“回环长度”可以通过“设置回环突发(0x77)”指令设置W5-4位来修改。当器件从标准SPI模式切换到QPI模式时,这些设置仍然不会改变。

上电或者复位之后的缺省的“回环长度”是8字节,缺省的无效时钟数是2。QPI模式下,仅可配置“快速读(0x0B)”,“四IO快速读(0xEB)”,以及“回环突发读(0x0C)”指令的无效时钟数。不论何时设置器件从SPI模式到QPI模式,无效时钟数必须在0x0B,0xEB和0x0C指令之前重新设置。

图48 设置读参数指令(仅QPI模式)

8.2.35 回环突发读(0x0C)

“回环突发读(0x0C)”指令提供另一种方式,来执行QPI模式下的“回环”读操作。指令类似于QPI模式下“快速读(0x0B)”指令,除了读操作将会在到达边界后立即“回环”到“回环长度”的开始位置。

“回环长度”和无效时钟数可以通过“设置读参数(0xC0)”指令配置。

图49 环回突发读指令(仅QPI模式)

8.2.36 进入QPI模式(0x38)

W25Q128FV支持标准/双线/四线串行外设接口(SPI)和四线外设接口(QPI)。但是SPI模式和QPI模式不能够同时使用。“进入QPI(0x38)”指令是唯一的将器件从SPI模式切换到QPI模式的指令。

上电之后,缺省的状态是标准/双线/四线SPI模式。这提供了向Winbond之前几代的串行Flash存储器的兼容。参看指令表1-3以获取所有支持的SPI指令。为了将器件切换到QPI模式,状态寄存器2中的QE位必须设置为1,然后再向器件发出“进入QPI(0x38)”指令。如果QE位为0,“进入QPI(0x38)”指令会被忽略,器件会仍然处在SPI模式。

参见指令表3获取所有QPI模式下支持的指令。

当前器件从SPI模式切换为QPI模式,已经存在的写使能,编程/擦除挂起状态,以及回环长度设置仍然不会改变。

图50 进入QPI指令(仅SPI模式)

8.2.37 离开QPI模式(0xFF)

如果需要离开QPI模式,进入标准/双线/四线SPI模式,必须使用“离开QPI(0xFF)”指令。

如果器件从QPI模式切换为SPI模式,已经存在的写使能锁定(WEL),和编程/擦除挂起状态,以及回环长度设置仍然不会改变。

图51 离开QPI指令(仅QPI模式)

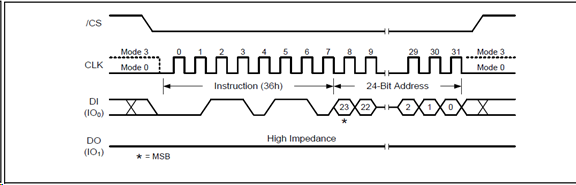

8.2.38 独立块/扇区锁定(0x36)

独立块/扇区锁定提供了另一种避免存储器阵列被不期望地擦除/编程。如果需要该指令,状态寄存器3中的WPS位必须设置为1。如果WPS=0,写保护则由状态寄存器中的CMP,SEC,TB,BP[2:0]等位共同决定。独立块/扇区锁定位是易失位。器件上电或者复位之后,这些位的缺省值是1,这样整片存储阵列都会被保护。

为了像图4d那样锁定一个特定的块或者扇区,独立块/扇区锁定命令首先由拉低/CS发起,然后在DI引脚上通过CLK的上升沿输入指令码0x36,连同24位地址,然后驱动/CS为高电平。在此之前,还必须给出写使能指令,从而设置WEL=1。

图52a 独立块/扇区锁定指令(SPI模式)

图52b 独立块/扇区锁定指令(QPI模式)

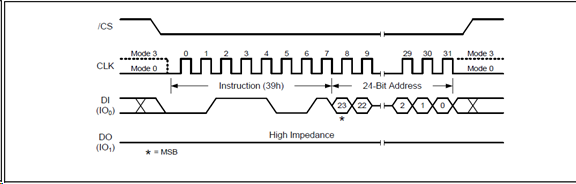

8.2.39 独立块/扇区解锁(0x39)

独立块/扇区锁定提供了另一种避免存储器阵列被不期望地擦除/编程。如果需要使用该指令,状态寄存器3中的WPS位必须设置为1。如果WPS=0,写保护则由状态寄存器中的CMP,SEC,TB,BP[2:0]等位共同决定。独立块/扇区锁定位是易失位。器件上电或者复位之后,这些位的缺省值是1,这样整片存储阵列都会被保护。

如果如图4d那样需要解锁特定的块或者扇区,独立块/扇区解锁指令通过拉低/CS引脚来发起,然后通过DI引脚在CLK的上升沿输入指令码0x39,连同24位地址,然后驱动/CS信号为高。在此之前必须给出写使能指令,以设置WEL位1。

图53a 独立块解锁指令(SPI模式)

图53b 独立块解锁指令(QPI模式)

8.2.40 读块/扇区锁定状态(0x3D)

独立块/扇区锁定提供了另一种避免存储器阵列被不期望地擦除/编程。如果需要使用该指令,状态寄存器3中的WPS位必须设置为1。如果WPS=0,写保护则由状态寄存器中的CMP,SEC,TB,BP[2:0]等位共同决定。独立块/扇区锁定位是易失位。器件上电或者复位之后,这些位的缺省值是1,这样整片存储阵列都会被保护。

如图54a那样,读取一个特定的块或者扇区的的块锁定位,可以使用读块/扇区锁定命令获取。该指令通过拉低/CS引脚发起,然后通过DI引脚在CLK的上升沿输入指令码0x3D,连同24位地址。其后,块/扇区锁定位将在CLK的下降沿输出,MSb在先,如图54。如果LSb位为1,则对应的块/扇区被锁定;如果LSb位为0,则对应的块/扇区未被锁定,可以执行擦除/编程操作。

图54a 读块锁定状态指令(SPI模式)

图54b 读块锁定状态指令(QPI模式)

8.2.41 全局块/扇区锁定(0x7E)

所有的块/扇区锁定位可以通过全局块/扇区锁定指令来设置为1。该指令通过将/CS引脚拉低来发起,然后通过DI引脚在CLK的上升沿输入指令码0x7E,最后将/CS拉高。在此之前,必须使用写使能指令来设置状态寄存器中的WEL为1,以使得器件可以接收全局块/扇区锁定指令。

图55 全局块锁定指令(左SPI模式,右QPI模式)

8.2.42 全局块/扇区解锁(0x98)

所有的块/扇区锁定位可以通过全局块/扇区解锁指令设置为0。该指令的发起通过驱动/CS引脚为低,然后通过DI引脚在CLK的上升沿输入指令码0x98,再驱动/CS为高。在此之前,必须先给出写使能指令,设置状态寄存器中的WEL为1,使得器件可以接受全局块/扇区解锁指令。

图56 全局块解锁指令(左为SPI模式,又为QPI模式)

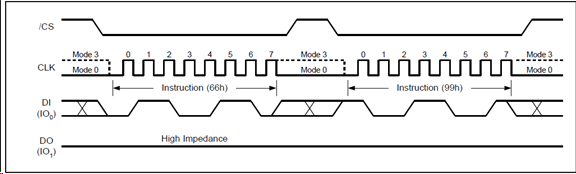

8.2.43 允许复位(0x66)和复位器件(0x99)

由于较小的封装和引脚数量限制,W25Q128FV提供软件复位指令以替代专用的复位引脚。一旦器件接受了复位指令,任何正在进行的内部操作将会终止,器件将会进入缺省的上电状态,丢失当前所有的易失性设置,例如易失性状态寄存器位,写使能锁定(WEL)位,编程/擦除挂起位,读取参数设置(P7-P0),连续读模式位(M7-M0)以及环回位设置(W6-W4)。

“允许复位(0x66)”和“复位(0x99)”指令既可以在SPI模式发出也可以在QPI模式发出。为了避免意外的复位,这两条指令必须按顺序发送。在“允许复位(0x66)”命令之后,除了“复位(0x99)”之外的任何其他的命令,将会禁止“允许复位”状态。此时如果需要复位器件,则需要重新发送“允许复位(0x66)”和“复位(0x99)”指令序列。一旦复位指令被器件接受,器件需要大约t_RST=30us的时间来进行复位。在此期间,任何指令都不会被接受。

如果器件接受复位命令序列时,正在进行或者挂起的内部擦除或者编程指令,则数据可能会被损坏。因此,建议在给出复位命令序列之前,先检查状态寄存器中的BUSY位和SUS位。

图57a 允许复位和复位指令序列(SPI模式)

图57b 允许复位和复位指令序列(QPI模式)

9 AC特性

(略,参看英文数据手册)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?