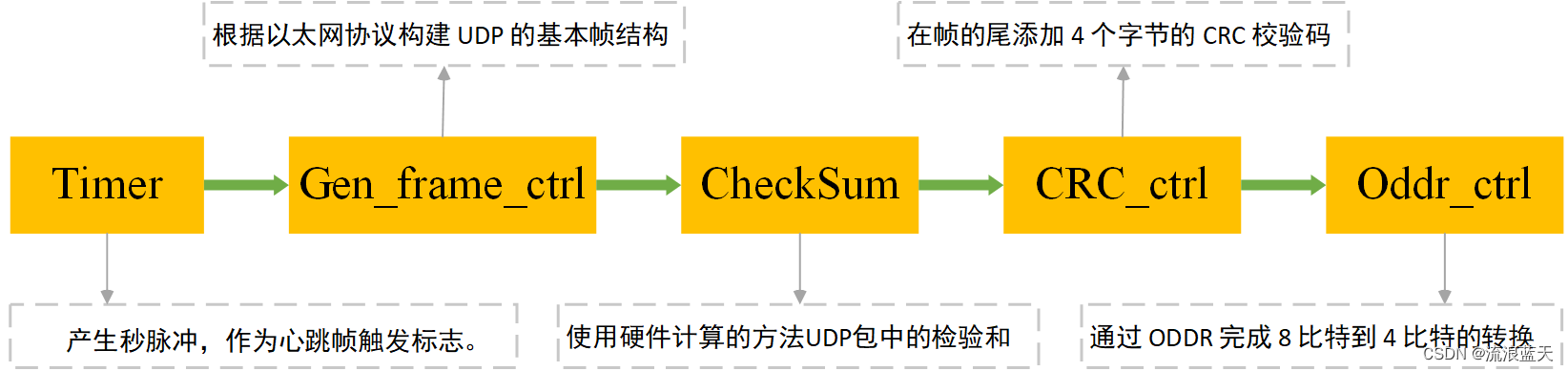

在上一篇千兆以太网数据发送(二):IP、UDP检验和计算中,我们完成了IP校验和、UDP校验和的计算,并将计算结果填充在以太网协议帧中的对应位置,输出数据信号check_data[7:0]和数据有效信号check_en。至此,完成了下图中发送链路timer模块、gen_frame_ctrl模块和check_sum模块,但是CRC字段都给的0。本文将在此基础上计算出CRC校验和,进一步完善以太网数据包。

一、CRC校验模块

CRC校验时不对以太网帧头进行计算,即不包含开头的7个0x55和1个0xd5,因此我们设置一个标志位,当数据是帧头部分时拉低标志位crc_ds,否则拉高。这样就可以根据crc_ds的值去控制crc计算的输入:当crc_ds == 0时crc输入为0,当crc == 1时crc输入为模块输入的数据。

计算完成的CRC校验值填充在数据帧的末尾。值得注意的是,CRC计算中初始值为0xFFFFFFFF,计算结果需要高低位对调,并且计算结果需要取反操作。

模块的输入是上级模块输出的数据信号check_data[7:0]和使能信号check_en,模块输出是填充好CRC检验码的数据信号dout[7:0]和数据有效信号dsout。

二、ODDR源语

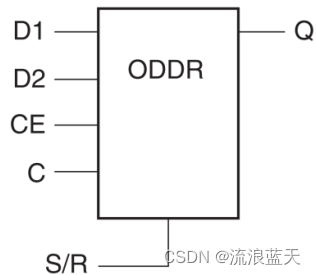

源语功能:把两路单端的数据合并到一路上输出,上下沿同时输出数据,上升沿输出 a 路,下降沿输出 b 路。ODDR 的原语结构图如下图所示:

C:输入的同步时钟;

Q:输出的 1 位 DDR 数据;

D1 和 D2:分别是“ C”时钟上升沿和下降沿同步输入的 SDR 数据;

CE:时钟使能信号;

S/R:置位/复位信号,这两个信号不能同时拉高。

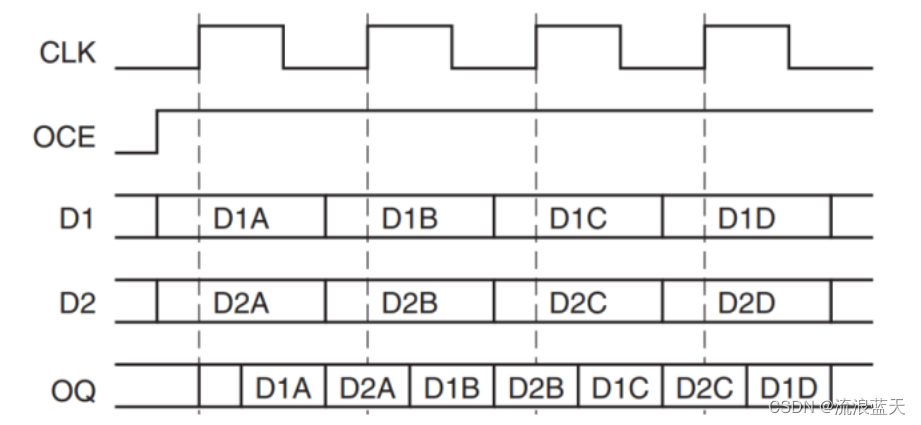

DDR_CLK_EDGE 参数为 ODDR 的两种输出模式,一般我们使用SAME_EDGE模式,在该模式下数据可以在相同的时钟边沿输出到 Q。SAME_EDGE 模式的时序图如下图:

代码中ODDR源语的调用如下图。模式选择“SAMEEDGE”,初始值设置为1'b0。以输出tx_clk以太网发送时钟为例,使D1 = 1'b1,D2 = 1'b0,则输出Q会在sclk的上升沿等于1,在sclk的下降沿等于0,即tx_clk。

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("ASYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_CLK_inst (

.Q(tx_clk), // 1-bit DDR output

.C(sclk), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(1'b1), // 1-bit data input (positive edge)

.D2(1'b0), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

); 三、仿真验证

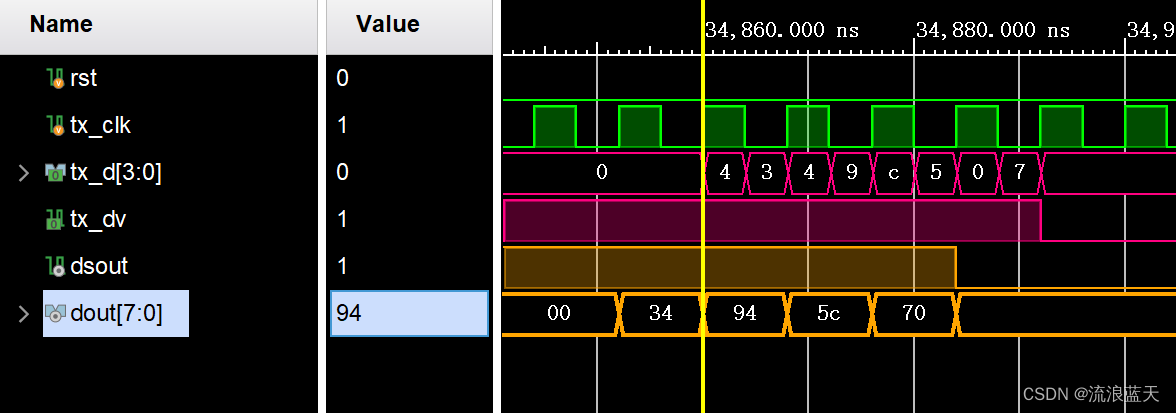

将CRC模块的输出dout[7:0]、dsout和ODDR模块的输出信号tx_dv、tx_d[3:0]丢进ILA,抓取数据波形如下图。可以看到CRC计算结果已经添加在数据帧的末尾,为0x34945c70。经ODDR模块转换为DDR信号tx_d[3:0],在tx_clk的上升沿输出数据的低四位,下降沿输出数据的高四位。

四、上板验证

至此,我们分别实现了 链路timer模块、gen_frame_ctrl模块、check_sum模块、crc_crtl模块和oddr模块,完成了以太网发送链路中心跳帧的组建。将这些模块移植到之前写的千兆网以太网数据接收工程中千兆网数据接收(二),实现了这样的功能:上位机可以向FPGA发送数据,并且在没有发送数据时可以接收来自于FPGA的心跳包,以此证明FPGA在线。

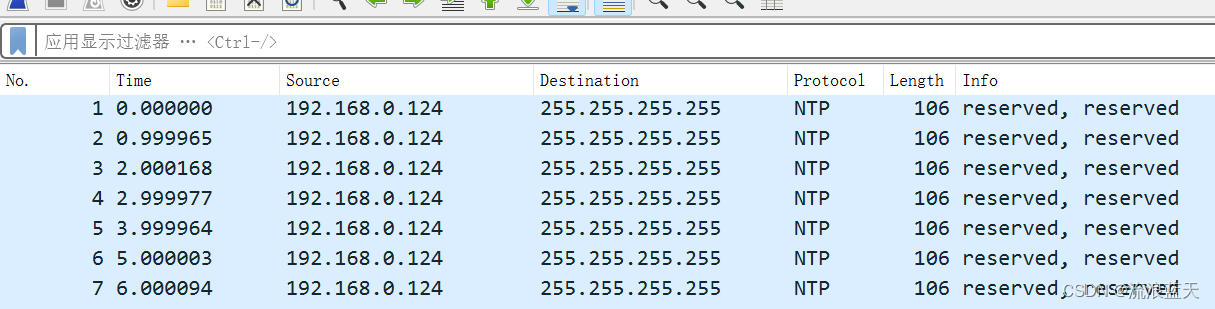

设置上位机IP地址192.168.0.123,端口号123;FPGA端MAC地址48'h00_11_22_33_44_55,IP地址192.168.0.124,端口号1234。将生成的bitstream文件下载到FPGA中,使用网线连接PC和FPGA,利用Wireshark抓取数据包如下:

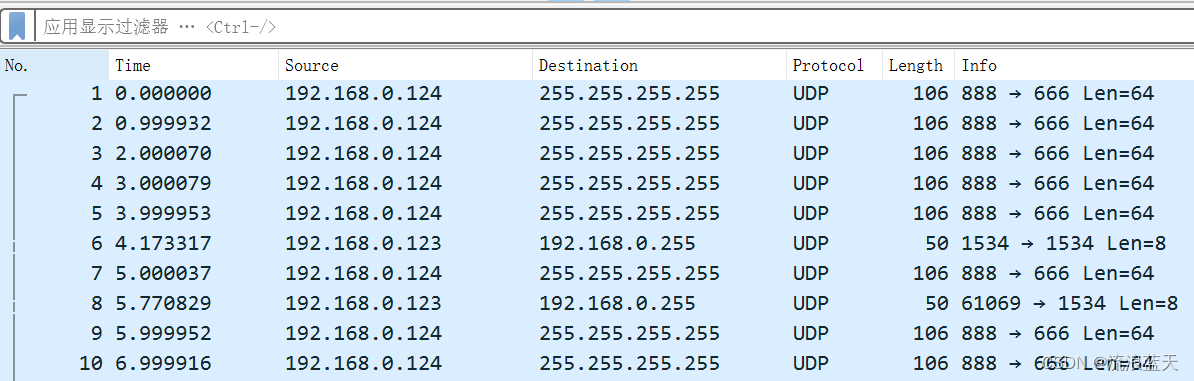

可以发现抓到的包虽然是以1S为间隔的,但是并不是UDP包,而是NTP包,这是为什么呢?查阅资料后得知, NTP 是用来同步计算机系统时钟的协议,它通过网络获取和同步各个计算机的时钟。并且NTP 使用UDP作为传输协议,通常在UDP的端口号123上运行。既然这样,回去把上位机端口号修改成666,将FPGA端口号修改为888,重新抓包后如下图:

可以看到这次成功抓到了来自于FPGA的UDP心跳包,根据提示信息可知数据包来自于端口号为888的设备,数据长度为64,与我们发送的一致。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?