一、建立时间与保持时间

建立时间:指时钟边沿到来之前,数据保持稳定的时间。也就是说输入数据应该在时钟沿之前到来,这样才能保证稳定信号进入触发器。

保持时间:指时钟边沿到来之后,数据保持稳定的时间。这样可以保证数据被稳定地读取。

建立时间和保持时间在保证不发生时序违例、稳定数据被采集情况下的最小值叫做建立时间门限(Tsu)和保持时间门限(Th)。

当建立时间超过Tsu时,他们的差值叫做建立时间裕量(Tsu Slack);当保持时间超过Th时,他们的差值叫做保持时间裕量(Th Slack)。

二、建立时间分析

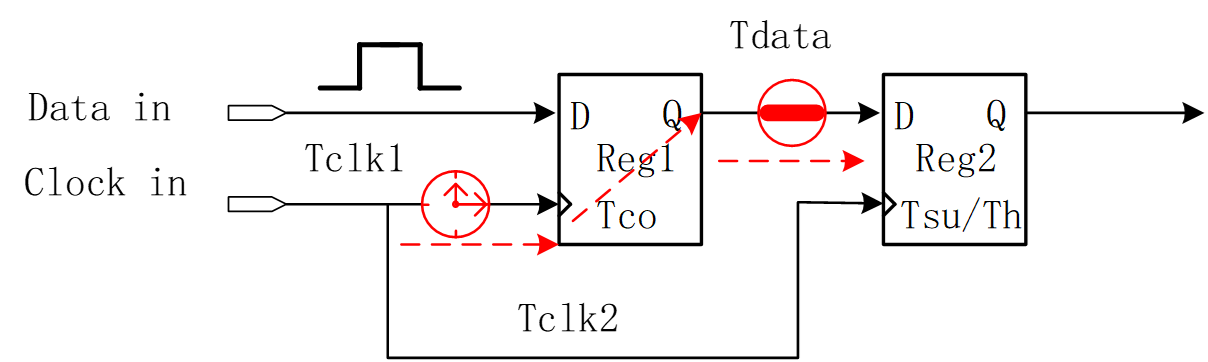

两级D触发器分析模型如下:

图中,Tclk1、Tclk2、Tdata分别表示对应线路的延时,Tco表示寄存器D-->Q的延时。假设data in已经准备好数据,并且参考时钟输入管脚为0时刻。

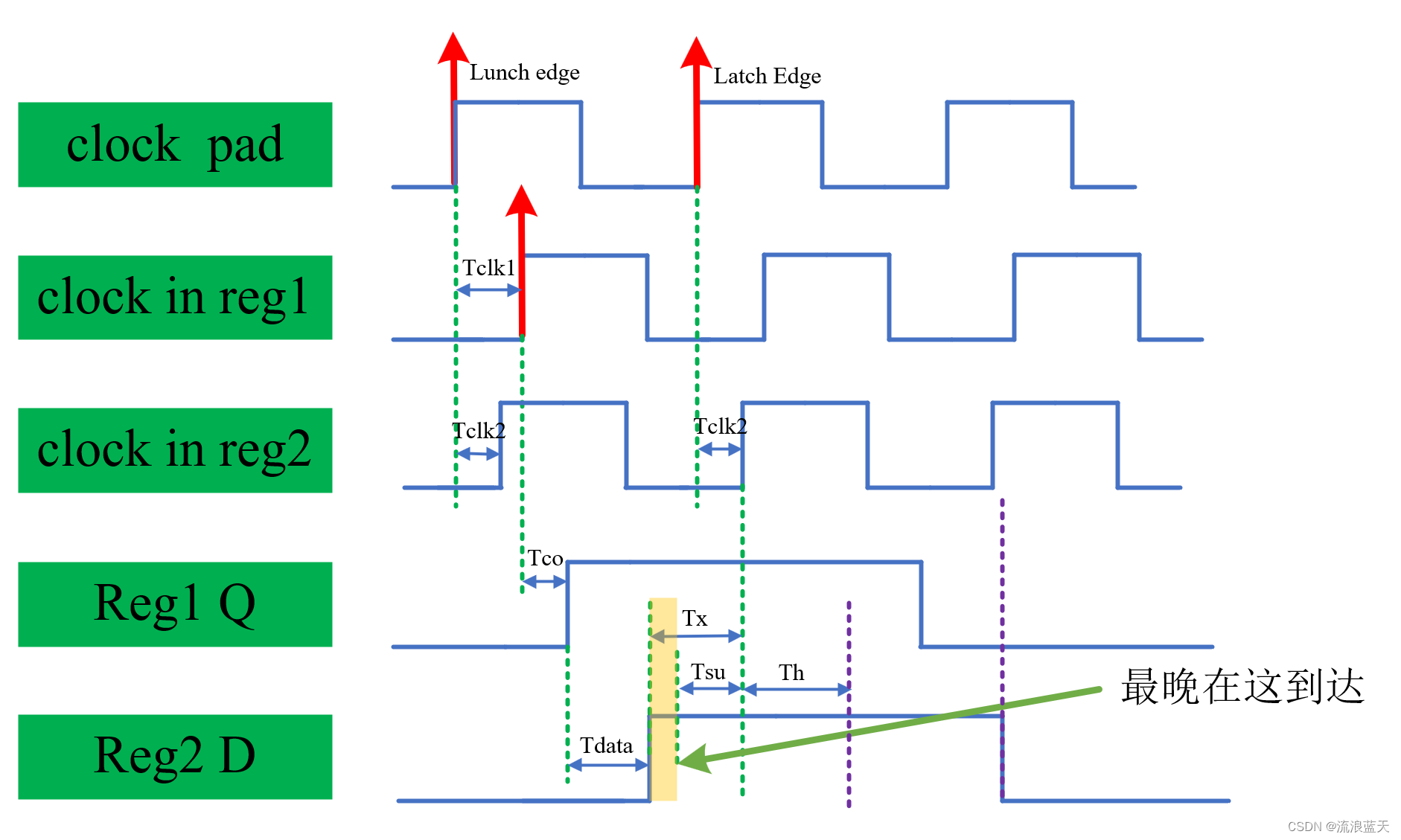

由图可知,数据由发射沿时钟到达目标采样寄存器(reg2)D端的实际时间,即 Data Arrival time = Tclk1 + Tco + Tdata;电路要求的到达时间:Data Required time = Latch edge + Tclk2 - Tsu。可得建立时间裕量Tsu Slack = (Latch Edge + Tclk2 – Tus)- (Tclk1 + Tco + Tdata)。

我们知道,为了不引起时序违例问题,要求:Tsu Slack > 0,而Tx = Tsu + Tsu Slack,因此,只有当 Tx = T + Tclk2 – Tclk1 – Tco – Tdata > Tsu才能满足时序要求。

三、保持时间分析

还是两级D触发器的模型,我们分析保持时间如下:

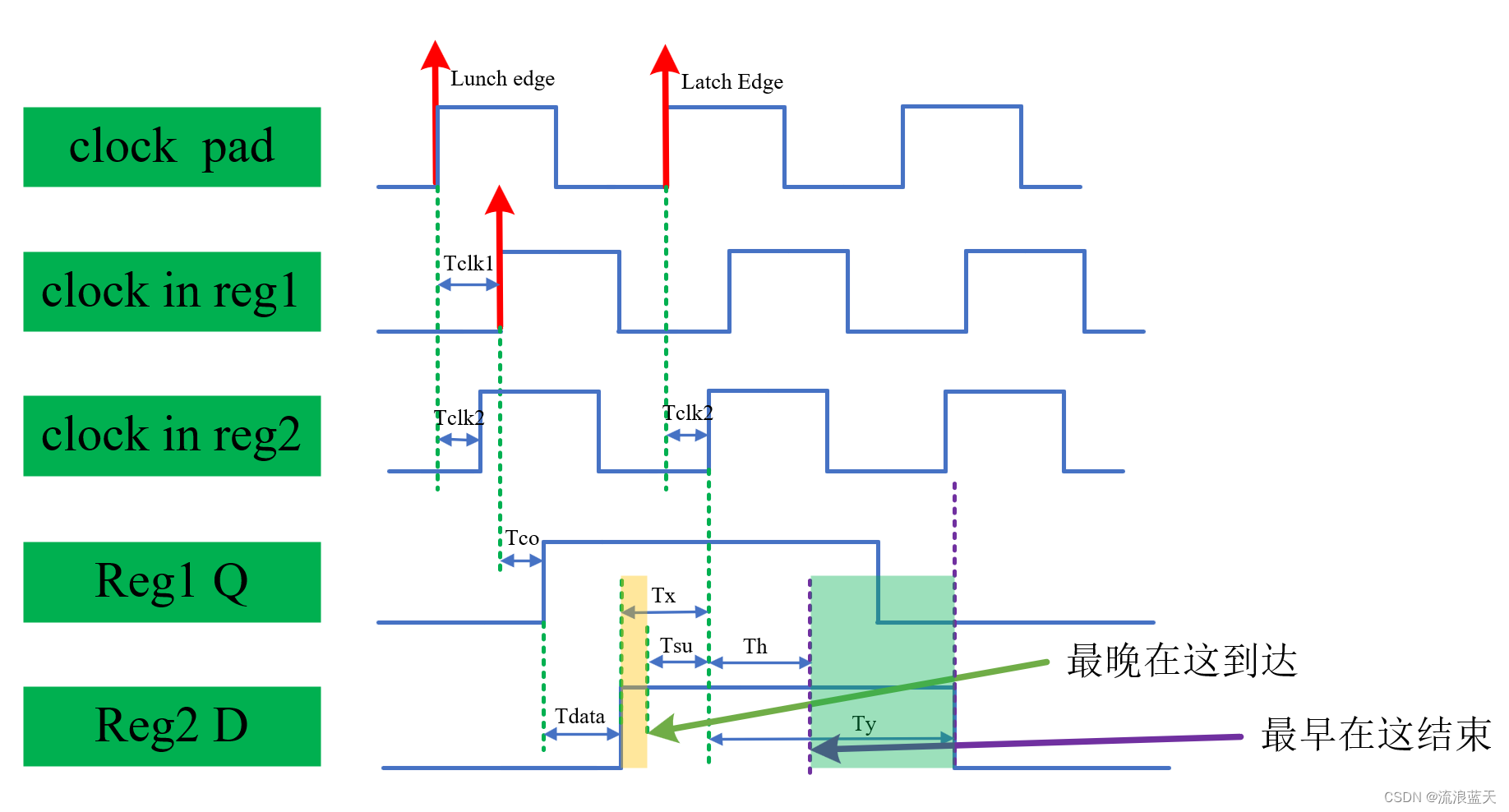

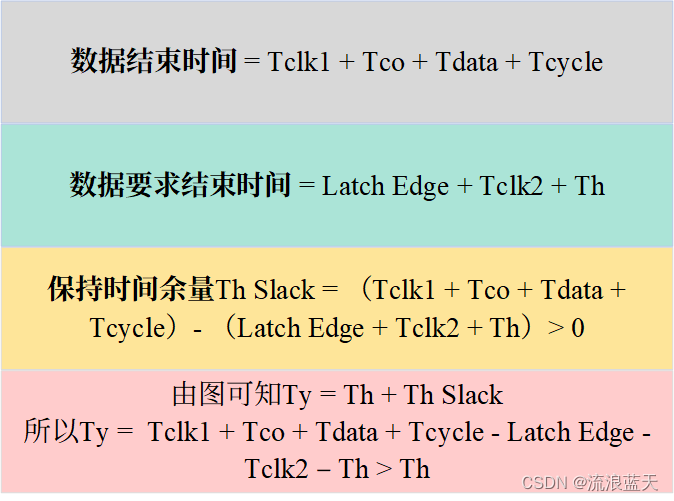

由图可知,数据的真实结束时间 Data End time = Tclk1 + Tco + Tdata + Tcycle;电路要求的数据结束时间:Data Required End time = Latch Edge + Tclk2 + Th。所以可知保持时间裕量Th Slack = (Tclk1 + Tco + Tdata + Tcycle)- (Latch Edge + Tclk2 + Th)。

同样,为了不引起时序违例问题,要求:Th Slack > 0,而Ty = Th + Th Slack,因此,只有当 Ty = Tclk1 + Tco + Tdata + Tcycle - Latch Edge - Tclk2 – Th > Th才能满足时序要求。

四、练习一下

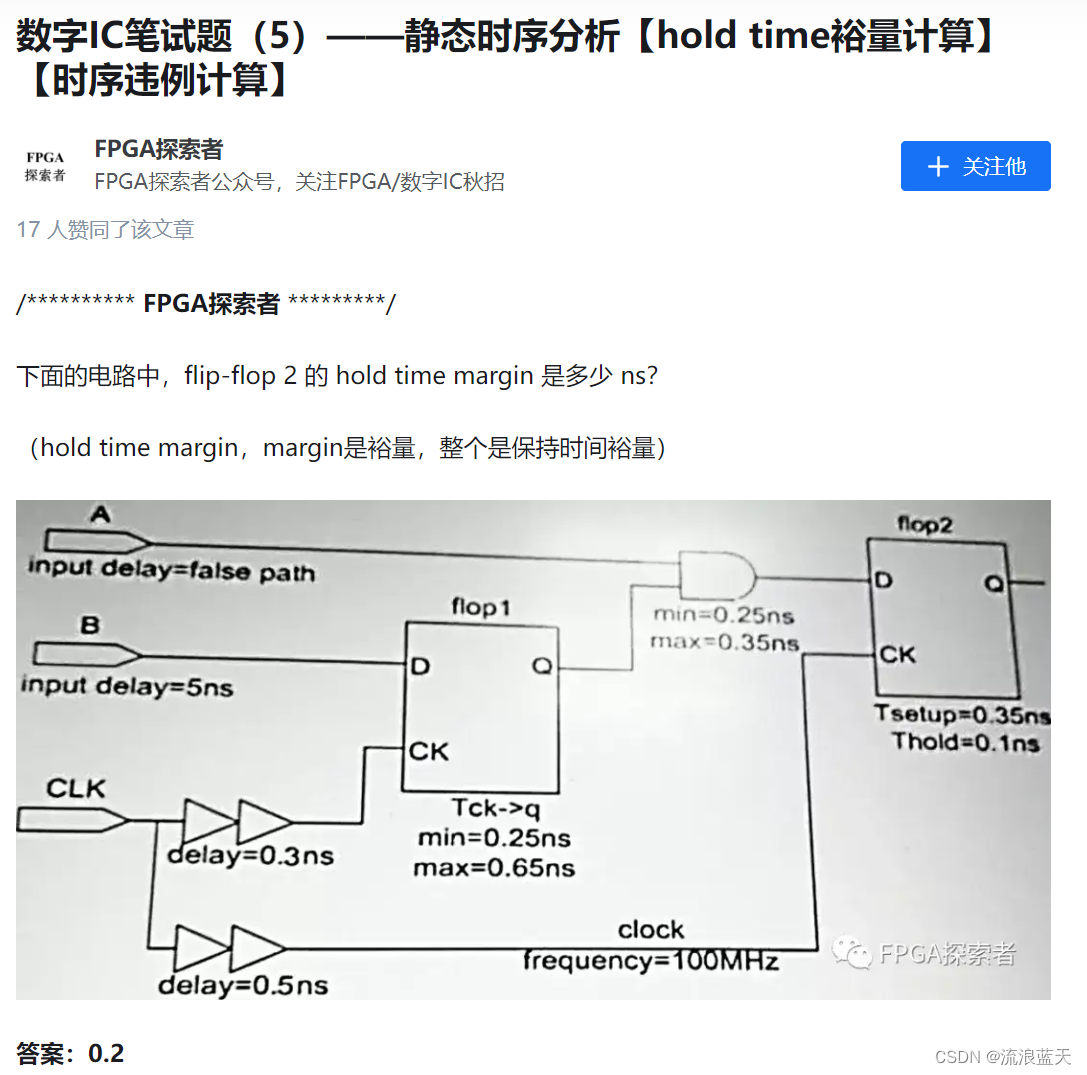

在某知某乎上找一道题:

题目要求保持时间裕量,带入我们的公式得:

Th Slack = (Tclk1 + Tco + Tdata + Tcycle)- (Latch Edge + Tclk2 + Th)

= ( 0.3 + 0.25 + 0.25 + 10) - (10 + 0.5 + 0.1)

= 10.8 - 10.6

= 0.2

很神奇,竟然算对了。回过头再分析一下,题目中A引脚 input delay = false path,应该是直接不用管。时钟频率=100Mhz,所以 Tcycle=10ns。

时序图回头再补上,但是我不知道Tck和Tdata的max和min延时在计算时应该怎么选择,请指教!

3102

3102

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?