结论

1.100pcs测试OK,5Kpcs测试OK,不代表100Kpcs、1KKpcs永远都是OK。

2.不要过于信任任何芯片物理特性方面的一致性。

3.除了注意MCU自身IO口在整机进入低功耗模式的处理,也要注意外围芯片(例如外接RF模块、EEPROM、触摸专用IC等)在整机进入低功耗模式的处理。

产品现状

一个低功耗产品在两年前由前同事开发完,工厂量产过5K,未反馈该问题。今年再次生产10K,反馈有7%不良率,不良现象是待机电流比标准待机电流60uA要高50~100uA不等,这对电池产品来讲是致命的。

更为致命的是,这批产品已经有2K出货到客户那里,如果处理不好,会带来很高额的赔偿成本。

产品架构

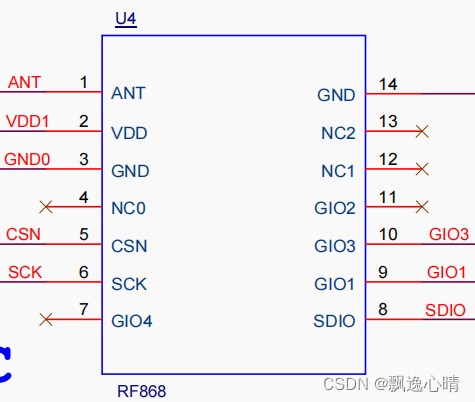

产品主要架构是一个瑞萨MCU,外接LCD显示屏、NTC采样电阻、按键以及RF模组。RF模组是使用了合泰某颗RF IC设计了一块小板。模组原理图如下

| 芯片引脚 | 功能 |

| ANT | 天线 |

| VDD | 电源正极 |

| GND | 电源地 |

| CSN | SPI通信片选引脚 |

| SCK | SPI通信时钟引脚 |

| GIO3 | 可设置功能,本项目用于中断引脚 |

| GIO1 | 可设置功能,本项目用于SPI通信MISO |

| SDIO | SPI通信MOSI引脚 |

| 其余 | 无功能,悬空 |

技术排查

1.初步怀疑RF模组不良,但是RF模组在贴到主板之前,有专门的治具测试,测试PASS的才会贴到主板上;

2.仍怀疑RF模组不良,将RF模组换到同一个项目另一个良品的主板上,待机电流OK;

3.将RF模组换回来不良主板上,待机电流仍然NG;

4.由于该RF模组也用在其他3款电池产品上,所用初始化代码一致,但是该项目使用瑞萨MCU,但其他3款均使用华大MCU。

5.无意间发现,当用手触摸CSN引脚时,待机电流恢复到标称值;当手离开CSN引脚时,待机电流又跳到高值。因此怀疑该引脚在进入低功耗时未进行恰当的处理。

由于代码是前同事开发,架构一塌糊涂,经过多层排查,最后发现在进入低功耗时:

① 将MCU上连接到模组的几个SPI引脚(模组的CSN、SCK、SDIO,下同)均设置为输入模式,且未设置上拉和下拉;

② MCU未发送命令,使模组使能这几个SPI引脚的上拉功能;

③ 这几个SPI引脚引脚在硬件上,均未放置上拉电阻;

方案验证

① 进入低功耗时,不将CSN引脚设置为输入模式,保持输出模式;

② 进入低功耗时,维持原有的将它们设置为输入模式,但使能CSN的MCU IO口上拉功能;

③ 对模组进行初始化时,使模组使能这几个SPI引脚的上拉功能(模组仅支持三个IO一起使能或除能上拉功能);

④ 在硬件电路上,在CSN引脚上新增一个100K的上拉电阻;

以上四种方案,选择任意一个均能够使得待机电流保持在标称值。

是产品已量产,选择硬件方案显然不具有经济性,最后我们选择第③种方案,使能模组内部这几个SPI引脚的上拉功能。

思考

产品在两年前进行过一轮试产,也进行过5K的量产,均未暴露出这个问题,但是今年这批量产,却暴露出这个问题,目前是RF模组的一致性问题,还是MCU的一致性问题,正在排查。

但可见产品的开发不能依赖于测试验证,无论是少数试产的验证,还是批量量产的验证。即便是批量量产,也可能因为某一批器件的物理特性,结合起来恰好使得问题被掩盖,这并不意味着每一批器件都能使得产品有预期的表现,也不意味着将来在某些特定条件下,产品仍能保持正常性能。

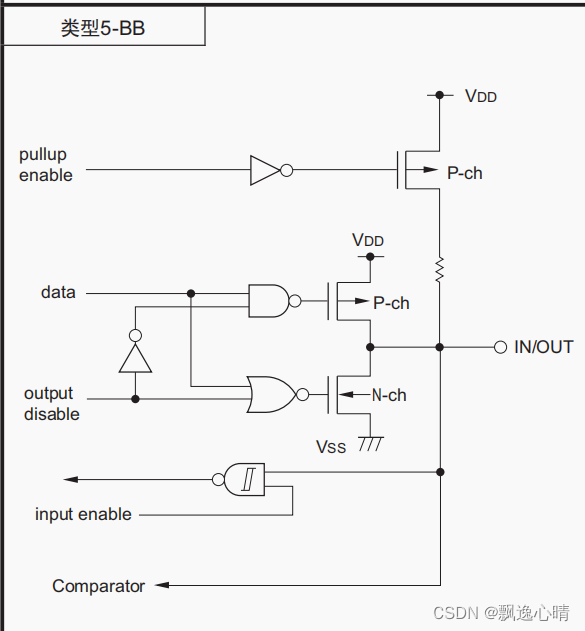

因此产品的开发,应当侧重于理论层面的分析,在技术层面需要进行深入的分析,例如要分析MCU IO口的内部结构(如下图),在输入、输出模式,使能、除能上下拉电阻,使能、除能复位功能时,是否存在着某些电流泄露的路径。

大多数工程师在开发产品时,往往只是查阅例程代码,以及规格书中相关的寄存器部分,对于诸如电特性、IO口结构、时钟电路图没有深入研究分析,只是把功能调试出来,再经过测试团队的几轮测试、工厂小批量试产就开始上市,但今天这个案例已经敲响警钟——测试不是保证产品质量的方法,考虑全面的原始设计才是唯一途径。

7101

7101

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?