重定时

Retiming是不能用在跨时钟域路径上的。

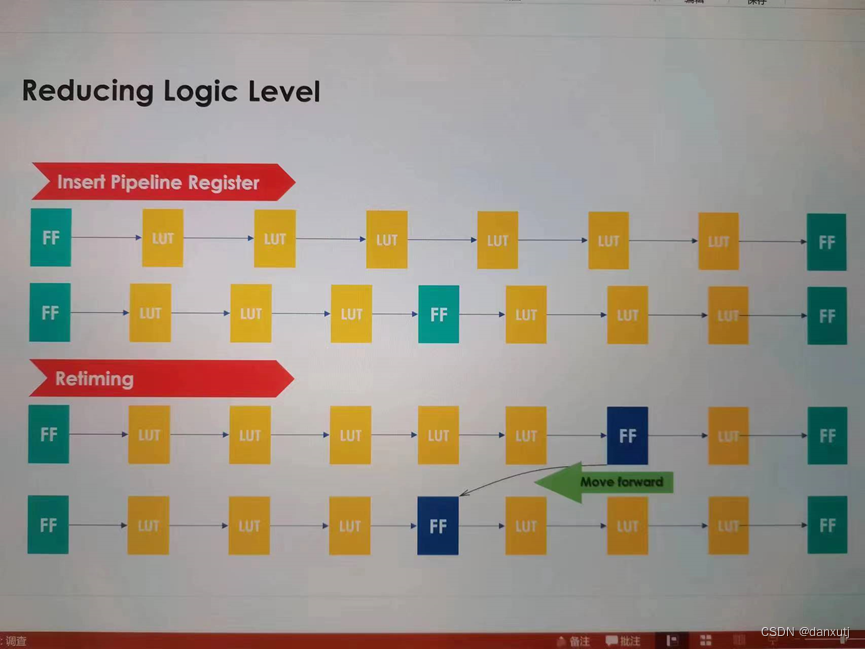

看重点,是把触发器前移或者后移,平衡逻辑级数。

通过平衡逻辑级数的方式降低逻辑延迟,达到时序收敛的目的。

布局布线阶段的种子应该怎么理解?

这个是针对ISE的,FPGA设计流程中,布局的随机性比较大,可以通过种子改变随机数,把这个原理应用在布局算法中。

Vivado里也可以这么做,比如专门设置一个32位的版本寄存器,每次改一下版本号,就相当于加入了一个随机扰动,但不建议这么做。

工具就可以实现retiming,自动优化,在代码中,如果我们预期但某个功能的logic level比较大,我们可以在前面多打几拍再送进去,工具retiming的时候可以自动把触发器放到组合逻辑中间。mentor的工具综合,效果挺好,synplify也可以。

Vivado的retiming现在已经做的很好了,打开综合选项设置界面,可勾选-retiming,这是全局设置,同时还可以选择模块化综合,对指定模块进行retiming,具体操作可查看ug901第三章。

2789

2789

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?