针对状态机,重新学习了《Verilog数字系统设计教程》(第4版夏宇闻编著)。看到第12章同步状态机的原理、结构和设计,整理了一些以前没注意到的细节。

1如何区分Mealy和Moore状态机

如果时序逻辑的输出不但取决于状态,还取决于输入,称为米勒状态机Mealy。而如果时序逻辑电路的输出只取决于当前状态,则称为摩尔状态机Moore。

我是这么理解的,简单一点儿的就是摩尔状态机,复杂一点儿的是米勒状态机。把摩尔状态机的状态弄得复杂一点,把输入包含进去,也可以实现和米勒状态机一样的状态转换。也就是下一自然段描述的第一种方式。

设计高速电路时,状态机有以下两种的设计方式,第一种是把状态变量直接用作输出,为此在指定状态编码时需要多费一些脑力。第二种方法是在输出逻辑后面再加一组与时钟同步的寄存器。让输出信号在下一个时钟跳变沿,同时存入寄存器组及完全同步的输出,也就是加一个流水线寄存器。

2 状态转移图

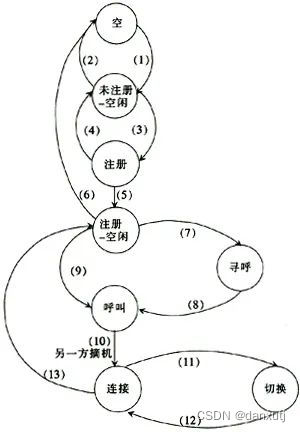

我看到这本书讲述的画状态转移图的方式。它一般是从idle的状态开始。

然后都会用斜杠线分割,前面是输入,后面是输出。比如说输入有复位信号,那么就是复位信号在什么条件下,然后输出是什么,例:Reset/k=0。

每个状态用一个椭圆来去表示,状态转移是画在两个状态之间,感觉是每一个状态细细的去读,然后根据状态转移,每一个写一个if语句,整体用一个case可以直接写出来那个状态机。

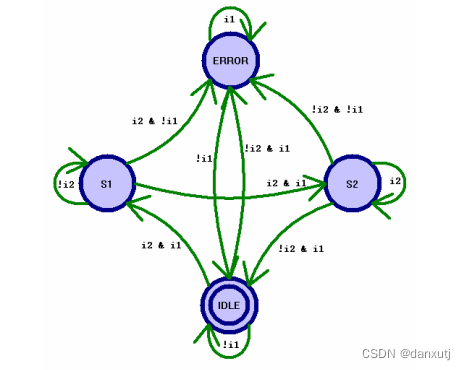

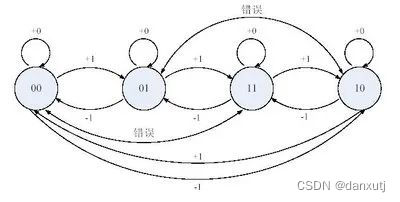

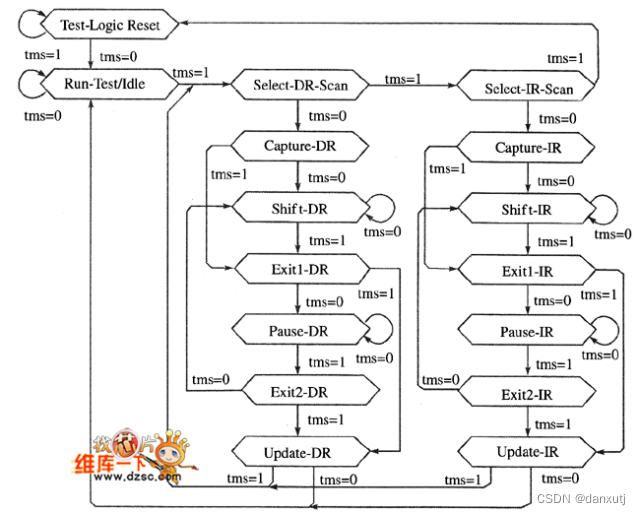

从网上找了一些状态转移图的示例,感觉还是要根据具体的项目来定,状态转移图没有确定的画法。

3 状态机的几段式

根据状态转移,每一个写一个if语句,整体用一个case可以直接写出来那个状态机,这种情况是一段式的状态机

对于比较复杂的状态机,尽量避免采用这种方式(因为都在一个always循环里不好维护)。而是用多个always循环来去写。也就是经常说的两段式或者是三段式。可以按照最多的来去写。比如现在有一个例子,这个状态机有两个输出。状态机的写法为:第一个always循环是每一个时钟炎产生一次可能的状态变化,第二个always循环是产生下一状态的组合逻辑,第三个always循环是产生输出一的组合逻辑。第四个always循环是产生输出二的组合逻辑

4 状态的编码方式

然后关于状态,一般会采取两种方式,有一种叫独热编码(有多少个状态就有多少比特,而且只有一个比特为1,其他全为0的一种码制,比如0001 0010 0100 1000),有一种叫格雷编码(它在相邻位间转换时,只有一位产生变化),究竟哪一种编码好,要看具体情况。对于用FPGA实现的有限状态机,建议使用独热码,因为虽然独热码用了多用了一些触发器,但所用的组合电路可以省一些,因此电路的速度和可靠性有有显著提高,而总的单元数并无显著增加。独热码又有一些不可到达的状态,所以最后的语句需要加default分支项(这一般都不会忘,不管什么情况,case最后都有一个default)。

241

241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?