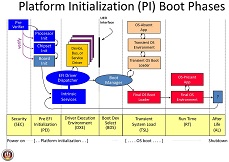

Security (SEC) Phase

The Security (SEC) phase is the first phase in the PI Architecture architecture and is responsible for the following:

- Handling all platform restart events

- Creating a temporary memory store

- Serving as the root of trust in the system

- Passing handoff information to the PEI Core

In addition to the minimum architecturally required handoff information, the SEC phase can pass optional information to the PEI Core, such as the SEC Platform Information PPI or information about the health of the processor.

UEFI.org -PI VOLUME 1: Platform Initialization Specification 1.2 Pre-EFI Initialization Core Interface

Pre-EFI Initialization (PEI) Phase

The Pre-EFI Initialization (PEI) phase of the PI Architecture specifications (hereafter referred to as the “PI Architecture”) is invoked quite early in the boot flow. Specifically, after some preliminary processing in the Security (SEC) phase, any machine restart event will invoke the PEI phase.

The PEI phase will initially operate with the platform in a nascent state, leveraging only onprocessor resources, such as the processor cache as a call stack, to dispatch Pre-EFI Initialization Modules (PEIMs).

These PEIMs are responsible for the following:

- Initializing some permanent memory complement

- Describing the memory in Hand-Off Blocks (HOBs)

- Describing the firmware volume locations in HOBs

- Passing control into the Driver E

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5132

5132

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?