名称:汽车速度表设计verilog代码具备超速报警功能

软件:QuartusII

语言:Verilog

代码功能:

速度表设计

任务与要求:

1、显示汽车时速Km/h;

2、车轮每转一圈,有一个传感脉冲:每个脉冲假定代表1m的距离;

3、采样周期设为10S:

4、要求数码管显示到小数点后2位

5、具备超速报警功能。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

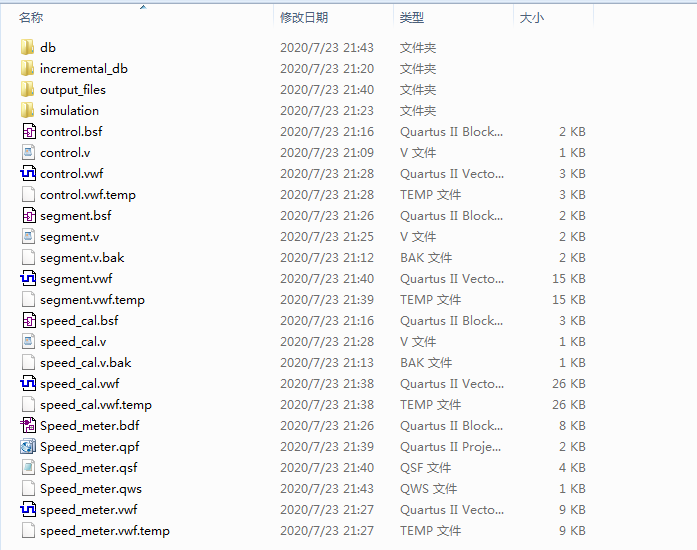

1. 工程文件

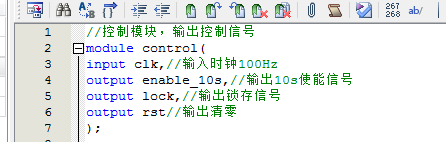

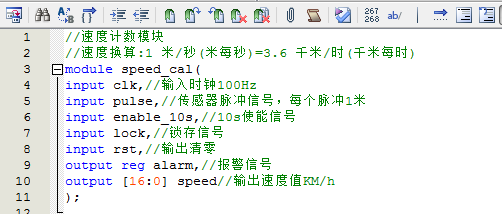

2. 程序文件

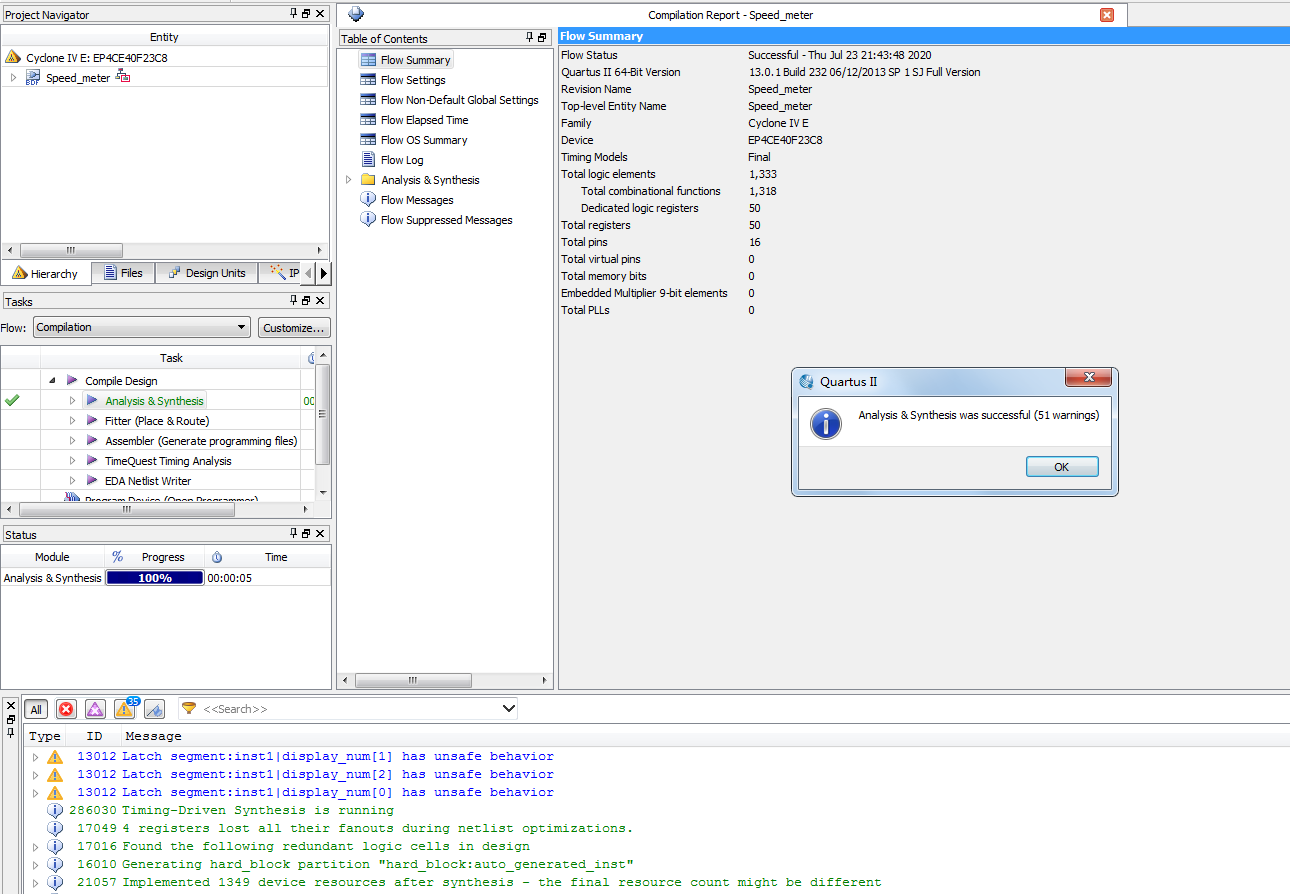

3. 程序编译

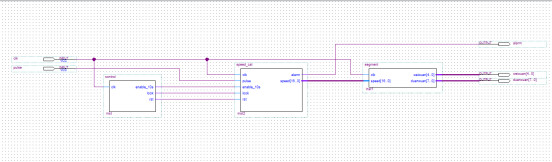

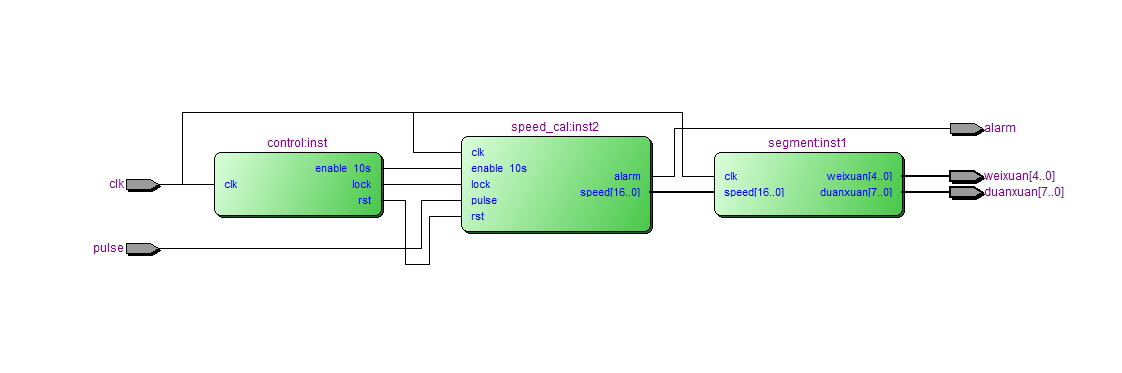

4. RTL图

5. 仿真图

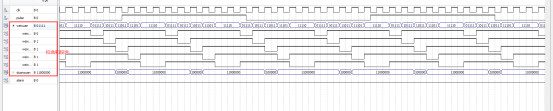

整体仿真图

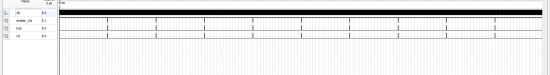

控制模块仿真图

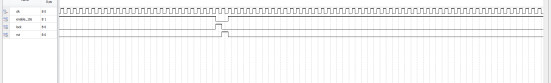

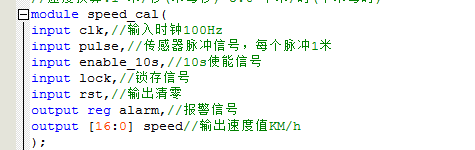

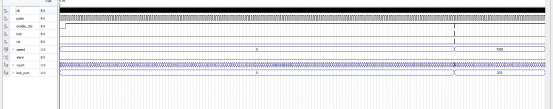

速度计算模块

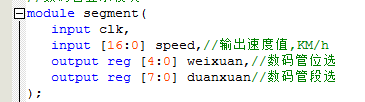

显示模块

部分代码展示:

//速度计数模块 //速度换算:1 米/秒(米每秒)=3.6 千米/时(千米每时) module speed_cal( input clk,//输入时钟100Hz input pulse,//传感器脉冲信号,每个脉冲1米 input enable_10s,//10s使能信号 input lock,//锁存信号 input rst,//输出清零 output reg alarm,//报警信号 output [16:0] speed//输出速度值KM/h ); reg [16:0] count=17'd0; always@(posedge pulse or posedge rst)//传感器脉冲计数 if(rst) count<=17'd0;//清零 else count<=count+17'd1;//传感器脉冲计数 reg [16:0] lock_num=17'd0;//锁存计数值 always@(posedge clk) if(lock)//输出锁存信号 lock_num<=count;//锁存计数值 else lock_num<=lock_num; //10s对应距离为lock_num米,速度为lock_num/10(米每秒) //输出速度值(lock_num/10)*360;//取2位小数 assign speed=lock_num*36;//取2位小数 always@(posedge clk) if(speed>15000)//超过150KM/h alarm<=1;//超速报警 else alarm<=0; endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?