名称:篮球比赛24秒倒计时器basys3开发板verilog代码

软件:VIVADO

语言:Verilog

代码功能:

篮球计时器

1、篮球24秒倒计时器,按键启动倒计时

2、倒计时可以通过按键控制暂停、继续

3、倒计时结束后LED灯闪烁报警

4、数码管显示倒计时

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

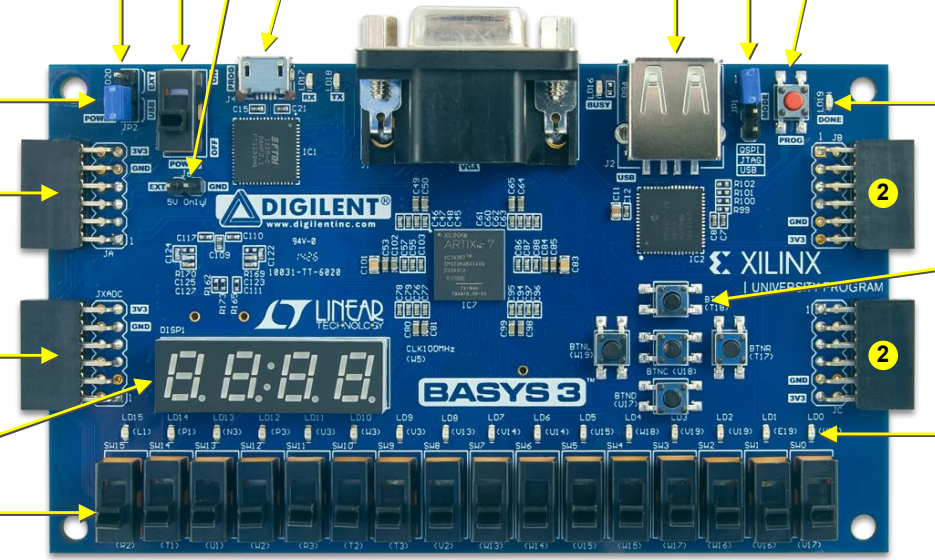

本代码已在Basys3开发板验证,开发板如下,其他开发板可以修改管脚适配:

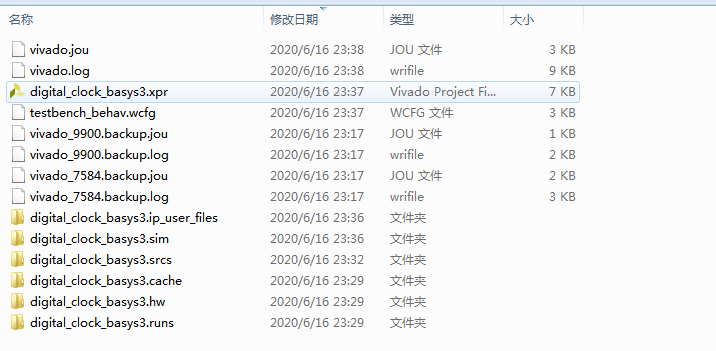

1. 工程文件

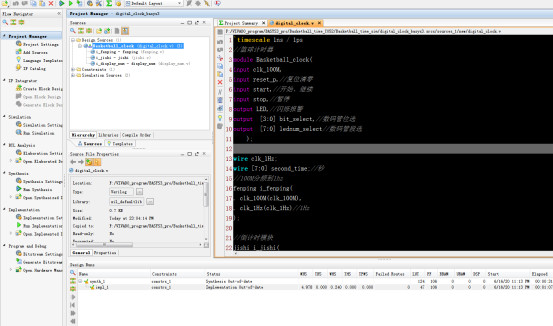

2. 程序文件

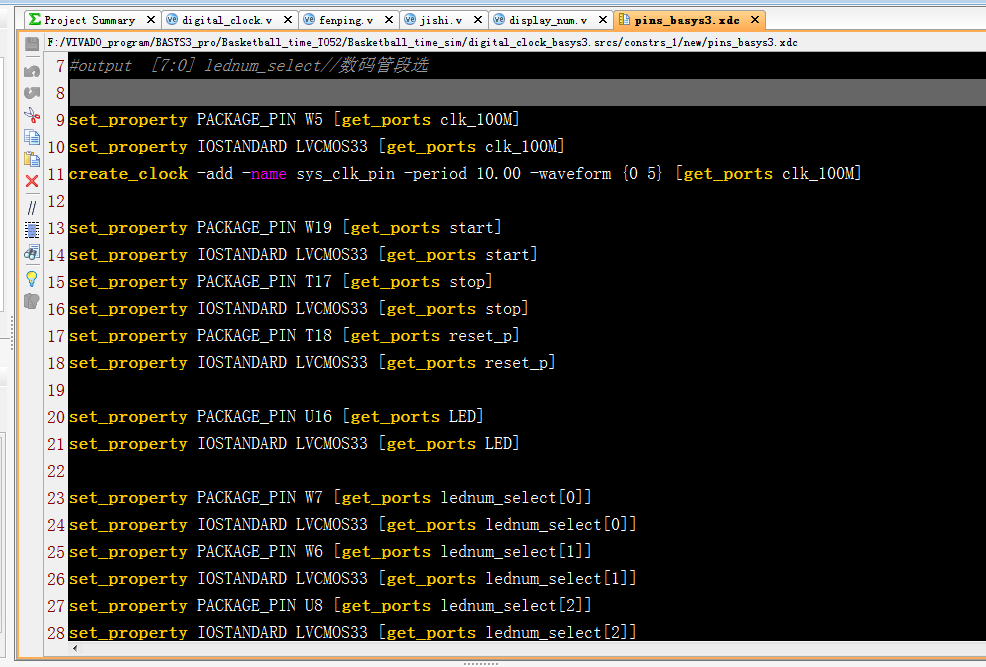

3. 管脚约束文件

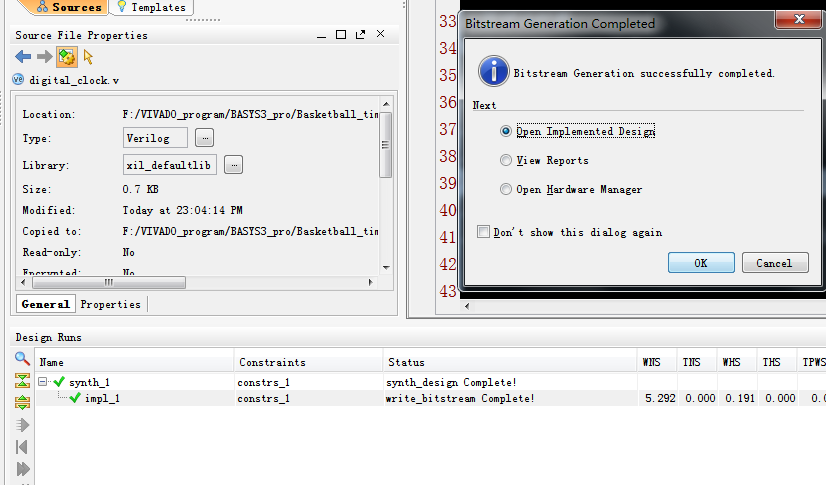

4. 程序编译

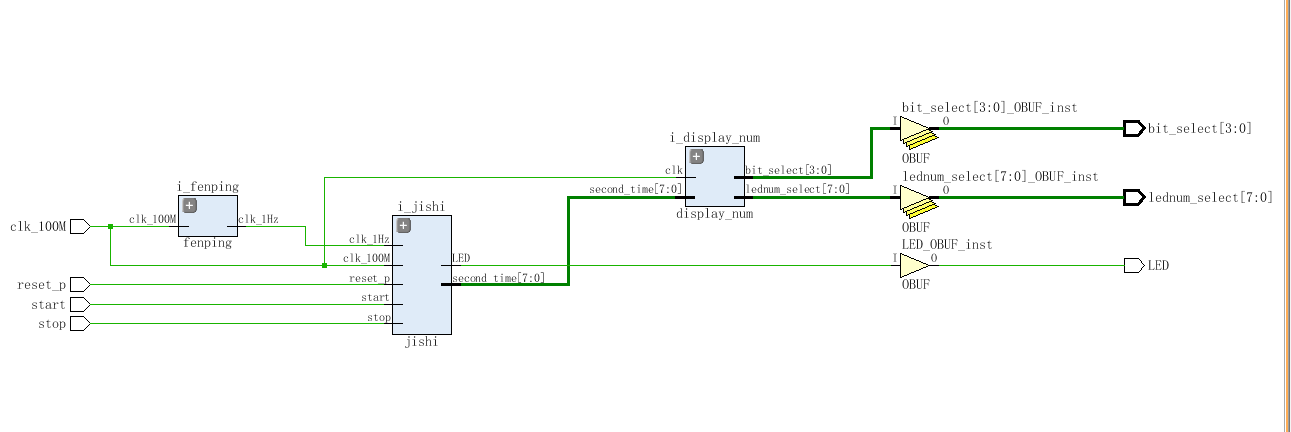

5. RTL图

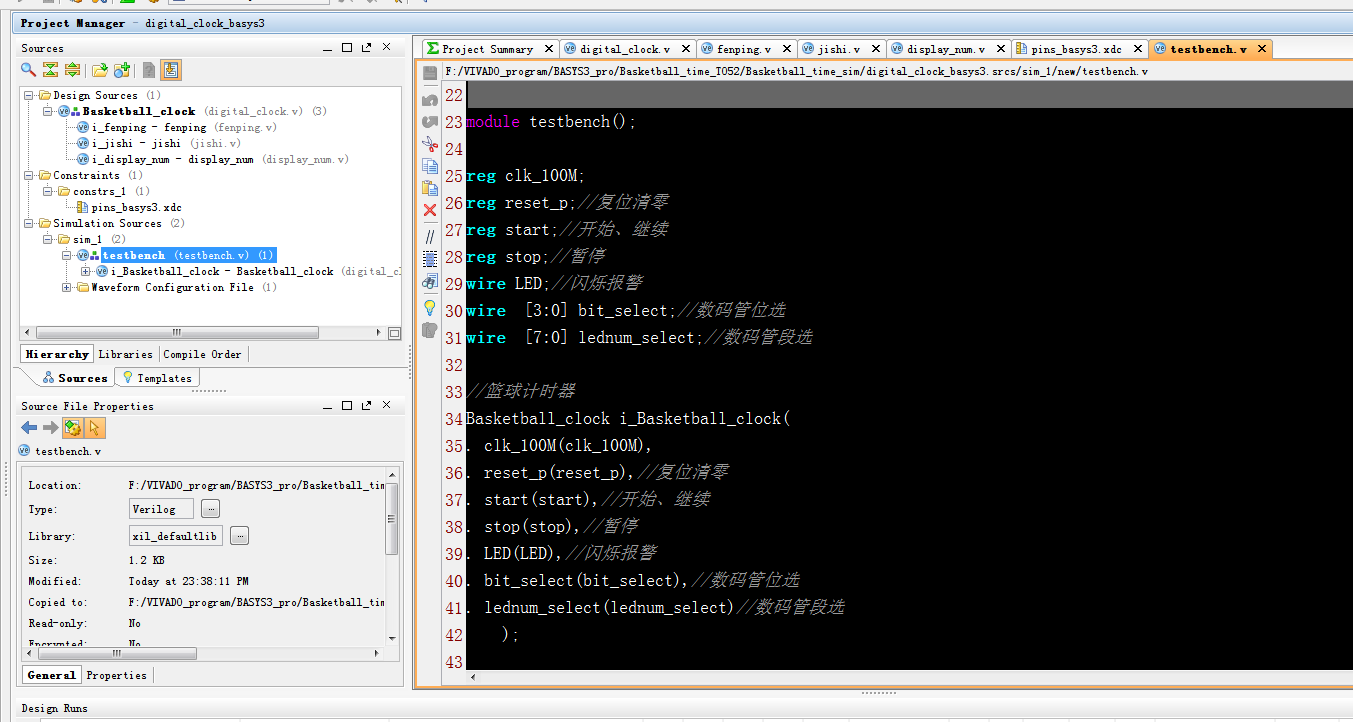

6. Testbench

7. 仿真图

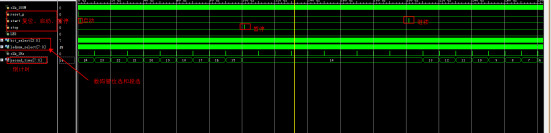

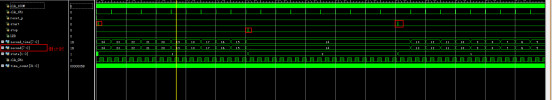

整体仿真图

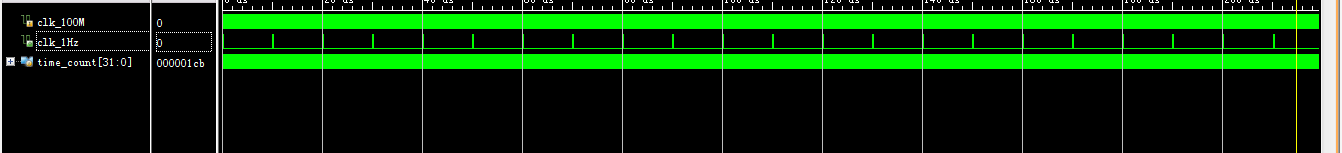

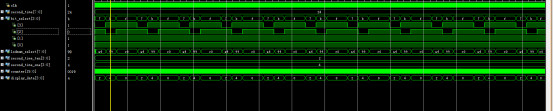

分频模块仿真

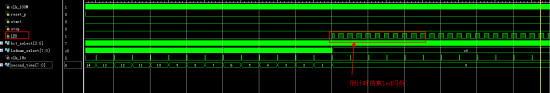

倒计时模块仿真

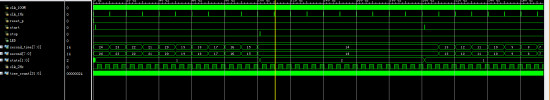

显示模块仿真

部分代码展示:

//倒计时模块 module jishi( input clk_100M, input clk_1Hz,//1Hz信号 input reset_p,//复位清零 input start,//启动、继续 input stop,//暂停 output reg LED,//闪烁报警 output [7:0] second_time//秒 ); reg [7:0] second=8'd24;//秒 parameter s_idle=2'd0;//空闲状态 parameter s_down_cnt=2'd1;//倒计时状态 parameter s_stop=2'd2;//暂停状态 parameter s_end=2'd3;//结束状态 reg [1:0] state=s_idle;//默认正常计时状态 always@(posedge clk_100M or posedge reset_p) if(reset_p) state<=s_idle;//空闲状态 else case(state) s_idle://空闲状态 if(start)//启动、继续按键按下 state<=s_down_cnt; else state<=s_idle; s_down_cnt://倒计时状态 if(second==8'd0) state<=s_end; else if(stop)//暂停键按下,进入暂停状态 state<=s_stop; else state<=s_down_cnt; s_stop://暂停状态 if(start)//启动、继续按键按下 state<=s_down_cnt; else state<=s_stop; s_end://结束 state<=s_end; default:; endcase //产生2Hz闪烁时钟 reg clk_2Hz=0; reg [31:0] time_count=32'd0; always@(posedge clk_100M) if(time_count==32'd25000000)begin//100Mhz计数25000000 time_count<=32'd0; clk_2Hz<=~clk_2Hz;//输出2Hz end else begin time_count<=time_count+32'd1;//计数 clk_2Hz<=clk_2Hz;//输出2Hz end always@(posedge clk_100M or posedge reset_p) if(reset_p) second<=8'd24;//复位到24秒 else if(state==s_down_cnt && clk_1Hz)//倒计时状态 if(second==8'd0) second<=8'd0; else second<=second-8'd1;//倒计时 else second<=second; always@(posedge clk_100M or posedge reset_p) if(reset_p) LED<=0;//复位 else if(state==s_end)结束 LED<=clk_2Hz;//闪烁 else LED<=0; //输出秒 assign second_time=second; endmodule

4737

4737

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?