各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们说到了Datasheet里的内容不用全文通读,应该有选择的查看,如引脚功能、电气参数、典型电路及封装大小。今天我们来讲一讲PCB设计中的蛇形走线。

PCB设计与信号完整性

作者认为在信号完整性分析中,大部分是单端信号的信号完整性问题,其中信号的反射是影响信号完整性的一个重要因素。因此,解决信号的反射问题,就解决了大部分的信号完整性问题。

根据反射机理,信号的反射是由于阻抗不连续引起,那么我们在PCB设计时,需要保证走线的宽度、走线的参考平面、走线距离参考平面的距离一致,保证信号从发送端到接收端的路径都保持一致的阻抗特性。

另一个影响信号完整性的因素是串扰。串扰是多个网络之间信号的相互耦合造成的,最有效、最直接的方法是加大信号间距。设计PCB时要注意区分线距是2根PCB走线内侧边缘的距离还是走线的中心间距。

PCB走线信号时序

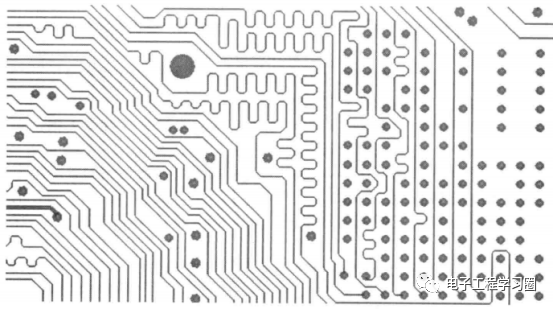

PCB通过走线来调整彼此的时序,在对时序有要求的系统设计中,采用蛇形进行走线延时。如下图所示:

PCB中的蛇形走线

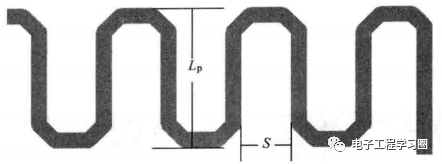

蛇形走线可以改变传输延时,但是会破坏信号质量。影响蛇形线信号传输最关键的两个参数就是耦合长度Lp和耦合距离S,如下图所示:

蛇形走线的耦合长度和耦合距离

信号在蛇形走线上传输时,相互平行的线段之间会发生耦合,呈差模形式,S越小,Lp越大,耦合程度也越大,降低信号的质量。

蛇形走线注意事项

1.尽量增加平行线段的距离S,至少大于3H,H指信号走线到参考平面的距离,说白了就是走线要绕大弯走线。

2.减小耦合长度Lp

3.采用带状线或埋式微带线的蛇形线,它们产生的信号传输延迟较小。

4.高速线尽量不要走蛇形线,尤其避免小范围内蜿蜒走线。

5.空间允许的情况下,可采用任意角度的蛇形走线,能有效减少相互间的耦合。

6.高速PCB设计中,蛇形线没有滤波或抗干扰能力,只用做时序匹配。

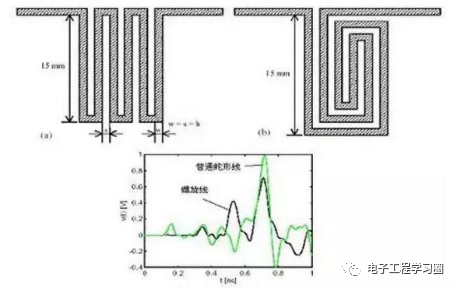

7.有时可考虑螺旋走线的方式进行绕线,效果更好

螺旋走线和普通蛇形线的比较

8.蛇形走线的转角采用45°转角或圆形转角。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

关注同名公众号领取资料~

链接也可在往期文章中找(在文章的最后有链接)~

6980

6980

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?