Verilog生成矩阵一般是使用shift_ip核,但其实用两个FIFO也行。最近刚好学到这种方法,把原理总结一下。

要求

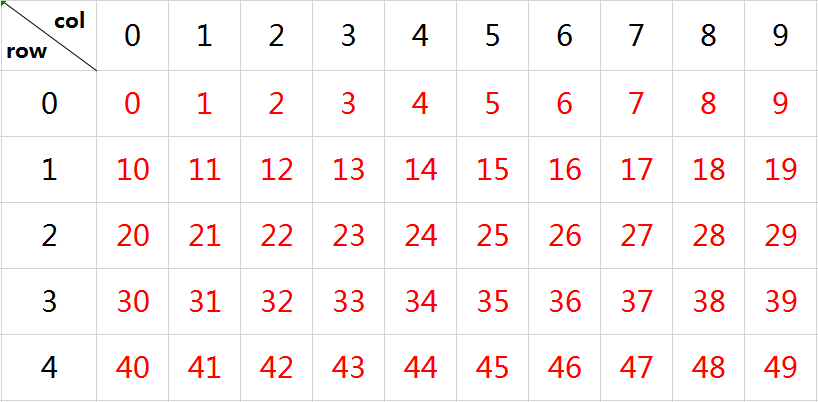

现在有10x5的数据和对应数据有效指示信号,数据为0~49,要用FPGA对其生成3x3矩阵,以便后面进行一些矩阵运算。

第一步,计数器行列规划

首先想到是计数,数据每来一个,cnt_col 就计1下,cnt_col 计满10下时再用cnt_row 计一下,cnt_row 共计5下,这样数据就变成了10x5,如下图所示:

第二步,FIFO形成三行数据

用两个FIFO进行将数据进行缓存。数据来的时候FIFO_1就直接写入,最后两行则不写。来第二行数据的时候FIFO_2就写入,最后一行则不写。这里的行就是用到第一步的计数了。FIFO_1和FIFO_2共用读使能,来第三行数据时就一起读,这时第三行数据来了,配合FIFO_1和FIFO_2读出来的数据,刚好形成时序对齐的3行数据。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5700

5700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?