USB3.0接口系列:

USB3.0接口——(1)基础知识

USB3.0接口——(2)数据结构

USB3.0接口——(3)协议层(包格式)

USB3.0接口——(4)生产消费者模型

USB3.0接口——(5)Host数据传输模型

USB3.0接口——(6)Device数据传输模型

…

1.数据结构

在 USB 3.0 及更高版本的 xHCI 协议中,“Rings”、“Transfer Request Block (TRB)” 和 “Transfer Descriptor (TD)” 是用于管理 USB 数据传输和事件的重要概念。

1.1.Rings

Rings是指一种数据结构,用于组织和管理 USB 数据传输和事件。在 xHCI 协议中,存在多个Rings,每个 Ring 用于特定类型的数据传输或事件。

Ring是数据结构的循环队列。——>TRB Ring定义了一个队列,该队列用于在生产者(Producer)实体和消费者(Consumer)实体之间传输工作项目。

注意: Command和Event TRBs并不支持Chain bit(CH),因此所有的Command Descriptors (CDs)和Event Descriptor (EDs)只有单个TRB构成。

注意: TRB Ring可能大于page,但是它们不得越过64K字节边界。 由于主机控制器可支持255个USB设备,每个设备最多可以声明31个端点,31个端点中的30个可以声明多达64K个流,这意味着单个xHC可能存在大约500M个 Transfer Ring。

1.1.1命令环(Command Ring)

用于xHC(eXtensible Host Controller,可扩展主机控制器)的一种循环队列,使系统软件能够发出命令以枚举USB设备,配置xHC以支持这些设备以及协调虚拟化功能。

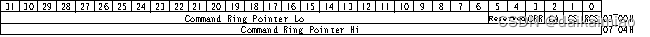

1.1.1.1.CRCR

Command Ring Control Register,命令环控制寄存器。

Command Ring为系统软件提供发送命令来枚举USB设备,配置xHCI支持设备,以及协调虚拟化功能的能力。Command Ring由Operational register中的Command Ring Control Register来支持。

1.1.2.传输环(Transfer Ring)

每个端点或流的一种命令循环队列,提供了与USB设备之间的数据传输。

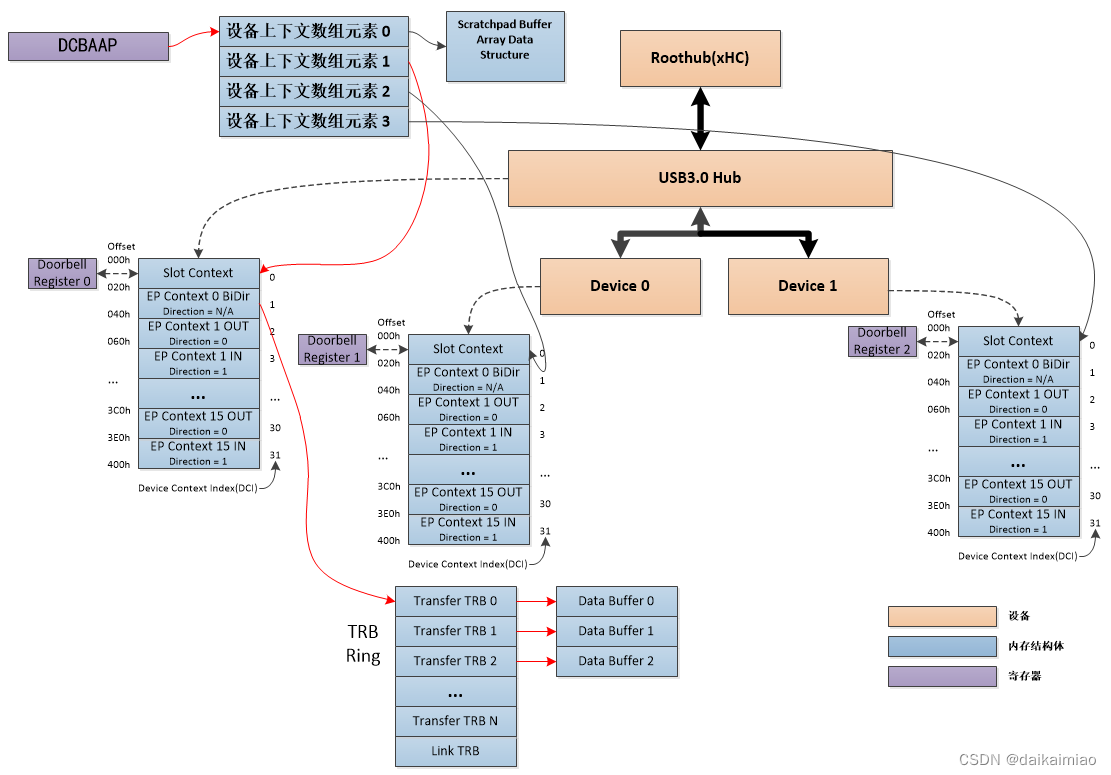

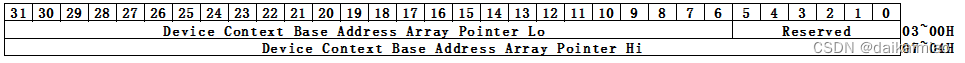

1.1.2.1.DCBAAP

DCBAAP,设备上下文及地址数组指针寄存器。

xhci里面的Operational 寄存器组里面的设备上下文基地址数组指针寄存器(Device Context Base Address Array Pointer Register,DCBAAP),用于保存设备上下文基地址数组(DCBAA)的指针(也就是这个数组的首地址)。

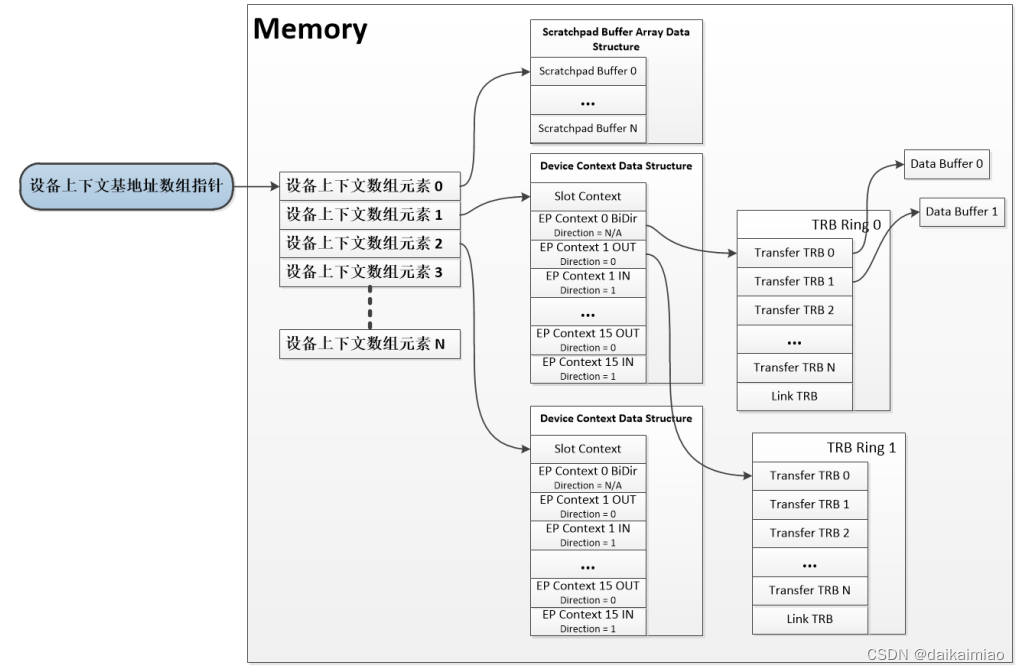

1.1.2.1.1.DCBAA

DCBAA,设备上下文基地址数组,内存数据结构。

DCBAA数组里的每个元素都是指针,指向设备上下文数据结构的基地址。(设备上下文数据结构也是数组)

DCBAA和xHCI的设备槽(Device Slot)相关联,一个Slot对应DCBAA里面的一个条目,可以通过Slot ID来索引对应的设备上下文(Device Context)数据结构,也就是可以将DCBAA看为是一个查找表。

在初始化xHCI时每个条目都会初始化为0。注意DCBAA的首个条目(Slot ID=0)是被xHCI的暂存机制(xHCI Scratchpad Mechanism)使用的。

并且设备上下文基地址数组的首地址,在xHCI被设置为“run”模式(也就是USBCMD寄存器的R/S bit位置1)之前,应该被写入到DCBAAP寄存器中,同时Scratchpad Buffer Array的首地址也要在此之前放入到设备上下文及地址数组的第0个条目。

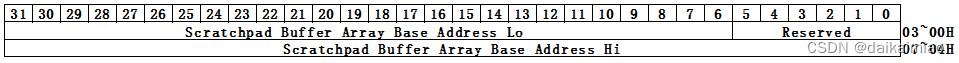

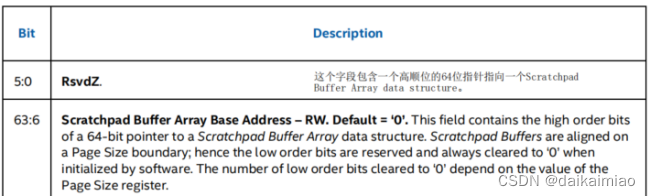

设备上下文基地址数组元素0的位定义:

Scratchpad缓冲区是系统内存的PAGESIZE块,xHCI用来存储其内部状态。xHCI可以请求0到1024个缓冲区。所需的缓冲区数量在HCSPARAMS1寄存器中给出。每个缓冲区是一个与PAGESIZE边界对齐的PAGESIZE块(Page Size一般是4KByte,整个Scratchpad缓冲区大小为N*4KByteÿ

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

737

737

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?