差分信号

差分信号的定义

- 所谓差分信号,即使用两个物理量之间的数值差异来表示一个信号。从严格意义上来讲,所有电压信号都是差分的,因为一个电压只能是相对于另一个电压而言的。

- 如果在一个电路系统中,将系统的"地"作为系统电压的基准点。若使用某一条传输线相较系统电压基准点的电压差表示待传输的信号,我们称这个信号为单端信号。若我们使用某一对传输线之间的电压差用于表示待传输信号,则我们称该型号为差分信号。

差分信号的优点

- 差分信号的第一个好处是,因为你在控制‘基准’电压,所以能够很容易地识别小信号。在一个地做基准,单端信号方案的系统里,测量信号的精确值依赖系统内‘地’的一致性。信号源和信号接收器距离越远,他们局部地的电压值之间有差异的可能性就越大。从差分信号恢复的信号值在很大程度上与‘地’的精确值无关,而在某一范围内。

- 差分信号的第二个主要好处是,它对外部电磁干扰(EMI)是高度免疫的。一个干扰源几乎相同程度地影响差分信号对的每一端。既然电压差异决定信号值,这样将忽视在两个导体上出现的任何同样干扰。除了对干扰不大灵敏外,差分信号比单端信号生成的 EMI 还要少。

- 差分信号提供的第三个好处是,在一个单电源系统,能够从容精确地处理‘双极’信号。为了处理单端,单电源系统的双极信号,我们必须在地和电源干线之间某任意电压处(通常是中点)建立一个虚地。用高于虚地的电压来表示正极信号,低于虚地的电压来表示负极信号。接下来,必须把虚地正确地分布到整个系统里。而对于差分信号,不需要这样一个虚地,这就使我们处理和传播双极信号有一个高逼真度,而无须依赖虚地的稳定性。

差分晶振

差分晶振的定义

- 所谓差分晶振,顾名思义,就是输出是差分信号的晶振。差分晶振是指输出差分信号的晶振,通过使用2种相位彼此完全相反的信号,从而消除了共模噪声,从而实现一个更高性能的系统。

差分晶振的选择

- 选择差分晶振,首先要确认好频率,然后是电压,时钟逻辑类型,封装体积,工作温度以及频率稳定度(精度ppm)。

- 目前常用的时钟逻辑类型有LVDS,LVPECL,HCSL,CML四种类型。

- 目前市场主流差分晶振都是6脚贴片封装,常见的尺寸有7050(7.0*5.0mm),5032(5.0*3.2mm) ,3225(3.2*2.5mm)

差分晶振信号模式

- 时钟逻辑类型有LVDS,LVPECL,HCSL,CML四种类型,每种逻辑类型具有不同的共模电压和摆幅电平。

| 规格 | LVPECL | LVDS | CML | HCSL |

| VCM | VCC-1.4V | 1.2V | VCC-0.2V | 350mV |

| VSWING_SE | 800mV | 325mV | 400mV | 700mV |

| VOH | VCC-1V | 1.3625V | VCC | 700mV |

| VOL | VCC-1.8V | 1.0375V | VCC-0.400V | 0V |

| Reference | VCC | Ground | VCC | Ground |

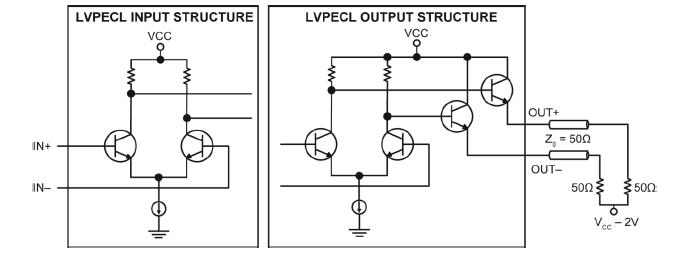

低压,正参考,发射极耦合逻辑(LVPECL)

- 低压,正参考,射极耦合逻辑(LVPECL)源自发射极耦合逻辑(ECL),采用正电源。LVPECL输入是具有高输入阻抗的电流开关差分对。输入共模电压应约为Vcc-1.3V,用于具有内部自偏置或外部偏置的工作余量。

- LVPECL输出由差分对放大器组成,驱动一对射极跟随器(或开放发射器)。输出射极跟随器应在“有效”区域内工作,始终具有直流电流。OUT +的输出引脚 和OUT-通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω)用于阻抗匹配,LVPECL输出的正确终端为50Ω至Vcc-2V和OUT + / OUT-通常为Vcc-1.3V,导致近似的直流电流为14mA。

- 另一种LVPECL输出终止的方法是提供142Ω电阻到GND,为LVPECL输出提供直流偏置,并为GND提供直流电流路径。由于LVPECL输出共模电压为Vcc-1.3V,因此直流偏置电阻可以通过假设直流电流为14mA(R=Vcc-1.3V/14mA)来选择,导致Vcc-3.3V的R=142Ω(150Ω也可以工作)。

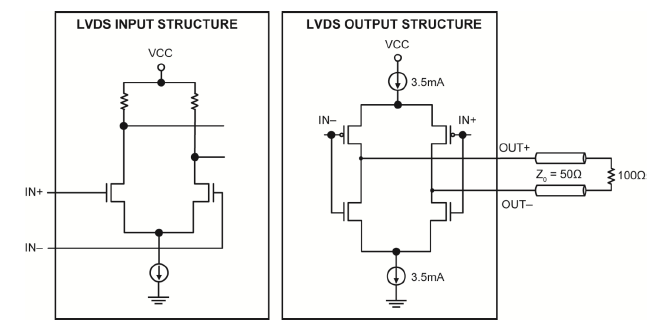

低压差分信号(LVDS)

- 低压差分信号(LVDS)输入需要在IN +和IN-引脚之间连接一个100Ω的电阻,共模电压约为1.2V。如果片内不包含100Ω的端接电阻,则必须包含在印刷电路板(PCB)上。

- LVDS输出驱动器由3.5mA电流源组成,通过开关网络连接到差分输出OUT +和OUT-的输出引脚通常连接到差分传输线(Z0=100Ω)或单端传输线 (Z0=50Ω)用于阻抗匹配,通过接收器输入端的100Ω电阻端接导致LVDS逻辑的摆幅为350mV。

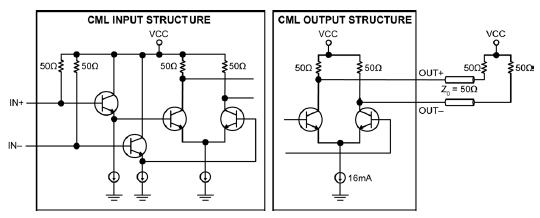

电流模式逻辑(CML)

- 大多数电流模式逻辑(CML)输入结构都有一个50Ω电阻连接到片内Vcc。如果没有,那么必须在PCB的IN +和IN-的两个输入端上施加一个电压。输入晶体管是射极跟随器,驱动差分对放大器。

- CML输出由一对差分共发射极晶体管和50Ω集电极电阻组成。OUT +和OUT-的输出通常连接到差分传输线(Z0=100Ω)或用于阻抗匹配的单端传输线(Z0=50Ω)。通过在共发射极差动BJT中切换电流来提供信号摆幅。假设电流源为16mA(典型值)并且CML输出用一个50Ω电阻上拉到Vcc,这个通过共模电压(Vcc-0.2V),输出电压从Vcc摆动到Vcc-0.4V。

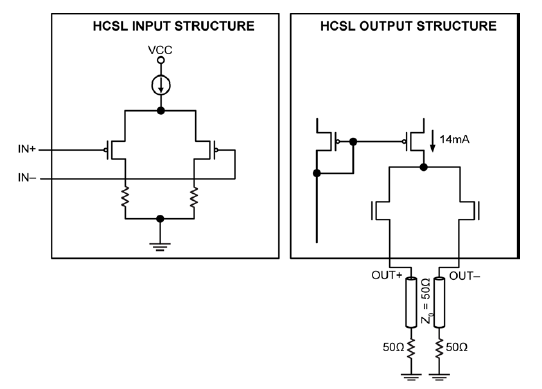

高速电流控制逻辑(HCSL)

- 高速电流控制逻辑(HCSL)输入要求IN +和IN-的两个输入引脚上的单端摆幅为700mV,共模电压约为350mV。

- 典型的HCSL驱动器是具有开源输出的差分逻辑。其中每个输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个输出引脚为高电平(驱动14mA)。OUT+引脚和OUT-引脚通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω),这需要一个外部端接电阻(50Ω到GND),从而为HCSL输入结构提供700mV的摆幅电平。

信号模式转换

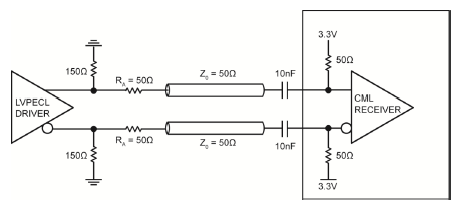

LVPECL到CML的转换

- 如下图所示,在LVPECL驱动器输出端向GND处放置一个150Ω的电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV LVPECL摆幅衰减到400mV的CML摆幅,需在150Ω电阻之后放置一个50Ω的衰减电阻(RA),以衰减LVPECL摆幅电平的一半。另外,必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置50Ω的端接电阻到VCC,用于CML偏置和传输线端接。

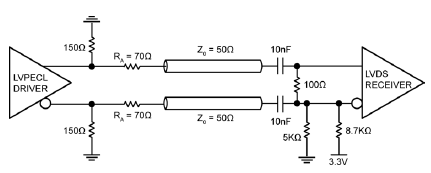

LVPECL到LVDS的转换

- 如下图所示,在LVPECL驱动器输出端向GND放置一个150Ω电阻,对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV LVPECL摆幅衰减到325 mV LVDS摆幅,必须在150Ω电阻器之后放置一个70Ω的衰减电阻。应在LVDS接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。LVDS输入需要重新偏置,可以通过向GND放置8.7KΩ电阻连接到3.3V和5KΩ电阻到GND来实现LVDS接收器输入共模的1.2V直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

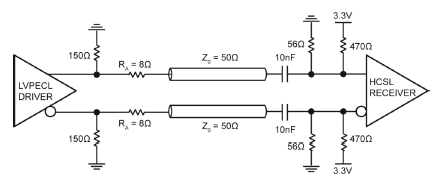

LVPECL到HCSL的转换

- 如下图所示,在LVPECL驱动器输出端向GND放置一个150Ω电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV的LVPECL摆幅衰减到700mV的HCSL摆幅时,必须在150Ω电阻之后放置一个衰减电阻(RA =8Ω)。应在HCSL接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。放置交流耦合电容后,HCSL输入需要重新偏置,可以通过将470Ω电阻连接3.3V和56Ω电阻到GND上来实现HCSL接收机输入共模的350 mV直流电平。

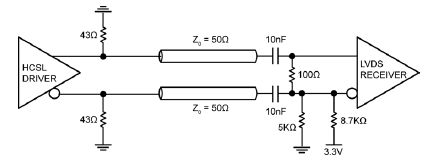

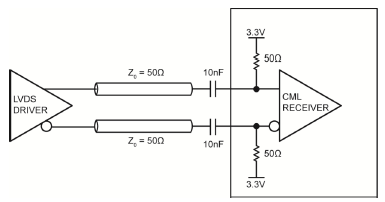

HCSL到LVDS的转换

- 在下图中,每个HCSL输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为48Ω,与50Ω并联,相当于23.11Ω。LVDS输入的摆幅为14mAx23.11Ω= 323mV。应在LVDS接收器前放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。放置交流耦合电容后,LVDS输入需要重新偏置,可以通过将一个8.7KΩ电阻连接到3.3V和5KΩ电阻连接到GND来实现LVDS接收器输入共模的1.2V 直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

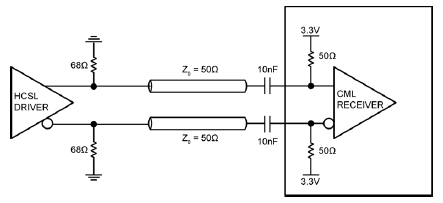

HCSL到CML的转换

- 在下图中,每个HCSL输出引脚在0和14mA之间切换, 当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为68Ω,与50Ω电阻并联,相当于28.81Ω。CML输入的摆幅为14mAx28.81Ω= 403mV。 应在CML接收器前面放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。另外,必须确认CML接收器输入内部的自偏置。如果没有CML输入端的自偏置,则必须在CML偏置和传输线端接的PCB上放置一个50Ω的端接电阻到VCC。

LVDS到CML的转换

- LVDS输出通过100Ω电阻终端驱动±3.5mA电流,在CML接收器前面产生350mV摆幅电平。因为CML的标准摆幅是400mV,所以CML接收器能够接收350mV摆幅电平。此外,还必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置一个50Ω的电阻到VCC,用于CML偏置和传输线端接。

2644

2644

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?