目录

1. 简介

本文是关于《Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)-CSDN博客》的博客文章,涉及了overlay设计的Vivado工程细节。在使用PYNQ调试MIPI驱动之前,需要搭建一些基本的IP核。这个过程并不复杂,因为Xilinx已经提供了相当完善的IP核体系。

Vivado 对应版本:2022.1

摄像头型号:Digilent Pcam 5C

开发板型号:KV260

2. Overlay 设计

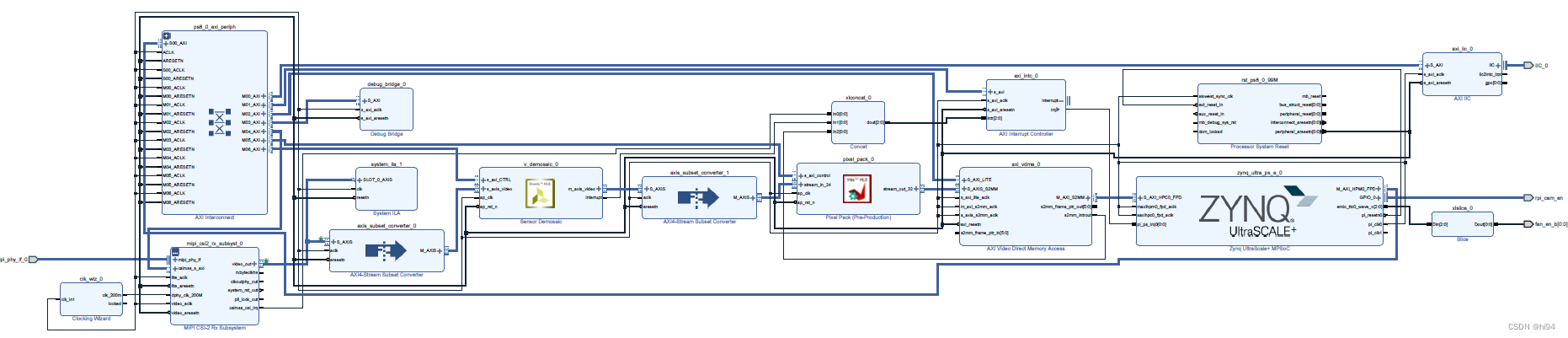

2.1 总体设计

本文提供了附带PDF文件,请参阅附件资源。文章通过一个简单的工程示例,演示了如何成功运行MIPI驱动的完整链路。

构建完整的工程需要将bit文件和hwh文件一并拷贝至PYNQ环境中,并使用overlay进行加载。

加载过程同样非常简单:

from pynq import Overlay

ol = Overlay("your.bit")关于HWH的解释:

HWH(Hardware Handoff)是硬件托管文件,是一种包含硬件设计详细信息的文件。它由Vivado在生成比特流文件时自动生成。HWH文件采用XML格式,包含设计中使用的IP核、接口、层次结构、时钟、中断等相关信息。

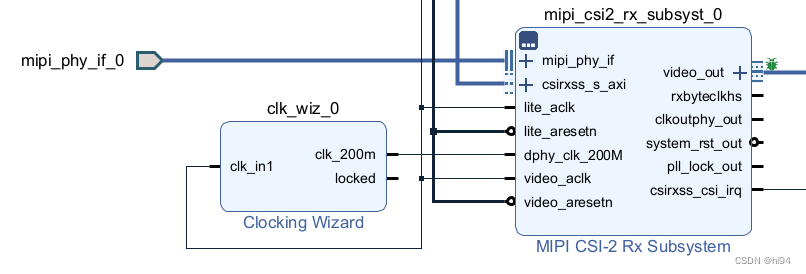

2.2 MIPI 子系统

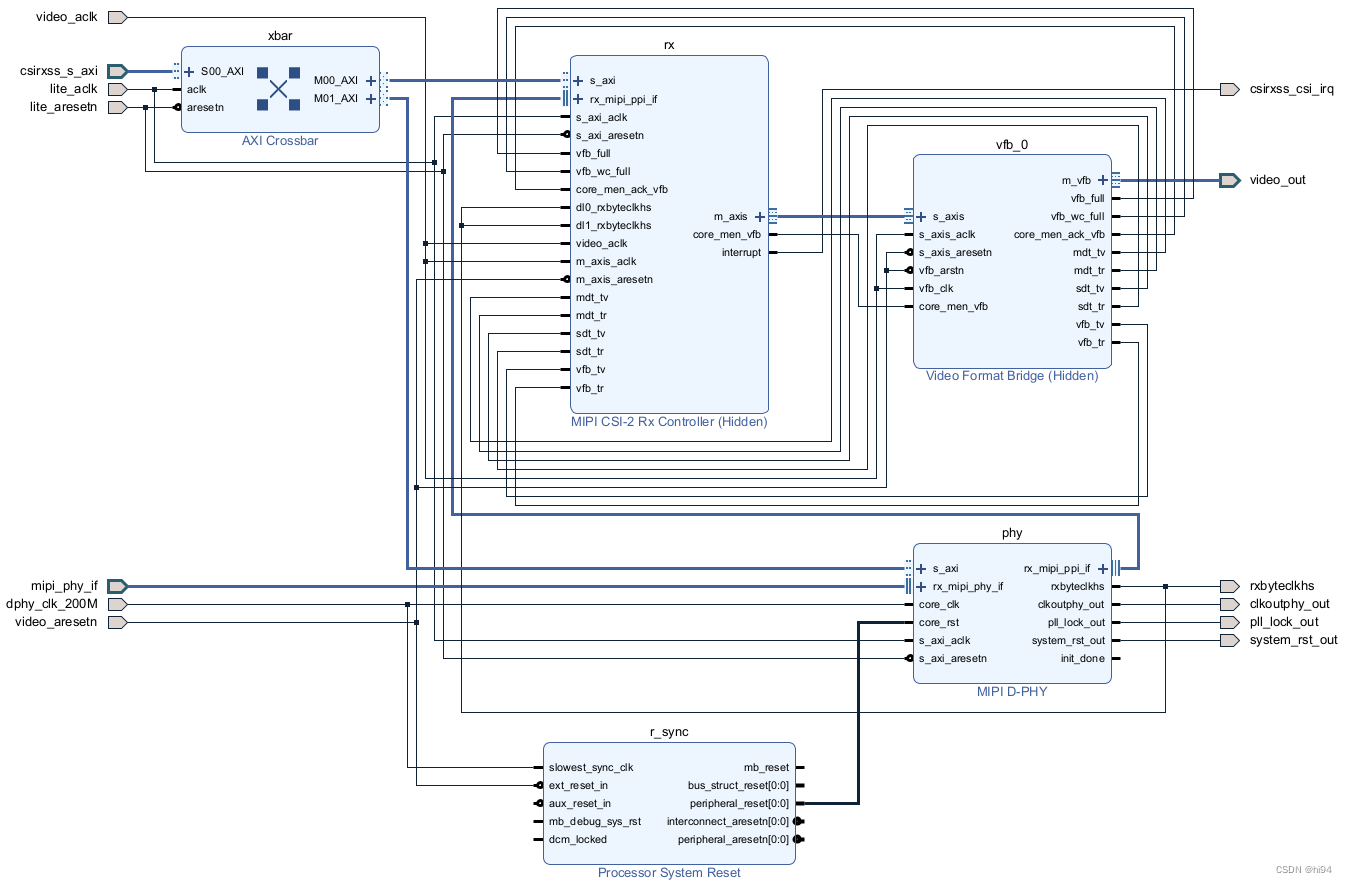

从 Block Design 中IP接口来看,mipi子系统的连接方式非常简单,其实 MIPI CSI-2 Rx Subsystem 是包含三个主要的 IP Core:

从 Block Design 中IP接口来看,mipi子系统的连接方式非常简单,其实 MIPI CSI-2 Rx Subsystem 是包含三个主要的 IP Core:

- MIPI PHY,物理层,负责处理物理层面的MIPI接口,将MIPI协议中的电信号转换为逻辑信号,并将其传递给接收端。

- MIPI CSI-2 Rx Controller,CSI-2 接收控制器,是MIPI CSI-2接收子系统的核心部分。它接收来自MIPI PHY的数据流,并解析其中的CSI-2协议,提取出图像数据和控制信息。

- Video Format Bridge,视频格式桥接器,将从MIPI CSI-2 Rx Controller接收到的图像数据流转换为特定的视频格式,以便后续的处理或显示。

创建该 IP 的 TCL 命令如下:

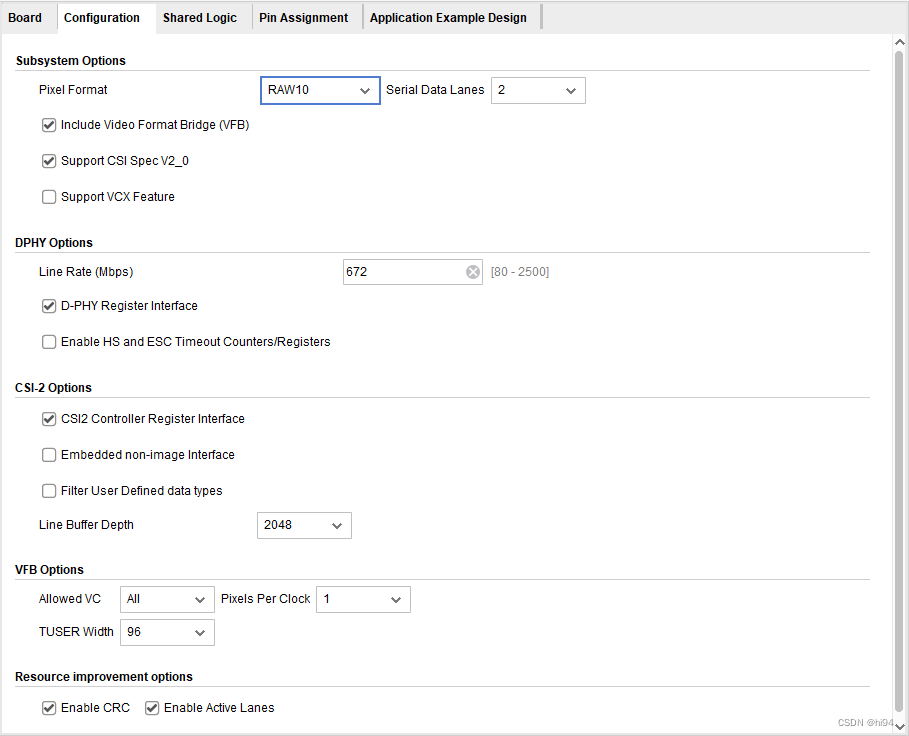

# Create instance: mipi_csi2_rx_subsyst_0, and set properties

set mipi_csi2_rx_subsyst_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:mipi_csi2_rx_subsystem:5.1 mipi_csi2_rx_subsyst_0 ]

set_property -dict [ list \

CONFIG.CLK_LANE_IO_LOC {D7} \

CONFIG.CLK_LANE_IO_LOC_NAME {IO_L13P_T2L_N0_GC_QBC_66} \

CONFIG.CMN_NUM_LANES {2} \

CONFIG.CMN_PXL_FORMAT {RAW10} \

CONFIG.CSI_EMB_NON_IMG {false} \

CONFIG.C_CLK_LANE_IO_POSITION {26} \

CONFIG.C_CSI_EN_ACTIVELANES {true} \

CONFIG.C_CSI_FILTER_USERDATATYPE {false} \

CONFIG.C_DATA_LANE0_IO_POSITION {28} \

CONFIG.C_DATA_LANE1_IO_POSITION {30} \

CONFIG.C_DPHY_LANES {2} \

CONFIG.C_EN_BG0_PIN0 {false} \

CONFIG.C_EN_BG1_PIN0 {false} \

CONFIG.C_EN_CSI_V2_0 {true} \

CONFIG.C_EN_TIMEOUT_REGS {false} \

CONFIG.C_HS_LINE_RATE {672} \

CONFIG.C_HS_SETTLE_NS {149} \

CONFIG.DATA_LANE0_IO_LOC {E5} \

CONFIG.DATA_LANE0_IO_LOC_NAME {IO_L14P_T2L_N2_GC_66} \

CONFIG.DATA_LANE1_IO_LOC {G6} \

CONFIG.DATA_LANE1_IO_LOC_NAME {IO_L15P_T2L_N4_AD11P_66} \

CONFIG.DPHYRX_BOARD_INTERFACE {som240_1_connector_mipi_csi_raspi} \

CONFIG.DPY_EN_REG_IF {true} \

CONFIG.DPY_LINE_RATE {672} \

CONFIG.HP_IO_BANK_SELECTION {66} \

CONFIG.SupportLevel {1} \

CONFIG.VFB_TU_WIDTH {96} \

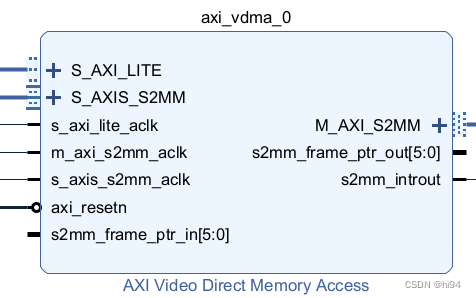

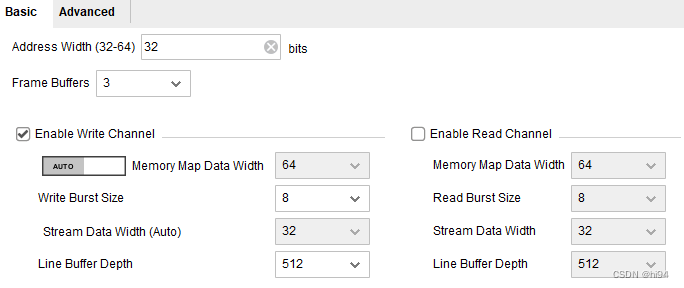

] $mipi_csi2_rx_subsyst_02.3 VDMA

# Create instance: axi_vdma_0, and set properties

set axi_vdma_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_vdma:6.3 axi_vdma_0 ]

set_property -dict [ list \

CONFIG.c_include_mm2s {0} \

CONFIG.c_mm2s_genlock_mode {0} \

] $axi_vdma_0该 VDMA IP Core 只启用了 Write Channel,因为只涉及到将 OV5640 的图像传入 PS-DDR,然后通过 iPython 直接显示:

frame_camera = cam_vdma.readchannel.readframe()

frame_color=cv2.cvtColor(frame_camera,cv2.COLOR_BGR2RGB)

pixels = np.array(frame_color)

plt.imshow(pixels)

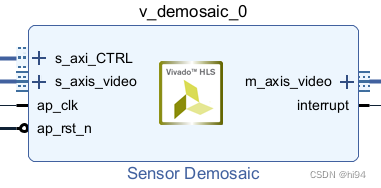

plt.show()2.4 去马赛克

去马赛克模块的驱动如下:

WIDTH = 1280

HEIGHT = 720

demo = ol.v_demosaic_0

demo.write(0x10,WIDTH)

demo.write(0x18,HEIGHT)

demo.write(0x28,0x03)

demo.write(0x00,0x81)OV5640摄像头是包含去马赛克功能的,本文并没有使用,因为后续文中会在此基础上,添加图像处理 IP Cores。本文的重点也是放在 MIPI 驱动上。

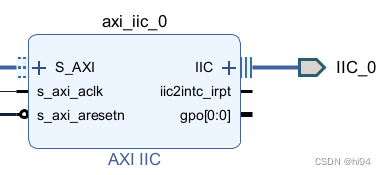

2.5 AXI_IIC

# Create instance: axi_iic_0, and set properties

set axi_iic_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:axi_iic:2.1 axi_iic_0 ]

set_property -dict [ list \

CONFIG.IIC_BOARD_INTERFACE {som240_1_connector_hda_iic_switch} \

CONFIG.IIC_FREQ_KHZ {400} \

] $axi_iic_0按照 TCL 代码调用 AXI IIC IP Core 即可,需要设置的参数很少。

3. 注意事项

- IIC接口速度需要设置为 400 kHz,如果使用默认 100 kHz,会出现操作IIC接口卡死的情况。

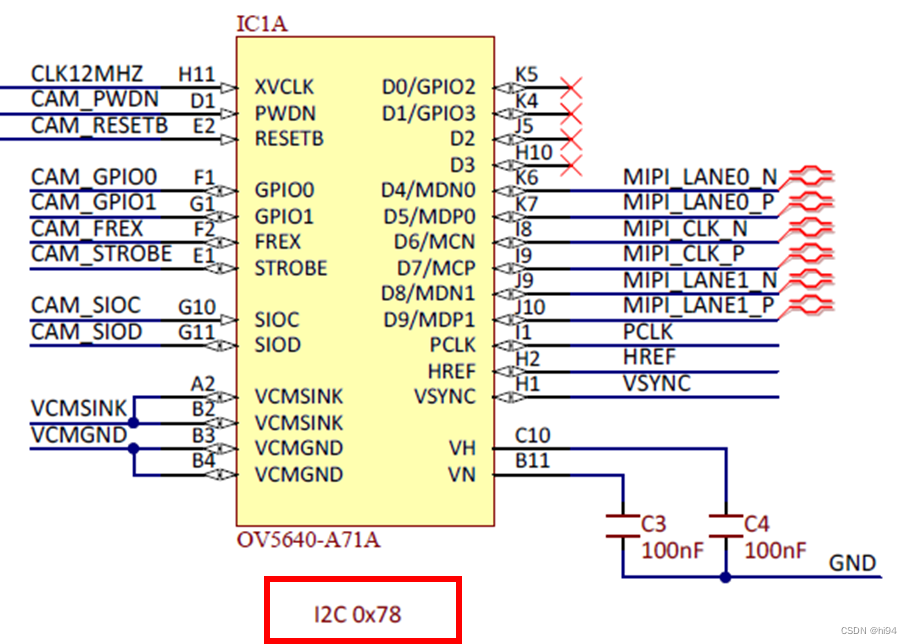

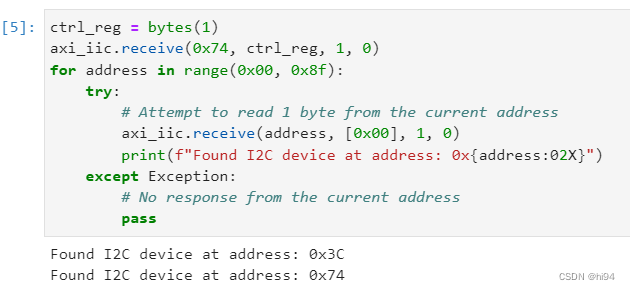

- 在摄像头原理图中《pcam_5c_sch.pdf》,提到传感器的地址为0x78,但实际中使用IIC扫描硬件设备时发现地址是0x3C。这似乎存在一些混淆,但实际上并不矛盾。0x78是一个包含读写位的地址,而0x3C则是去除了读写位后的地址。因此,0v5640的地址应当是0x78/0x79,其中0x78是写入地址,而0x79是读取地址。

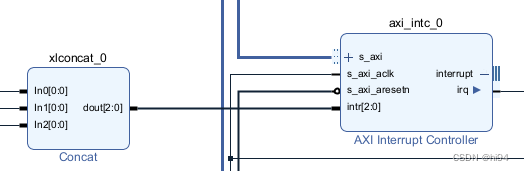

- 中断控制器的连接方式很重要,即使没有用到中断,不然 PYNQ 会报告无法找到中断。通常的做法使用 Concat 将几个中断合并,然后使用 AXI Interrupt Controller 将其连接到 Zynq 的中断输入。

4. 总结

本文分享了如何利用PYNQ快速入门摄像头MIPI驱动(OV5640)的过程。通过Vivado设计的overlay,演示了MIPI驱动的完整链路。文章着重介绍了MIPI子系统的构建,包括MIPI PHY、MIPI CSI-2 Rx Controller和Video Format Bridge的设置。另外,还介绍了去马赛克模块的驱动和AXI_IIC的配置。文章指出了一些注意事项,如IIC接口速度的设置、传感器地址的解释以及中断控制器的连接方式。

4022

4022

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?